2. 中国人民解放军91033部队,山东 青岛 266071

2. Unit 91033, PLA, Qingdao 266071, China

移动通信系统具有可靠和高效的特点,对于具有时变特性的无线信道,需要能在不同信道条件下进行可靠数据传输的传输方案。低密度奇偶校验(low density parity check, LDPC)码是一种能够逼近香农信道容量极限的信道编码[1],已经被广泛应用于卫星电视通信[2]、移动无线通信[3]、无线局域网[4]等领域中。空间耦合LDPC(SC-LDPC)码是一种源于LDPC卷积码的新型信道编码[5],理论上被证明可以达到一般二元无记忆对称信道的信道容量[6]。相比于LDPC码,空间耦合LDPC码在特殊的耦合结构下具有优异的性能,在B5G/6G移动通信系统中具有广阔的应用前景。码率兼容LDPC码是指一组信息位长度相同、码率不同的LDPC码,该组LDPC码在不同的码率下都有较好的性能,并能够使用同一套编译码器实现[7]。文献[8]通过对特殊的三边型LDPC校验矩阵进行扩展和组合,实现码率兼容空间耦合LDPC码,理论上可以实现任意码率,但对校验矩阵要求较高,在给定的短耦合长度下性能并不理想。文献[9]通过修改LDPC码的校验矩阵结构,在耦合边缘处对矩阵的连接进行不同的组合来现码率兼容,可以实现递归编码。文献[10]采用打孔方式,将随机打孔的码率兼容LDPC码进行耦合,耦合长度大时译码性能较好,但由于打孔操作是随机的,具有不确定性,并且长耦合长度对资源的占用较大。文献[11]提出了一种基于重复累加扩展构造LDPC码的方案,并对其进行耦合,通过对校验矩阵的变量节点进行扩展和耦合实现码率兼容,复杂度较高。

针对以上情况,本文设计并实现了一种码率兼容的空间耦合LDPC码方案,并基于FPGA进行验证。通过构造码率兼容的基矩阵进行耦合,实现码率兼容的空间耦合LDPC码。编码器直接使用校验矩阵进行系统编码,译码器采用分层最小和译码算法,在保证性能的同时可以减少FPGA中资源的占用。

1 码率兼容SC-LDPC码校验矩阵构造 1.1 空间耦合LDPC码的结构与编码算法空间耦合LDPC码的矩阵结构为

| ${{H}} = \left[ {\begin{array}{*{20}{c}} {{{{H}}_0}(0)}&{}&{}&{}&{} \\ {{{{H}}_1}(0)}&{{{{H}}_0}(1)}&{}&{}&{} \\ \vdots &{{{{H}}_1}(1)}& \cdots &{}&{} \\ {{{{H}}_m}(0)}& \cdots & \cdots & \cdots &{} \\ {}&{{{{H}}_m}(1)}& \cdots & \cdots &{{{{H}}_0}(t)} \\ {}&{}& \cdots & \cdots &{{{{H}}_1}(t)} \\ {}&{}&{}& \cdots & \vdots \\ {}&{}&{}&{}&{{{{H}}_m}(t)} \end{array}} \right]$ |

式中:空白部分为全零矩阵;

由于空间耦合LDPC码校验矩阵具有耦合关系,对应于

由于空间耦合LDPC的码字

| ${{{v}}_t}{{H}}_0^{\rm{T}}(t) + {{{v}}_{t - 1}}{{H}}_1^{\rm{T}}(t) + \cdots + {{{v}}_{t - m}}{{H}}_m^{\rm{T}}(t) = {\bf{0}}$ | (1) |

式(1)可以变换为

| ${{{v}}_{[0,t - 1]}}{{H}}_{[0,t - 1]}^{\rm{T}} = [{{\bf{0}}_{[0,t - 1]}}|{{{p}}_t}]$ | (2) |

式中:

| ${{{p}}_{t,i}} = \left\{ \begin{array}{l} {{{{p}}_{t - 1,i + 1}} + {{{v}}_{t - 1}}{{H}}_i^{\rm{T}}(t + i - 1),}\quad{i = 1,2, \cdots ,m - 1} \\ {{{{v}}_{t - 1}}{{H}}_m^{\rm{T}}(t + m - 1),}\quad{i = m} \end{array} \right.$ | (3) |

在编码第

| ${{{H}}_0}(t) = [\begin{array}{*{20}{c}} {{{H}}_0^{(0)}(t)}&{{{H}}_0^{(1)}(t)} \end{array}]$ | (4) |

前一部分

| ${{v}}_t^{(0)}{[{{H}}_0^{(0)}(t)]^{\rm{T}}} + {{v}}_t^{(1)}{[{{H}}_0^{(1)}(t)]^{\rm{T}}} = {{{p}}_{t,1}}$ |

令

| ${{v}}_t^{(1)} = {{v}}_t^{(0)}{[{{H}}_0^{(0)}(t)]^{\rm{T}}} + {{{p}}_{t,1}}$ | (5) |

至此,信息位

5G标准中增强移动宽带(enhanced mobile broadband,eMBB)场景下使用的LDPC码,采用类Raptor的扩展型码率兼容矩阵结构,在可以使用校验矩阵进行系统编码的同时实现码率兼容[14],类Raptor型LDPC码校验矩阵结构如图1所示。

|

Download:

|

| 图 1 类Raptor型LDPC码矩阵结构 | |

图中,子矩阵A与子矩阵E是由循环移位矩阵组成的矩阵阵列,子矩阵O为全零矩阵,子矩阵I为单位矩阵。矩阵A对应信息位;矩阵D对应校验位,具有双对角线结构,用于递归编码;核矩阵

令编码的码字矢量

| $\left\{ {\begin{array}{*{20}{l}} {{{{\lambda}} _{_0}} + {{{v}}_0} + {{{v}}_1} = {\bf{0}}} \\ {{{{\lambda}} _1} + {{{v}}_1} + {{{v}}_2} = {\bf{0}}} \\ {{{{\lambda}} _2} + {{v}}_0^1 + {{{v}}_2} + {{{v}}_3} = {\bf{0}}} \\ {{{{\lambda}} _3} + {{{v}}_0} + {{{v}}_3} = {\bf{0}}} \end{array}} \right. \Leftrightarrow \left\{ {\begin{array}{*{20}{l}} {{{{\lambda}} _0} = {{{v}}_0} + {{{v}}_1}} \\ {{{{\lambda}} _1} = {{{v}}_1} + {{{v}}_2}} \\ {{{{\lambda}} _2} = {{v}}_0^1 + {{{v}}_2} + {{{v}}_3}} \\ {{{{\lambda}} _3} = {{{v}}_0} + {{{v}}_3}} \end{array}} \right.$ | (6) |

式中上标代表矩阵的循环移位系数,无上标表示矩阵的循环移位系数为0。由于二元LDPC码的加法为模二加,将式(6)右侧方程等号两边相加,有

| ${{v}}_0^1 = {{{\lambda}} _0} + {{{\lambda}} _1} + {{{\lambda}} _2} + {{{\lambda}} _3}$ | (7) |

通过式(7)可以求出

| ${{{v}}_i} = [{{u}},{{{v}}_0},{{{v}}_1},{{{v}}_1},{{{v}}_3}] \times {{E}}_i^{\rm{T}}$ |

式中

在部分校验子前项编码算法中,式(4)说明了如何利用耦合基矩阵

|

Download:

|

| 图 2 码率兼容基矩阵结构 | |

基矩阵

| ${{H}} = \left[ {\begin{array}{*{20}{c}} {{{{H}}_0}}&{}&{}&{}&{} \\ {{{{H}}_1}}&{{{{H}}_0}}&{}&{}&{} \\ {}&{{{{H}}_1}}& \cdots &{}&{} \\ {}&{}& \cdots & \cdots &{} \\ {}&{}&{}& \cdots &{{{{H}}_0}} \\ {}&{}&{}&{}&{{{{H}}_1}} \end{array}} \right]$ |

式中

利用5G标准中的参数构造对应码率的类Raptor结构校验矩阵,使用BP译码算法与本文设计的SC-LDPC码校验矩阵进行性能仿真对比,在相同信息位长、最大译码迭代次数为20次、不同码率的情况下,误码率性能如图3所示。图中Eb/N0代表归一化信噪比,BER(bit error rate)代表误码率。可以看出本文所构造的码率兼容SC-LDPC码校验矩阵具有更好的译码性能,并且在BER=10−6时没有出现明显的错误平层。

|

Download:

|

| 图 3 误码率性能比较 | |

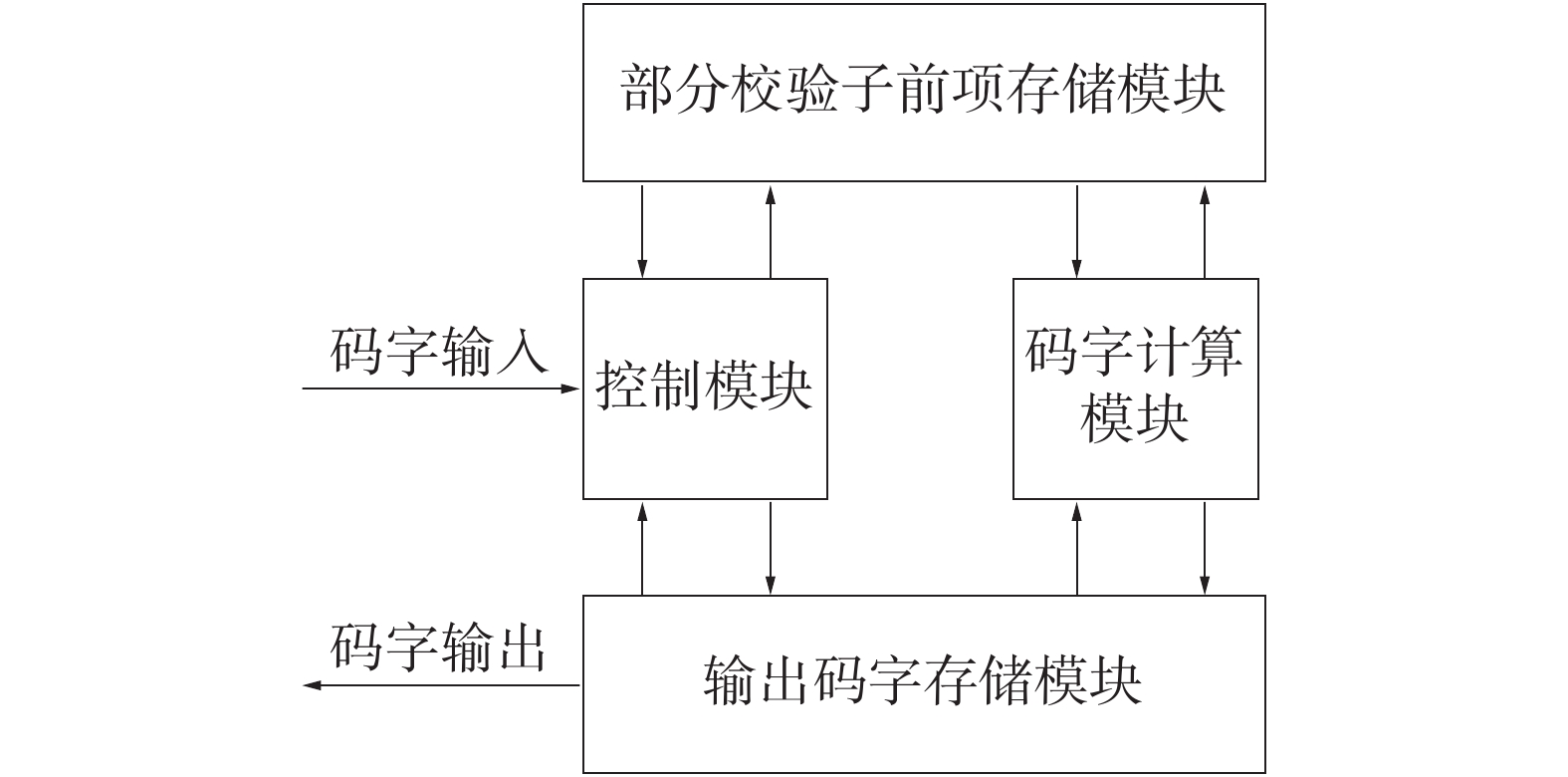

根据部分校验子前项编码算法,编码器主要由控制模块、部分校验子前项存储模块、码字计算模块、输出码字存储模块组成。编码器结构如图4所示。

|

Download:

|

| 图 4 码率兼容空间耦合LDPC码编码器结构 | |

当需要编码的码字信息位输入到编码器时,编码器将输入的信息位存储至寄存器中。当信息位接收完毕,编码器开始进行编码。编码器的核心模块为控制模块和码字计算模块。

控制模块对编码过程进行控制。当码字信息位和码率指示信号输入时,控制模块负责对这些信息进行接收;当信息接收完毕后,控制模块根据码率指示信号,对不同的码率情况进行编码运算。校验矩阵为准循环移位矩阵,输入的信息位与校验矩阵相乘等价于对信息位进行循环移位,因此编码器根据输入的码率控制信号来确定不同循环移位单元的计算使能,实现SC-LDPC码在不同码率下的编码。

码字计算模块的计算过程中主要为2个步骤,分别对应式(5)与式(3)。校验位的计算对应式(5)中校验位

|

Download:

|

| 图 5 编码器码字计算模块时序仿真 | |

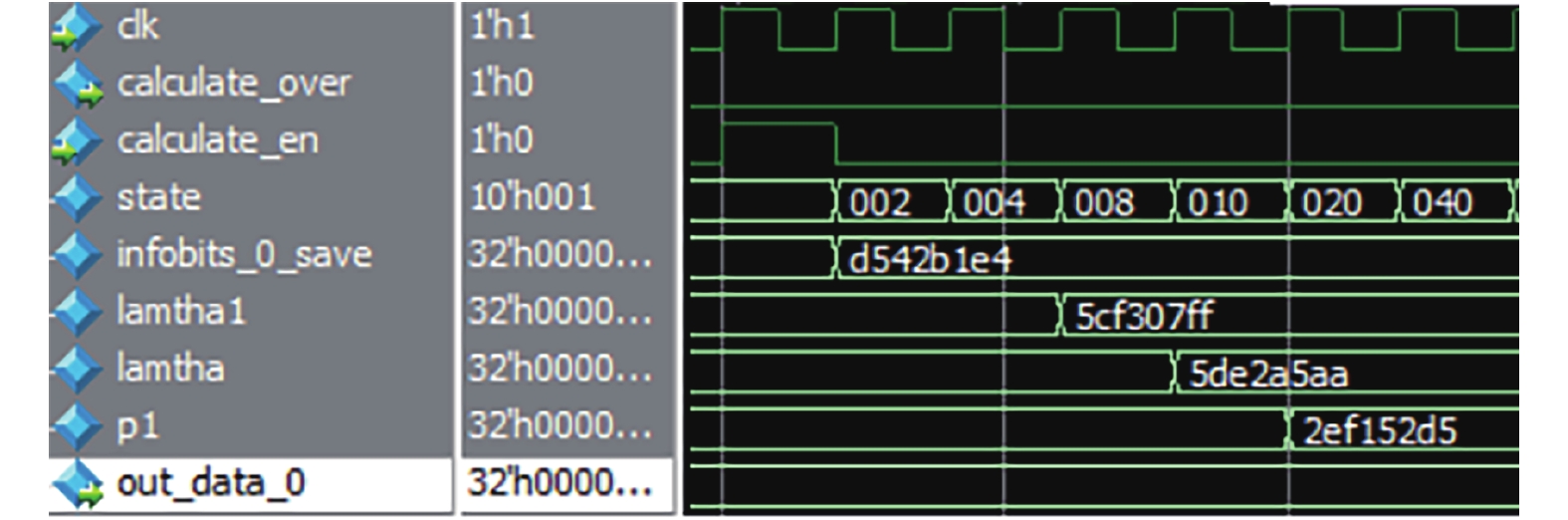

将编码器通过Verilog硬件描述语言实现,使用Modelsim 10.7软件进行时序仿真,如图6所示。在Xilinx xc7k325tff900-2芯片上进行实现,编码器资源占用如表1所示。

|

Download:

|

| 图 6 编码器输出结果时序仿真 | |

|

|

表 1 编码器资源占用表 |

由于编码器主要采用循环移位和异或运算进行编码计算,计算产生的中间数据存储在循环移位寄存器中,只有部分校验子前项需要在运算前进行读取、在编码完毕后需要进行存储,因此需要少量的RAM资源来存储部分校验子前项,编码器整体资源占用较低。

3 码率兼容SC-LDPC码译码器设计 3.1 分层译码算法由于本文构造的SC-LDPC码校验矩阵属于准循环校验矩阵,从硬件实现的角度考虑,分层译码算法是一种十分适用于准循环结构校验矩阵的译码算法。一方面,分层译码将整个校验矩阵分成多个层,优化了层间的消息传递,使迭代译码收敛速度更快;另一方面,分层译码只需要存储校验节点信息,无需存储变量节点信息,减少了资源占用[15]。假设校验矩阵的大小为M×N,将校验矩阵的M个校验方程分为T组,每组包括M/T行,分层译码算法的具体步骤描述如下:

1)初始化。

| $L(Q_{i,1}^{(0)}) = L({c_i}) = {y_i},L(\sigma _{ji,1}^{(0)}) = 0,l = 1,m = 1$ |

式中:

2)校验行分组更新。

①对于校验矩阵中第m层的每个变量节点,先验信息更新如下:

| $L(q_{ij,m}^{(l)}) = L(Q_{i,m}^{(l - 1)}) - L(\sigma _{ji,m}^{(l - 1)})$ |

②基于最小和算法,更新第m层的校验节点消息:

| $L(\sigma _{ji,m}^{(l)}) = \left( {\prod\limits_{i' \in {N_c}(j)\backslash \{ i\} } {{\rm{sign}}\left( {L(q_{i'j,m}^{(l)})} \right)} } \right) \cdot \mathop {\min }\limits_{i'} \left( {\left| {L(q_{i'j,m}^{(l)})} \right|} \right)$ |

③校验节点消息更新。在第l次译码迭代过程中,当第m层的校验节点消息更新后,立即计算与之相连的变量节点消息,后验概率消息更新方程为

| $L(Q_{i,m}^{(l)}) = L(q_{ij,m}^{(l)}) + L(\sigma _{ji,m}^{(l)})$ |

④译码判决。若

3)若伴随式

4)若

在SC-LDPC码的其他译码方案中,文献[16]提出了一种针对SC-LDPC码的特殊结构——修改优化变量节点信息传递规则的译码方式,充分利用变量节点信息进行更新运算;文献[17]提出了一种利用译码后验概率信息进行节点更新的译码方式,增加了可靠性。在信息位长192 bit,码率为1/2,译码迭代次数为20次的情况下,文献[16]、[17]以及本文提出的分层译码与BP译码算法性能如图7所示。

可以看出,本文采用的分层译码方式与文献[16]及[17]提出的译码算法相比,在短信息位长时译码性能较好,没有明显的错误平层,并且与BP译码算法的性能接近;在硬件实现中,可以将变量节点更新单元和校验节点更新单元合并,不需要存储变量节点更新信息,节省硬件存储资源占用。因此,选择分层译码算法作为本文设计的SC-LDPC码的译码算法方案。

|

Download:

|

| 图 7 本文译码方法与其他文献译码方法性能仿真对比 | |

根据分层最小和译码算法方案,结合SC-LDPC校验矩阵,采用分层译码方式,译码器输入数据采用6 bit量化,最高位为符号位,中间3位是整数位,最后2位为小数位。译码器结构如图8所示。

|

Download:

|

| 图 8 码率兼容空间耦合LDPC码译码器结构 | |

译码器主要由矩阵参数控制模块、码字似然比初始化模块、译码迭代控制模块、节点更新计算模块、校验节点概率信息存储模块、后验概率信息存储模块组成。其中,码字似然比初始化模块、校验节点概率信息存储模块与节点后验概率信息存储模块是译码器中的信息存储模块,主要由RAM组成,用于数据的写入和读取;矩阵参数控制模块由存储着矩阵信息的ROM组成,存储着矩阵的行列地址索引以及循环移位系数等参数。

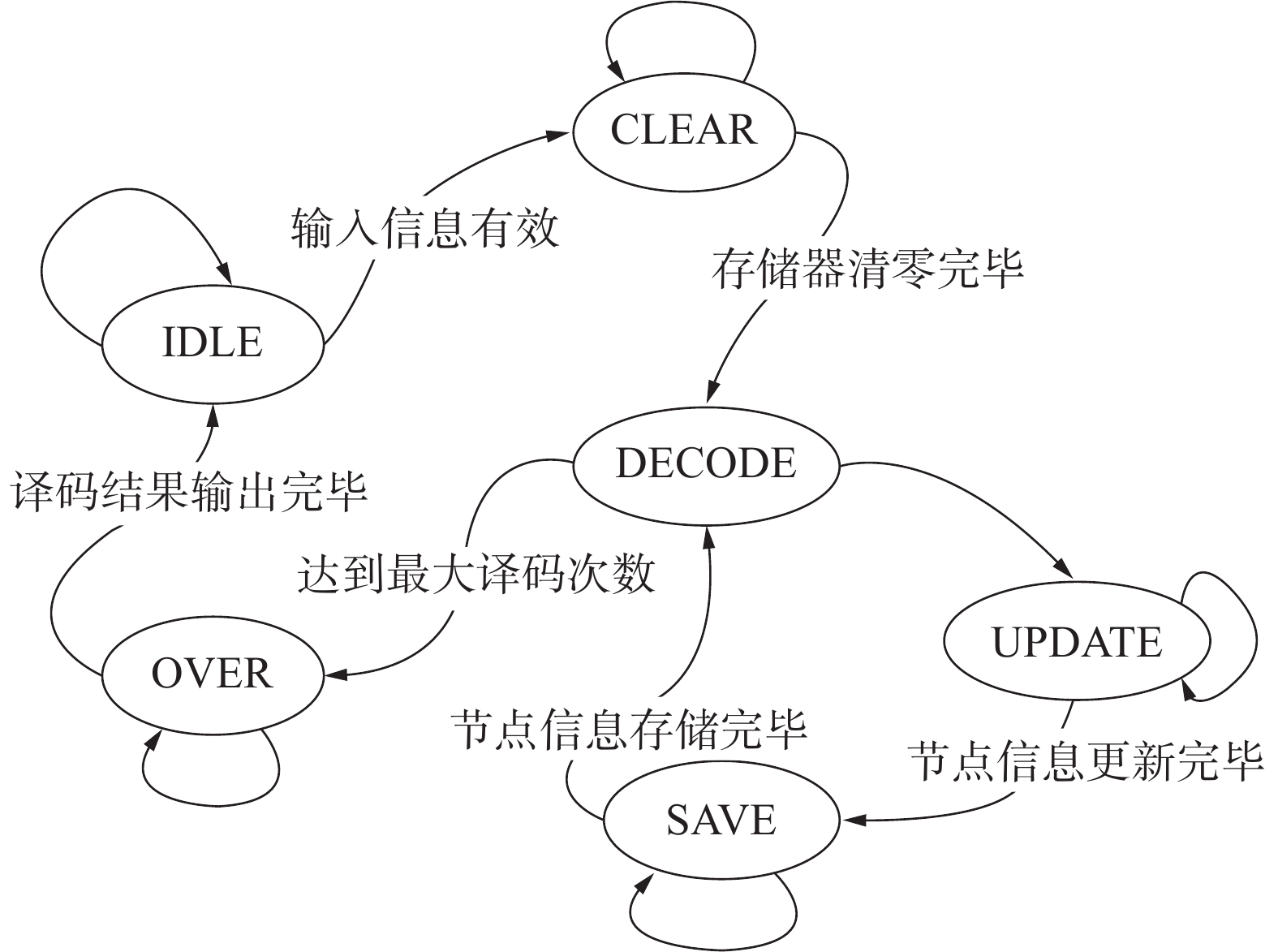

译码迭代控制模块采用状态机实现,共有6个状态,状态转移图如图9所示。CLEAR状态负责将节点信息RAM进行初始化;DECODE状态读取矩阵相关参数,初始化译码器的控制信号;UPDATE状态进行节点的信息更新;SAVE状态对更新后的节点信息进行保存;OVER状态将译码结果输出,输出完毕后返回IDLE状态。

|

Download:

|

| 图 9 译码器状态转移 | |

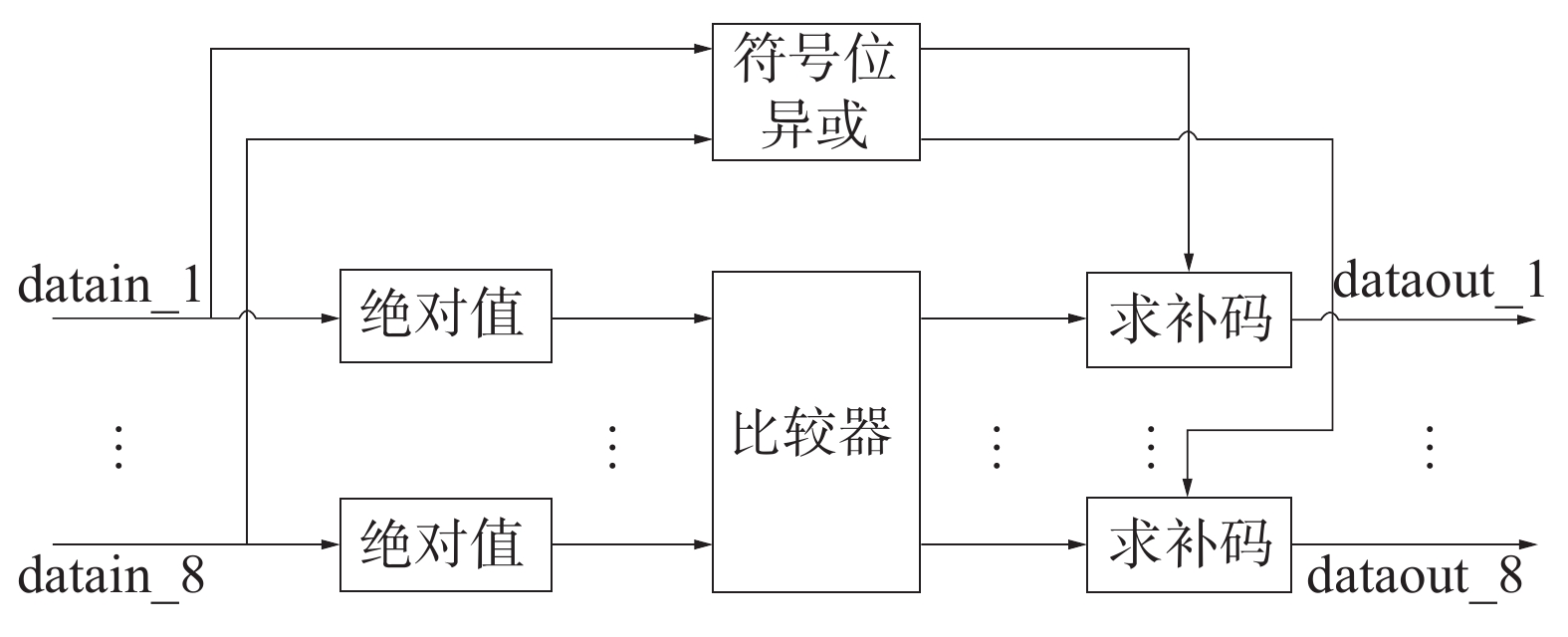

节点更新计算模块的主要功能是进行变量节点的更新和校验节点的信息更新。此模块主要步骤分为有符号加减法运算、符号整理运算、取绝对值最小值运算和乘法运算。首先,读取层存储模块中的上一层校验节点信息以及上一次迭代产生的变量节点后验概率信息,进行相减后得到更新的变量节点信息。之后,进行校验节点信息的更新,主要分为符号位相乘(异或)、求绝对值的最小值和次小值、比较并取补码值3个状态。符号相乘和取模运算是同时进行的,输入数据的最高位为符号位,将其进行异或运算,即符号相乘。求绝对值时,当数据符号为正,截掉符号位,保留其他位;当符号为负,将其他位取反后加一。因为校验矩阵的最大行重为8,所以求最小值和次小值运算需要花费3个时钟,首先将8个输入数据两两比较,分为绝对值大的一组和小的一组;再将绝对值小的一组中的4个数据两两比较,分为绝对值大的一组和绝对值小的一组;绝对值小的一组中比较出最小值,剩下的数据比较出次小值,然后将比较得出的值取补码,校验节点信息更新完毕。最后将更新后的变量节点信息与校验节点信息相加,得到更新后的变量节点后验概率信息,分层译码中的一层译码结束,继续进行下一层译码。节点更新计算模块时序仿真如图10所示,结构图如图11所示。

|

Download:

|

| 图 10 节点更新计算模块时序仿真 | |

|

Download:

|

| 图 11 节点更新计算模块结构 | |

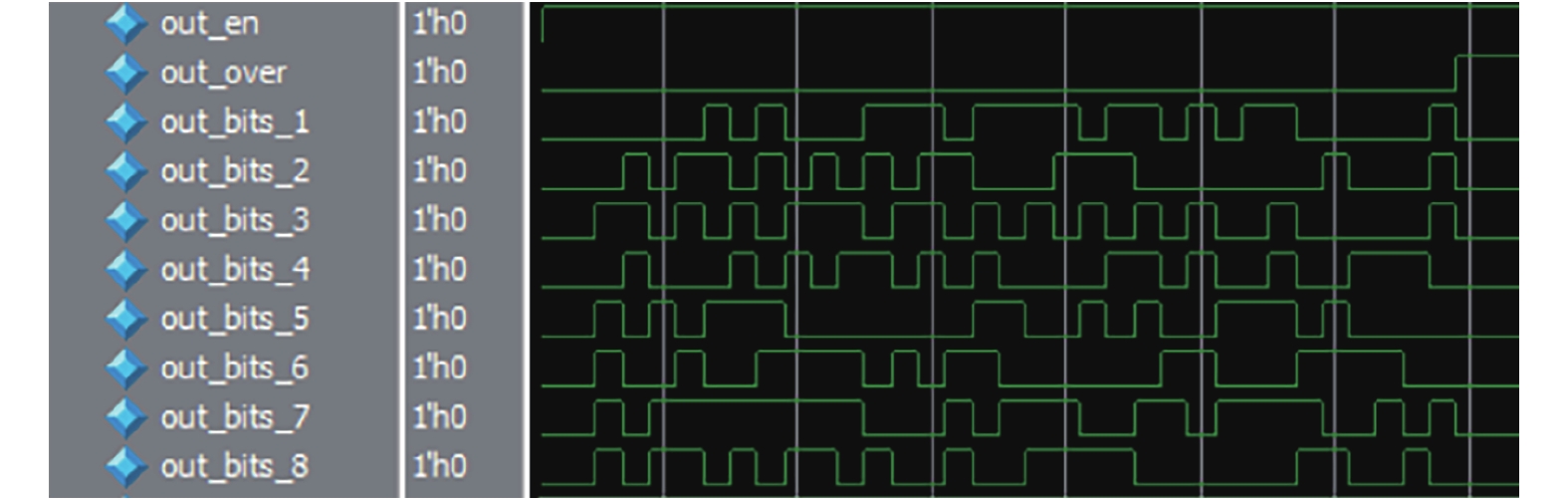

将译码器通过Verilog 硬件描述语言实现,使用Modelsim 10.7软件进行时序仿真,时序波形如图12所示。在Xilinx xc7k325tff900-2芯片上进行实现,译码器资源占用如表2所示。

|

Download:

|

| 图 12 译码器输出波形时序 | |

|

|

表 2 译码器资源占用表 |

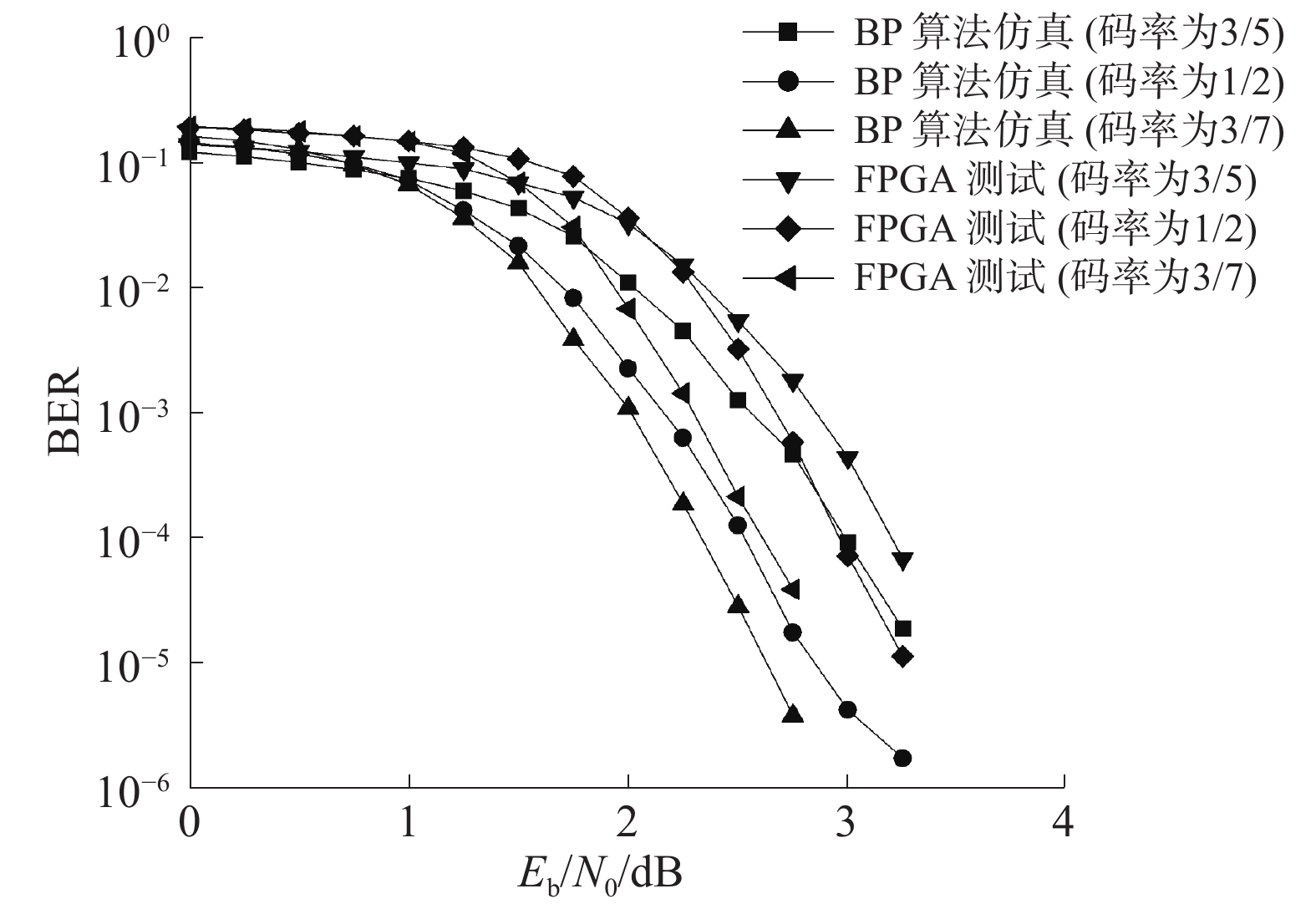

可以看出,译码器中的节点更新计算单元主要消耗LUT资源,而后验概率信息与校验节点信息存储模块消耗了一部分RAM资源来进行信息的存储,译码器整体资源占用较低。对译码器进行性能仿真,并与软件仿真结果进行对比,结果如图13所示。可以看出FPGA中的结果与软件仿真的结果具有0.5 dB左右的差异,一方面是由于输入的信噪比经过量化输入到译码器中,存在量化误差;另一方面是由于最小和译码在迭代更新计算过程中并没有进行和积运算,而是用取最小值作为近似导致的。本文所设计的3种码率在归一化信噪比为3.5 dB时FPGA仿真的误比特率都可以达到10−5量级,具有较好的译码性能。

|

Download:

|

| 图 13 BP译码仿真与FPGA测试性能对比 | |

1)针对无线信道的时变特性,本文设计了一种码率兼容的空间耦合LDPC码,通过对高码率的校验矩阵进行扩展,能够实现3种不同码率的码率兼容,可以适应不同信道条件下的需求。

2)本文基于FPGA完成了码率兼容空间耦合LDPC码的编码器和译码器的设计。编码器和译码器根据特殊的校验矩阵结构实现码率兼容,在保证编译码性能的同时,具有较低的资源占用和较好的性能,在实际工程应用中具有一定参考价值,可以为B5G/6G移动通信系统提供可借鉴的传输编码方案。

| [1] |

GALLAGER R. Low-density parity-check codes[J]. IRE transactions on information theory, 1962, 8(1): 21-28. DOI:10.1109/TIT.1962.1057683 ( 0) 0)

|

| [2] |

ETSI. ETSI EN 302 307 V1.3.1 (2013-03), Digital Video Broadcasting (DVB); second generation framing structure, channel coding and modulation systems for broadcasting, interactive services, news gathering and other broadband satellite applications (DVB-S2)[S]. [S.l.] ETSI, 2013.

( 0) 0)

|

| [3] |

3GPP. Draft_Minutes_report_RAN1#86b_v100[EB/OL]. (2016–11–10)[2020–8–13]. https://www.3gpp.org/ftp/tsg_ ran/WG1_RL1/TSGR1_86b/Report.

( 0) 0)

|

| [4] |

IEEE. IEEE Std 802.11-2007, IEEE standard for information technology-telecommunications and information exchange between systems-local and metropolitan area networks-specific requirements-Part 11: Wireless LAN medium access control (MAC) and physical layer (PHY) specifications[S]. Washington: IEEE, 2007: 1-1076.

( 0) 0)

|

| [5] |

FELSTROM A J, ZIGANGIROV K S. Time-varying periodic convolutional codes with low-density parity-check matrix[J]. IEEE transactions on information theory, 1999, 45(6): 2181-2191. DOI:10.1109/18.782171 ( 0) 0)

|

| [6] |

LENTMAIER M, SRIDHARAN A, COSTELLO D J, et al. Iterative decoding threshold analysis for LDPC convolutional codes[J]. IEEE transactions on information theory, 2010, 56(10): 5274-5289. DOI:10.1109/TIT.2010.2059490 ( 0) 0)

|

| [7] |

白宝明, 孙韶辉, 王加庆. 5G移动通信中的信道编码[M]. 北京: 电子工业出版社, 2020: 133-134.

( 0) 0)

|

| [8] |

SI Zhongwei, THOBABEN R, SKOGLUND M. Rate-compatible LDPC convolutional codes achieving the capacity of the BEC[J]. IEEE transactions on information theory, 2012, 58(6): 4021-4029. DOI:10.1109/TIT.2012.2188990 ( 0) 0)

|

| [9] |

MA Junyang, SI Zhongwei, HE Zhiqiang, et al. Recursive encoding of spatially coupled LDPC codes with arbitrary rates[C]//Proceedings of 2015 IEEE 26th Annual International Symposium on Personal, Indoor, and Mobile Radio Communications (PIMRC). Hong Kong, China, 2015: 127-131.

( 0) 0)

|

| [10] |

MITCHELL D M, LENTMAIER M, PUSANE A E, et al. Randomly punctured LDPC codes[J]. IEEE journal on selected areas in communications, 2016, 34(2): 408-421. DOI:10.1109/JSAC.2015.2507758 ( 0) 0)

|

| [11] |

HOU Wei, LU Shan, CHENG Jun. Rate-compatible spatially coupled LDPC code ensembles based on repeat-accumulate extensions[J]. IET communications, 2016, 10(17): 2422-2426. DOI:10.1049/iet-com.2015.1031 ( 0) 0)

|

| [12] |

PUSANE A E, FELTSTROM A J, SRIDHARAN A, et al. Implementation aspects of LDPC convolutional codes[J]. IEEE transactions on communications, 2008, 56(7): 1060-1069. DOI:10.1109/TCOMM.2008.050519 ( 0) 0)

|

| [13] |

王思杰. 空间耦合LDPC编码构造的研究与应用[D]. 北京: 北京邮电大学, 2017.

( 0) 0)

|

| [14] |

LI Huaan, BAI Baoming, MU Xijin, et al. Algebra-assisted construction of quasi-cyclic LDPC codes for 5G new radio[J]. IEEE access, 2018, 6: 50229-50244. DOI:10.1109/ACCESS.2018.2868963 ( 0) 0)

|

| [15] |

ZHANG Kai, HUANG Xinming, WANG Zhongfeng. High-throughput layered decoder implementation for quasi-cyclic LDPC codes[J]. IEEE journal on selected areas in communications, 2009, 27(6): 985-994. DOI:10.1109/JSAC.2009.090816 ( 0) 0)

|

| [16] |

ALI I, KIM J H, KIM S H, et al. Improving windowed decoding of SC LDPC codes by effective decoding termination, message reuse, and amplification[J]. IEEE access, 2017, 6: 9336-9346. ( 0) 0)

|

| [17] |

UL HASSAN N, PUSANE A E, LENTMAIER M, et al. Non-uniform window decoding schedules for spatially coupled LDPC codes[J]. IEEE transactions on communications, 2017, 65(2): 501-510. DOI:10.1109/TCOMM.2016.2633466 ( 0) 0)

|

2020, Vol. 47

2020, Vol. 47