从2005年“物联网”概念提出以来,超高频射频识别作为构成“物联网”的核心技术之一,国家在大力敦促其有关领域的研究,包括通信协议标准化、基带防碰撞算法、无源标签芯片的研发和生产等[1]。超高频无源标签芯片通过射频前端的整流器将射频信号能量转化为直流电源供电,其直流电压随着识别距离变化波动很大,通常在1.5~3 V之间且伴有高频纹波[2],因此,模拟前端中的基准电压源必须有很高的抗干扰能力。同时,超高频无源标签芯片的设计以低成本为导向,需要在版图面积、芯片功耗及性能上做出取舍。

传统的带隙基准电压源需要引入片上电阻、BJT以及运算放大器,较大的功耗和版图面积使其不适于无源标签芯片[3-5],因此低压低功耗的亚阈值基准源被广泛的采纳和研究,但普遍存在电源抑制比(power supply rejection ratio,PSRR)低下、温度系数差的问题。文献[6]中采用无电阻设计思路,简单的核心结构加以Cascode电流镜使其能实现基准电压的功能,但其低频时的PSRR仅为−26.38 dB;文献[7]提出了电阻俢调的新技术来改善温度系数,但需要数字电路介入,在版图面积和功耗上并无优势;文献[8]提出了新型的预稳压结构,低频时PSRR高达−115 dB,具有重要的参考意义。

文中所设计的低压低功耗基准电压源采用全MOS的核心结构,并通过预稳压电路提高电源噪声抑制能力,在减小版图面积和功耗的同时,具有很高的电源抑制比和良好的温度特性。

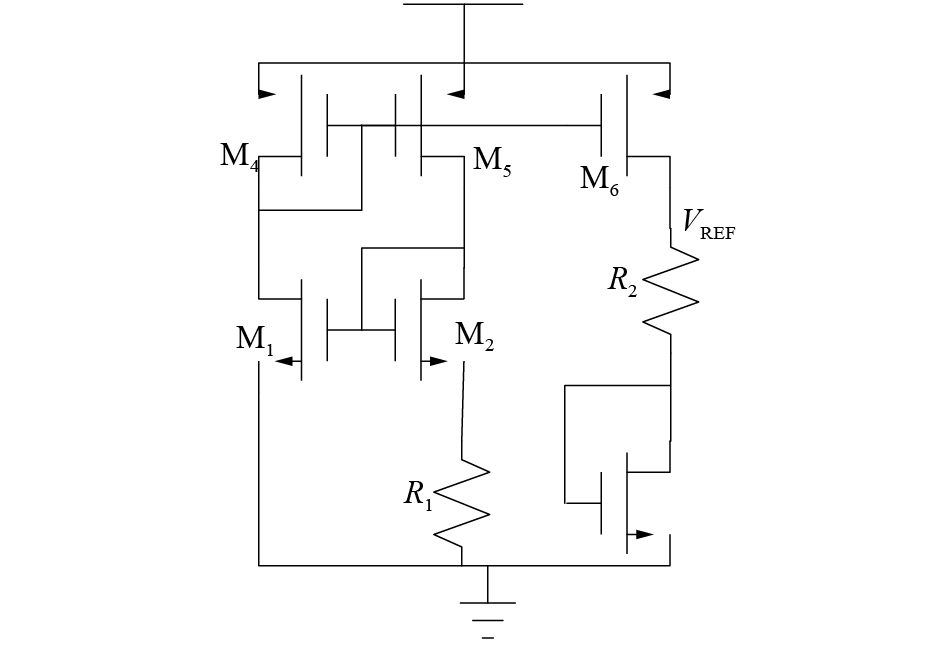

1 亚阈值基准原理分析 1.1 传统亚阈值基准结构

|

Download:

|

| 图 1 传统亚阈值基准结构 | |

|

Download:

|

| 图 1 传统亚阈值基准结构 | |

图中M1和M2均处于亚阈值区,可得其漏端电流为

| ${I_{{\rm{DS}}}} = \mu {C_{{\rm{OX}}}}V_{\rm{T}}^2\frac{W}{L}\exp (\frac{{{V_{{\rm{GS}}}} - {V_{{\rm{TH}}}}}}{{m{V_{\rm{T}}}}})$ | (1) |

式中:m为亚阈值修正因子,通常在1~2之间[10],本文取1;μ为电子迁移率;COX为栅极单位面积电容。将式(1)转换可得VGS为

| ${V_{{\rm{GS}}}} = {V_{\rm{T}}}\ln (\frac{{{I_{{\rm{DS}}}}}}{{\mu {C_{{\rm{OX}}}}V_{\rm{T}}^2}}\frac{L}{W}) + {V_{{\rm{TH}}}}$ | (2) |

电阻R1上的压降为M1和M2的VGS之差,由式(2)可得

| ${V_{{\rm{GS1}}}} - {V_{{\rm{GS2}}}} = {V_{\rm{T}}}\ln \frac{{{\eta _2}}}{{{\eta _1}}}$ |

式中η表示MOS管的宽长比(下文一致)。若忽略R1的温度系数,便可得到正温度系数的偏置电流:

| ${I_{{\rm{BIAS}}}} = \frac{{{V_{\rm{T}}}\ln ({\eta _2}/{\eta _1})}}{{{R_1}}}$ | (4) |

M3处于饱和区,其VGS为

| ${V_{{\rm{GS_3}}}} = {V_{_{{\rm{TH}}}}} + \sqrt {\frac{2}{{\mu {C_{{\rm{OX}}}}{\eta _3}}}\frac{{\lambda {V_{\rm{T}}}\ln n}}{{R1}}} $ |

式中:λ为M6与M4宽长比的比值;n为M2与M1宽长比的比值。则所得到的基准电压为

| ${V_{{\rm{REF}}}} = {V_{{\rm{TH}}}} + \sqrt {\frac{2}{{\mu {C_{{\rm{OX}}}}{\eta _3}}}\frac{{\lambda {V_{\rm{T}}}\ln n}}{{{R_1}}}} + \frac{{\lambda {V_{\rm{T}}}\ln n}}{{{R_1}}}{R_2}$ | (6) |

MOS管的阈值电压可近似为线性负温度系数[11],即式(4)第一项为负温度项,后两项均为正温度项,因此可以得到温度系数较小的基准电压源。但是片上电阻和电子迁移率μ都有一定的温度特性,使得传统亚阈值基准电压的温度系数很难把控,同时片上电阻消耗大量的版图面积。

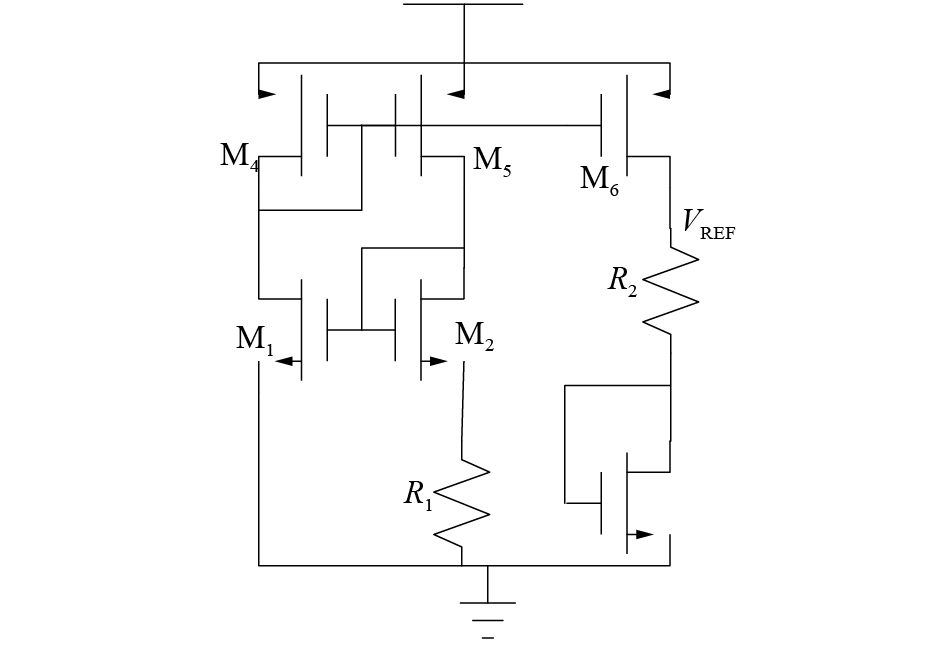

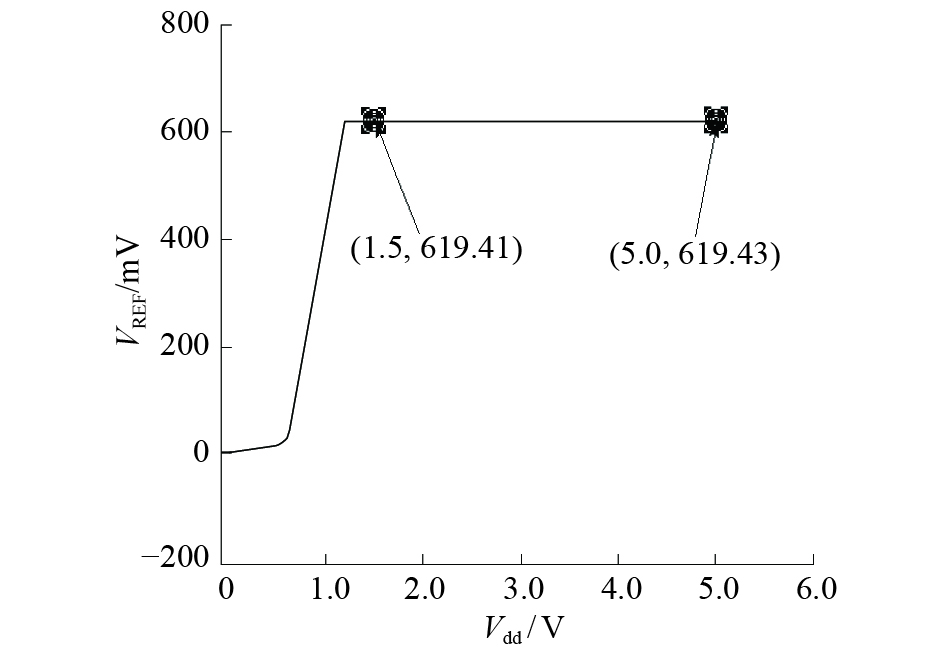

1.2 全MOS基准核心电路设计图2为本文提出的基准核心电路。其中,M3为处于深线性区的NMOS电阻,用于替代片上电阻;M1、M2、M5、M6均处于亚阈值区;M7位于饱和区;M4处于线性区,构成源极负反馈,用于稳定M5和M6的工作区域;M8~M12构成电流镜,且流经M12的电流为M8~M11的两倍;VPRE为预稳压模块的输出电压。

|

Download:

|

| 图 2 全MOS基准核心电路 | |

M3的导通电阻为

| ${R_{{\rm{on_3}}}} = \frac{1}{{\mu {C_{{\rm{OX}}}}{\eta _3}({V_{{\rm{GS_7}}}} - {V_{{\rm{TH}}}})}}$ | (7) |

联立式(3)、(5),可得偏置电流:

| ${I_{{\rm{BIAS}}}} = \mu {C_{{\rm{OX}}}}{\eta _3}({V_{{\rm{GS7}}}} - {V_{{\rm{TH}}}}){V_{\rm{T}}}\ln \frac{{{\eta _2}}}{{{\eta _1}}}$ | (8) |

M7的栅源电压关于偏置电流的表达式为

| ${V_{{\rm{GS_7}}}} = {V_{{\rm{TH}}}} + \sqrt {\frac{{2{I_{{\rm{DS}}}}}}{{\mu {C_{{\rm{OX}}}}{\eta _7}}}} $ | (9) |

式中

联立式(6)、(7),可获得偏置电流的另一种表达式:

| ${I_{{\rm{BIAS}}}} = \frac{{4\mu {C_{{\rm{OX}}}}\eta _3^2}}{{{\eta _7}}}{[{V_{\rm{T}}}\ln \frac{{{\eta _2}}}{{{\eta _1}}}]^2}$ | (10) |

再将式(8)代入式(7),可得:

| ${V_{{\rm{GS_7}}}} = {V_{{\rm{TH}}}} + \frac{{4{\eta _3}\ln ({\eta _2}/{\eta _1})}}{{\sqrt {{\eta _7}} }}{V_{\rm{T}}}$ |

M5和M6栅源电压差值为

| ${V_{{\rm{GS_5}}}} - {V_{{\rm{GS_6}}}} = {V_{\rm{T}}}\ln ({\eta _6}/{\eta _5})$ |

最终,可得VREF的表达式:

| $\begin{aligned}{V_{{\rm{REF}}}} = & {V_{{\rm{GS7}}}} - {V_{{\rm{GS6}}}} + {V_{{\rm{GS5}}}} = \\& {V_{{\rm{TH}}}} + \frac{{4{\eta _3}\ln ({\eta _2}/{\eta _1})}}{{\sqrt {{\eta _7}} }}{V_{\rm{T}}} + {V_{\rm{T}}}\ln \frac{{{\eta _6}}}{{{\eta _5}}}\end{aligned}$ | (13) |

对比式(4)、(9),消除了与工艺有关的参数μ,温度系数更加稳定。且MOS电阻的引用大大节省芯片面积。求导可得温度系数为

| $\frac{{\partial {V_{{\rm{REF}}}}}}{{\partial T}} = \beta + [\frac{{4{\eta _3}\ln ({\eta _2}/{\eta _1})}}{{\sqrt {{\eta _7}} }} + \ln \frac{{{\eta _6}}}{{{\eta _5}}}]\frac{k}{q}$ |

式中β为阈值电压的温度系数,为负常数,后两项均为正常数,因此只需调节M1~M6的宽长比即可获得零温度系数的基准电压。

2 基准源系统设计设计的基准源包括基准核心电路、预稳压电路以及启动电路(黑色框内)。完整结构如图3所示。

2.1 启动电路基准电路存在简并点,即所有管子都处于无电流状态,需要启动电路来脱离简并态。正常上电时基准电压输出低电压,因此反相器输出高电平,NMOS管导通拉低M13和M8栅极,电路启动。正常工作时,NMOS截止。

2.2 预稳压电路设计设计的预稳压电路由M13~M19组成。M17~M19构成小信号电阻,其阻值很小,用req表示。当电源发生波动时(变化量用vdd表示),vpre为VPRE的变化量,则M14中的电流变化量可以表示为

| ${i_{14}} = {g_{{\rm{ds14}}}}({v_{{\rm{dd}}}} - {v_{{\rm{pre}}}})$ |

由于M16精确复制了基准产生的偏置电流,其电流视作恒定,同时流经基准核心模块电流也恒定,因此i14将全部作用于小信号电阻req上,即

| ${i_{14}} = \frac{{{v_{{\rm{pre}}}}}}{{{r_{{\rm{eq}}}}}} = {g_{{\rm{ds14}}}}({v_{{\rm{dd}}}} - {v_{{\rm{pre}}}})$ | (16) |

转换式(10)可得:

| $\frac{{{v_{{\rm{dd}}}}}}{{{v_{{\rm{pre}}}}}} = \frac{1}{{{r_{{\rm{eq}}}}{g_{{\rm{ds}}14}}}} + 1 = K$ |

由于req和gds14数量级很小,因此K值很大,即vpre远小于vdd,实现了预稳压的作用。

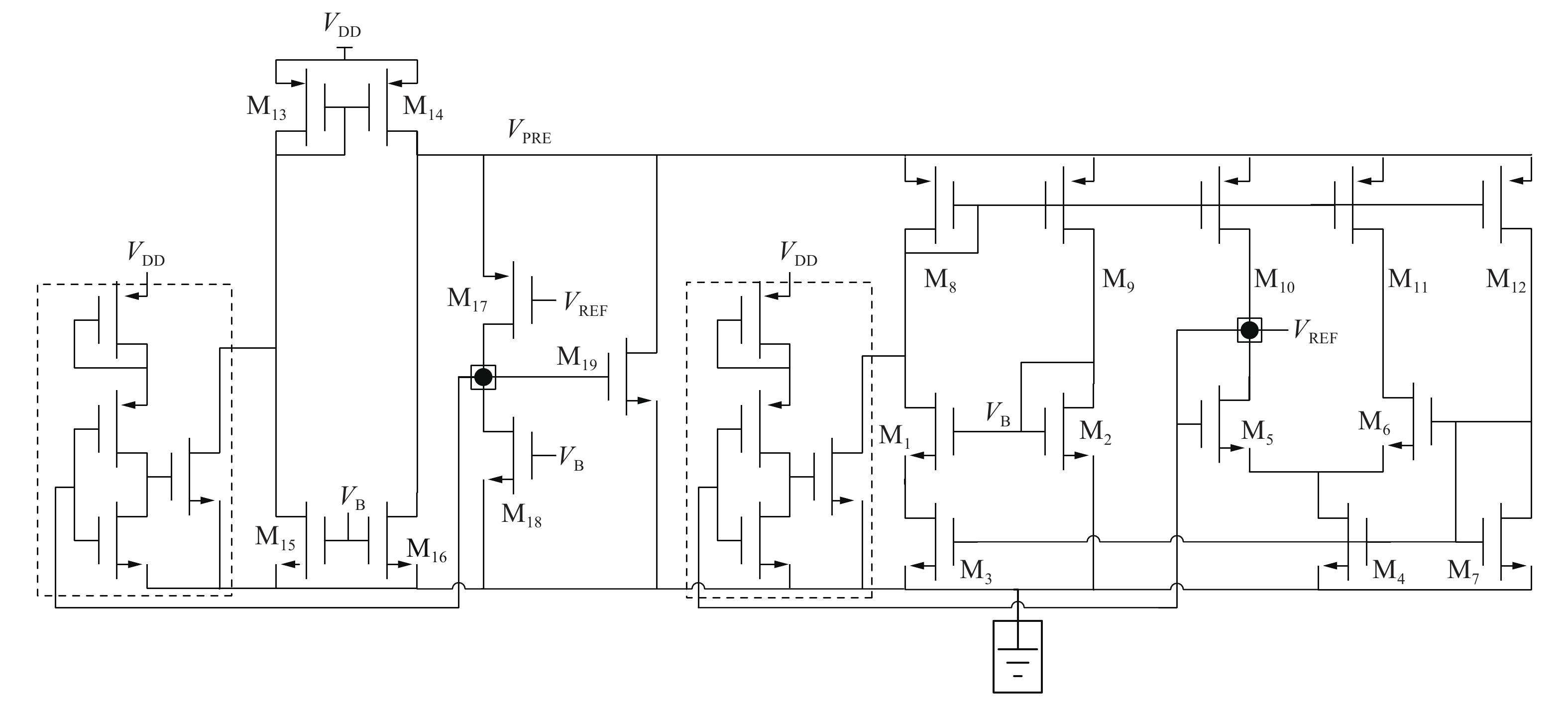

3 仿真分析本次的电路设计基于SMIC 0.18 μm CMOS工艺,并采用Hspice高精度仿真软件进行性能及参数的仿真和验证。

|

Download:

|

| 图 3 基准源总体电路 | |

图4为线性调整率的仿真结果。供电电压最低在1.1 V时基准即可工作。在1.5~5.0 V供电范围内,基准电压变化22 μV,线性调整率为4.9 μV/V。

|

Download:

|

| 图 4 线性调整率仿真波形 | |

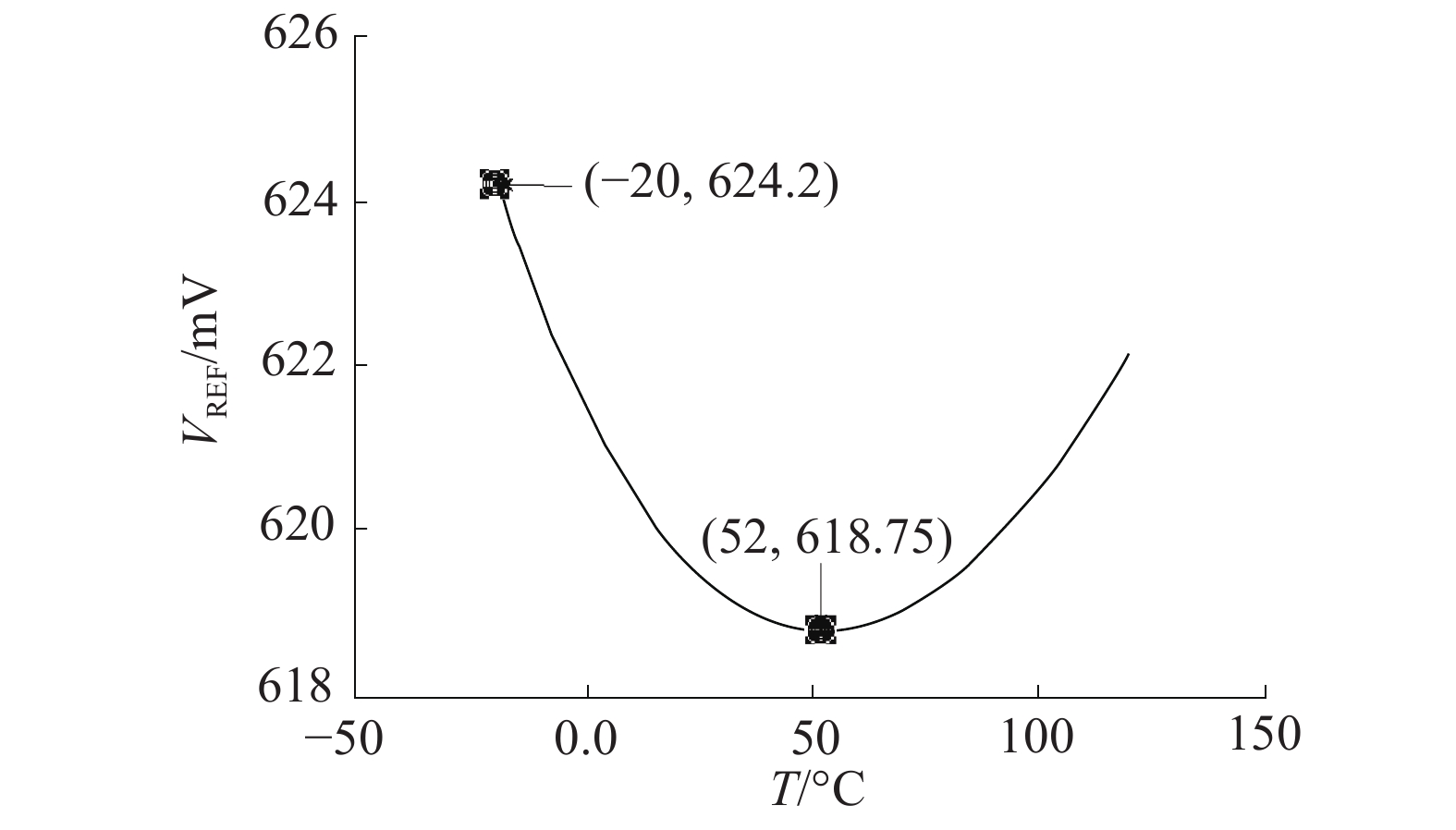

图5为在1.5 V供电电压下,基准源的温度系数仿真结果。在−20~120 ℃的温度区间内,基准最高为624.2 mV,最低为618.75 mV,平均输出619 mV,温度系数为6.2×10−6/℃。

|

Download:

|

| 图 5 温度系数仿真结果 | |

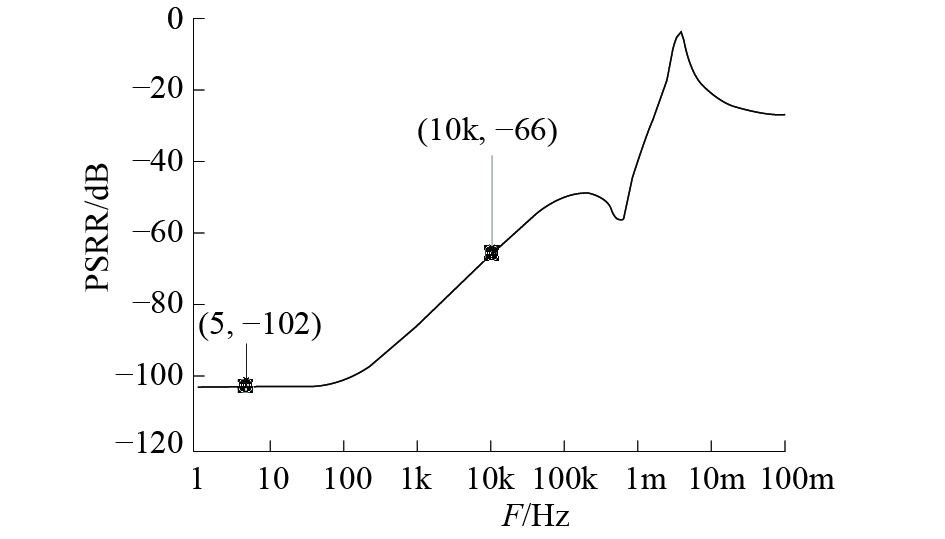

图6为在1.5 V供电电压下的电源抑制比仿真结果。结果表明,低频时的PSRR高达−102 dB,在10 kHz的噪声频率附近的PSRR也有−65 dB。

|

Download:

|

| 图 6 PSRR仿真结果 | |

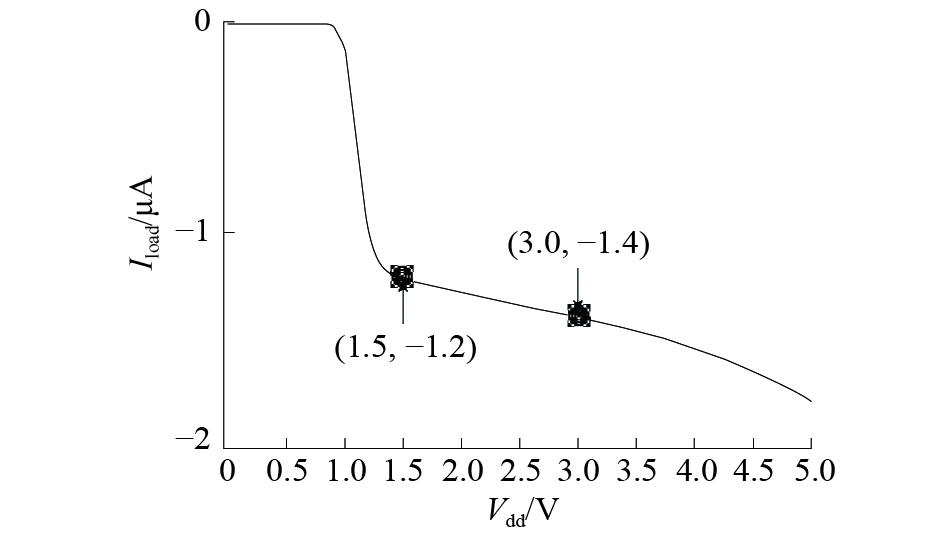

图7为不同供电电压下电路的直流功耗仿真结果。在1.5 V典型供电电压下,直流功耗约为1.8 μW,3.0 V时直流功耗为4.2 μW。

|

Download:

|

| 图 7 电流消耗仿真结果 | |

表1给出了本文设计的基准源与参考文献的性能参数比较。文献[8]为无运放设计的带隙基准基准,通过预稳压电路实现很高的电源抑制比,但带隙基准的功耗很大;文献[6]为全MOS低压基准设计,结构简单功耗低,但其温度系数和PSRR特性较本文劣势明显。文献[7]对亚阈值基准的温度系数进行了大幅度优化,但俢调电路增加了功耗。本文在功耗、温度特性和电源抑制得到了很好的权衡。

|

|

表 1 性能参数对比 |

本文设计了一适用于无源标签芯片的亚阈值基准电压源,具体创新点为:1)电路采用全MOS管搭建;2)通过MOS器件的亚阈值特性实现低压低功耗,可在1.5 V电压下工作,功耗为1.8 μW;3)通过加入预稳压电路实现高电源抑制比,低频时PSRR可达−102 dB;4)提出的新型基准核心电路,温度特性优良,达到6.2×10-6/℃。低压、低功耗、低温度系数的优良特性使其也能适用于无线通信及可穿戴设备等诸多领域。但是本文的基准电压有MOS器件的VGS实现,因此在不同工艺下的漂移较大,因此之后将进一步研究基准电压源工艺调整方面的研究。

| [1] |

闵丽娟, 卢捍华, 吴瑞雯. 物联网控制系统综述[J]. 南京邮电大学学报: 自然科学版, 2017, 37(2): 68-73. ( 0) 0)

|

| [2] |

姜宇. 低功耗无源UHF RFID标签芯片射频模拟前端电路研究[D]. 天津: 天津大学, 2010: 50-56.

( 0) 0)

|

| [3] |

GRAY P R, HURST P J, LEWIS S H, et al. Analysis and design of analog integrated circuits[M]. 5th ed. New York: Wiley, 2009: 321−326.

( 0) 0)

|

| [4] |

RAZAVI B. Design of analog CMOS integrated circuits[M]. New York: McGraw-Hill Education, 2017: 310−324.

( 0) 0)

|

| [5] |

KANG Xiaozhi, TANG Zhangwen. A novel high PSRR bandgap over a wide frequency range[C]//Proceedings of the 10th IEEE International Conference on Solid-State and Integrated Circuit Technology. Shanghai, China, 2015: 418−420.

( 0) 0)

|

| [6] |

张涛, 陈远龙, 王影, 等. 一种低功耗亚阈值全MOS管基准电压源的设计[J]. 电子元件与材料, 2016, 35(5): 28-30. ( 0) 0)

|

| [7] |

冯纯益. 纳米工艺下低压低功耗带隙基准源的研究[D]. 成都: 电子科技大学, 2013: 46-50.

( 0) 0)

|

| [8] |

ZHU Yuanming, LIU Fei, YANG Yajuan, et al. A-115dB PSRR CMOS bandgap reference with a novel voltage self-regulating technique[C]//Proceedings of IEEE 2014 Custom Integrated Circuits Conference. San Jose, USA, 2014: 1-4.

( 0) 0)

|

| [9] |

XIA Xiaojuan, XIE Liang, SUN Weifeng. A CMOS voltage reference based on VGS and ΔVGS in the weak inversion region

[J]. Journal of semiconductors, 2008, 29(8): 1523-1528. ( 0) 0)

|

| [10] |

黎进军. 亚阈值CMOS电压基准源的研究与设计[D]. 广州: 华南理工大学, 2012: 13-14.

( 0) 0)

|

| [11] |

CHOUHAN S S, HALONEN K. A 0.67-μW 177-ppm/℃ all-MOS current reference circuit in a 0.18-μm CMOS technology

[J]. IEEE transactions on circuits and systems II: express briefs, 2016, 63(8): 723-727. DOI:10.1109/TCSII.2016.2531158 ( 0) 0)

|

2018, Vol. 45

2018, Vol. 45