2. 射频集成与组装技术国家与地方联合工程实验室, 江苏 南京 210023

2. National & Local Joint Engineering Laboratory for RF Integration and Micro-packaging Technologies, Nanjing 210023, China

随着集成电路规模的不断增长,器件的特征尺寸也随之持续缩小,当器件的沟道长度和源漏的耗尽区宽度为同一数量级时就被认为是短沟器件,此时短沟道效应成为制约集成电路规模增长的主要因素之一。关于短沟道效应的相关研究可以分为对材料的改进和对器件结构的调整,在新型器件结构方面,Hisamoto等提出了FinFET结构,该结构可以很好地抑制由漏致势垒降低效应引起的漏电流,但是由于其硅鳍(fin)很薄,导致器件的寄生电阻较大,因此FinFET的驱动电流能力不高。后续的研究人员对该结构进行不断优化,目前FinFET结构已被广泛应用于低功耗处理器中[1-5]。Wei Long等提出了一种dual-material gate(DMG)结构,与常规器件相比,它的栅极由两段材料构成,且靠近源极的栅极材料功函数要比在漏极一侧的材料功函数大。通过这种特殊的栅结构,漏区的电势对源区的影响将被屏蔽,从而抑制了漏致势垒降低效应,此外,该结构还可以提高沟道中载流子的漂移速度,进而提高器件的电流驱动能力和跨导[6-8]。Colinge等[9]于2010年提出一种无结型晶体管,该结构有着近乎理想的亚阈值特性,它的漏电非常小,且其迁移率对栅电压和温度的敏感性要较常规器件更低。在此基础上,Ghosh等提出了一种异质栅氧层晶体管结构,该晶体管的栅氧层由2种不同介电常数的材料构成,沟道电场在2种不同的栅氧材料的交界处存在一个电场峰值,由于电势是固定的,因此该结构将会减小漏端的高电场,从而抑制了热载流子的生成。另外,考虑隧穿效应时,异质栅可以增加隧道的距离,从而减小隧穿电流,因此该结构可以有效地降低漏电流,同时异质栅氧层也可增强器件的电流驱动能力。基于此,研究人员将该结构引入到隧穿晶体管中用以加强其电流驱动能力[10-12]。

本文提出了一种具有非平面沟道的场效应晶体管,通过器件仿真软件对其阈值电压退化情况、亚阈值特性、衬底电流和击穿特性进行了仿真,同时给出了对器件性能改善原因的分析。

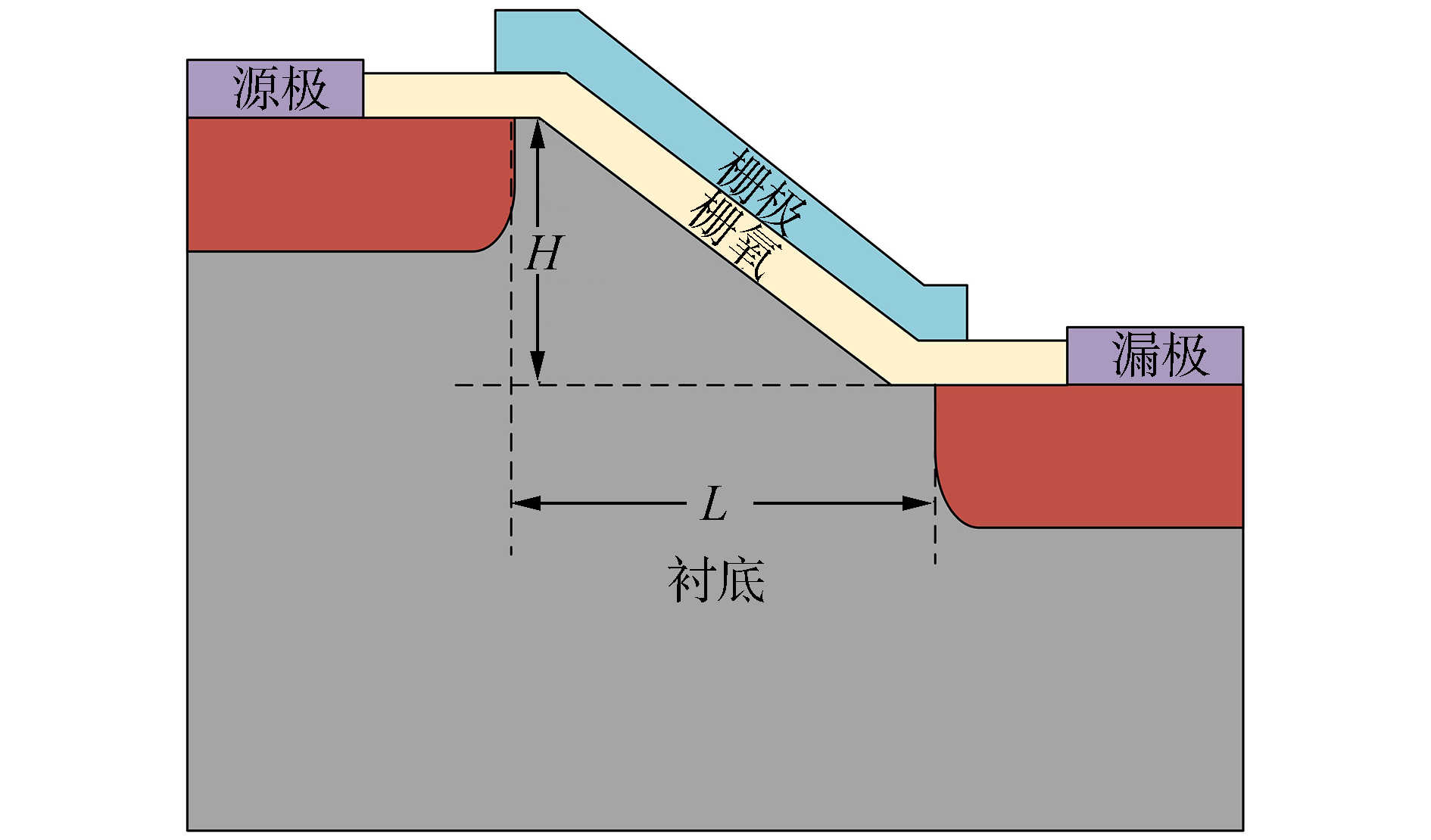

1 结构图 1为本文提出的非平面沟道晶体管,在该结构中,源区和漏区不在同一平面上,H表示源区和漏区的垂直距离,L表示源区与漏区的水平距离,即水平沟道距离。

|

Download:

|

| 图 1 非平面沟道晶体管的结构 | |

实际上,有效沟道长度Leff应该近似为

| $ {L_{{\rm{eff}}}} = \sqrt {{L^2} + {H^2}} $ |

常规晶体管中,栅氧层为厚度均匀的介质层,为保持结构参数的一致性,提出了如图 1所示的栅氧层结构,它在沟道表面任意一点的法线方向厚度均与常规结构的栅氧层厚度相同。本文以NMOS为例,仿真所采用的器件结构参数如表 1所示。为评估本文所提出的非平面沟道晶体管的性能,使用SILVACO二维器件仿真软件进行仿真,仿真所使用的模型为CVT集成模型、SRH复合模型、Sleberrherr碰撞电离模型和Fermi-Dirac载流子统计模型。

|

|

表 1 器件仿真参数 |

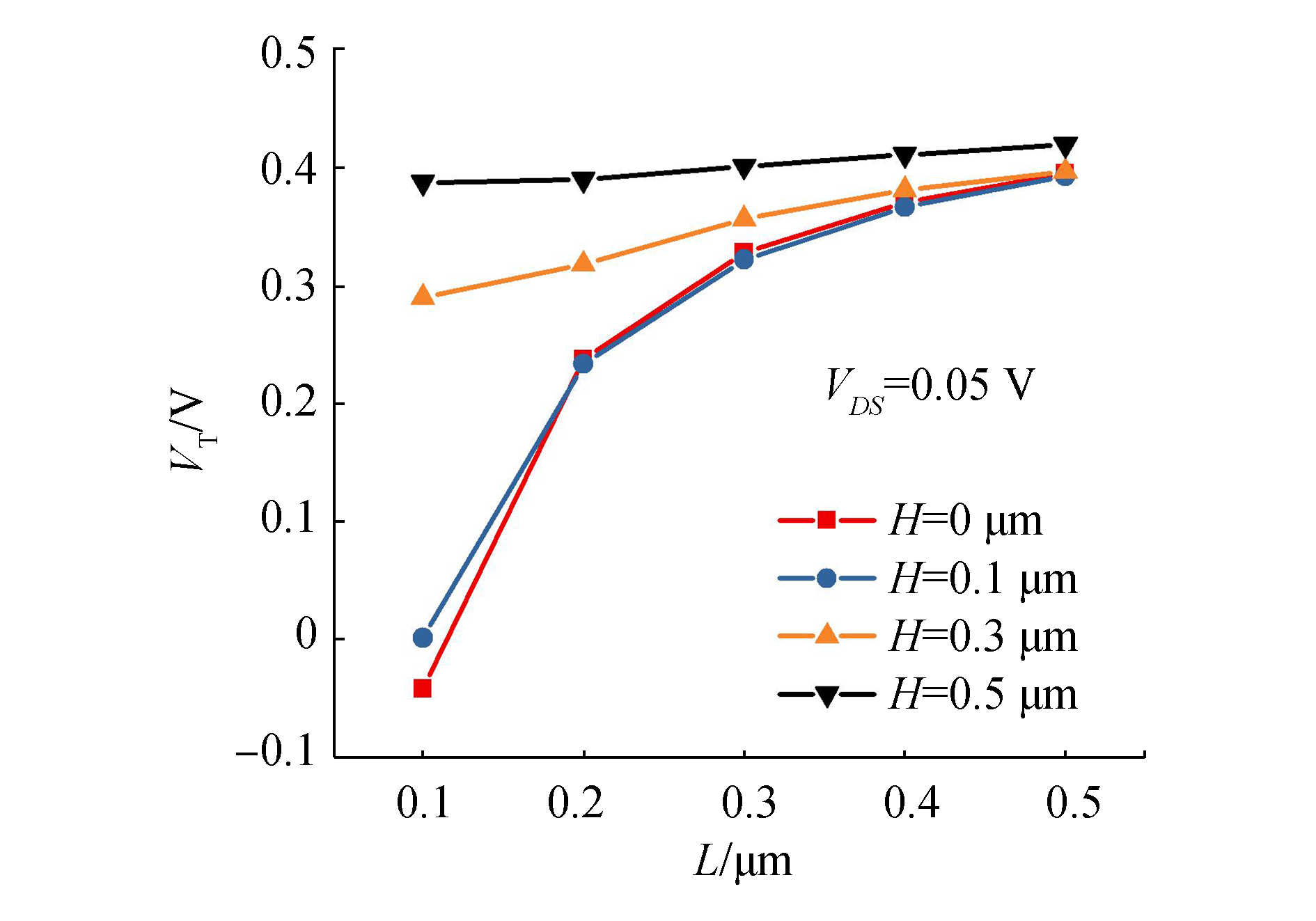

图 2对比了非平面沟道晶体管与常规晶体管阈值电压退化情况,从图中可以看出随着沟道的缩短,常规MOSFET的阈值电压急剧下降,尤其在当沟道长度低于0.1 μm时,阈值电压下降到了0 V以下,可见此时的器件根本无法关断。对于非平面沟道晶体管来说,尽管其在垂直距离为0.1 μm时与常规MOSFET的阈值电压退化情况没有明显的区别,但是当垂直距离为0.3 μm时其阈值电压下降幅度缩小了很多,在垂直距离为0.5 μm时阈值电压几乎没有发生退化。这表明随着垂直距离的增加,器件的阈值电压退化情况得到缓解。阈值电压退化是短沟道效应的一种,而垂直距离的引入增加了器件的有效沟道长度,因此该结构对阈值电压退化改善的原因也是显而易见的。

|

Download:

|

| 图 2 不同垂直距离下的阈值电压退化情况 | |

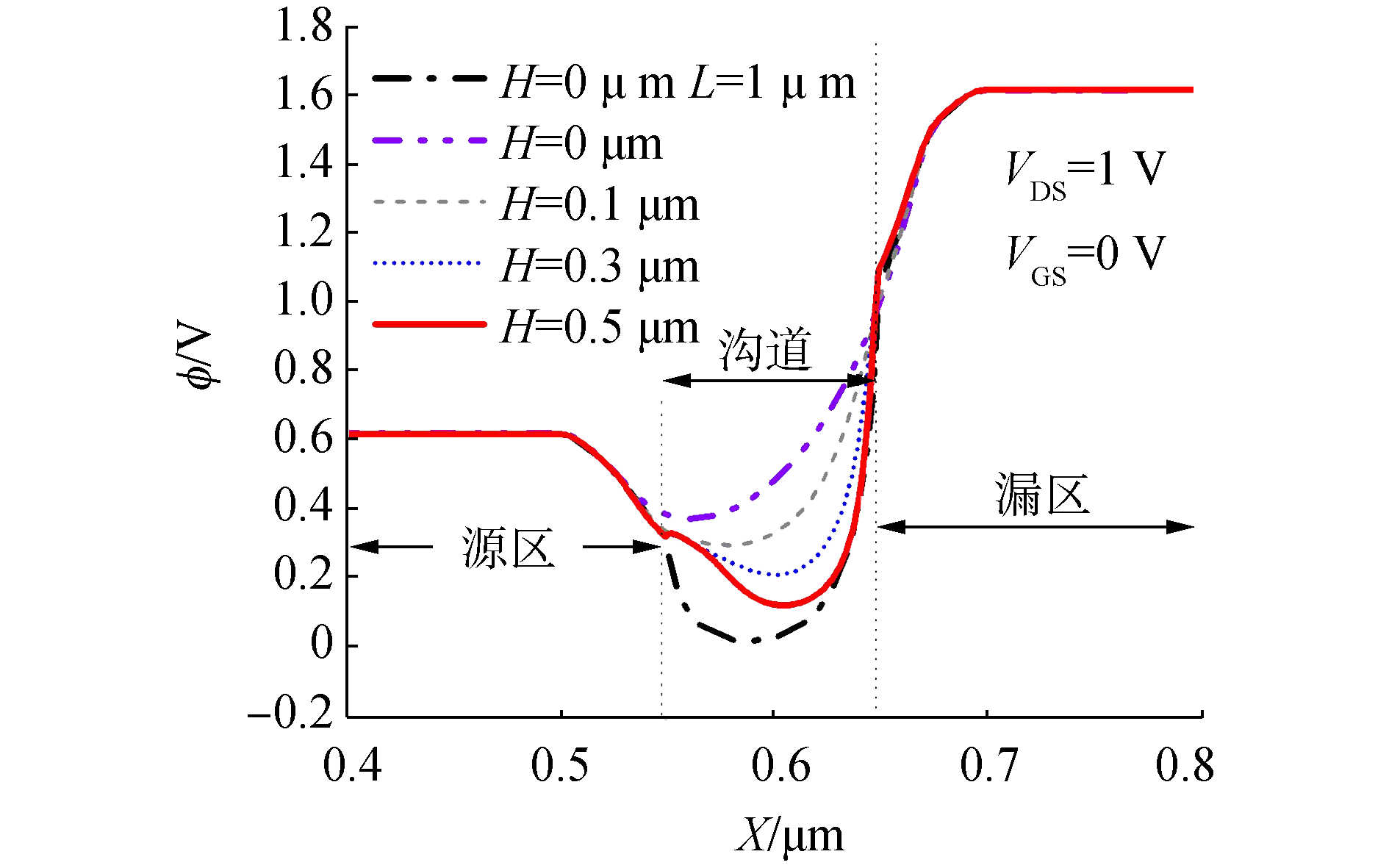

图 3是常规器件与不同垂直距离下非平面沟道晶体管的电势分布图,其中常规器件的沟道长度和非平面沟道晶体管的沟道长度为0.1 μm。另外设置1 μm的常规器件作为对照,以此检验短沟道的新结构器件与长沟道常规器件的性能差异。从图中可以看出,与常规长沟器件相比,沟道长度为0.1 μm时的沟道表面电势要高得多,这是由于沟道缩短后,漏区的高电势将会影响到整个沟道区,从而导致沟道的电势升高。这对于器件来说是有害的,因为沟道电势的提升将会导致其更容易反型,也即器件的阈值电压将会降低,从而导致阈值电压的退化,严重时将会导致器件在栅电压为零时沟道仍处于开启状态。对于非平面沟道晶体管来说,从图中可以看出,随着垂直距离的增加,沟道表面的电势也随之降低,因而保证了沟道缩短时沟道仍可以被关断,也就是说器件的阈值电压退化可以通过非平面沟道结构得到改善。

|

Download:

|

| 图 3 不同垂直距离下和不同沟道长度下的电势分布 | |

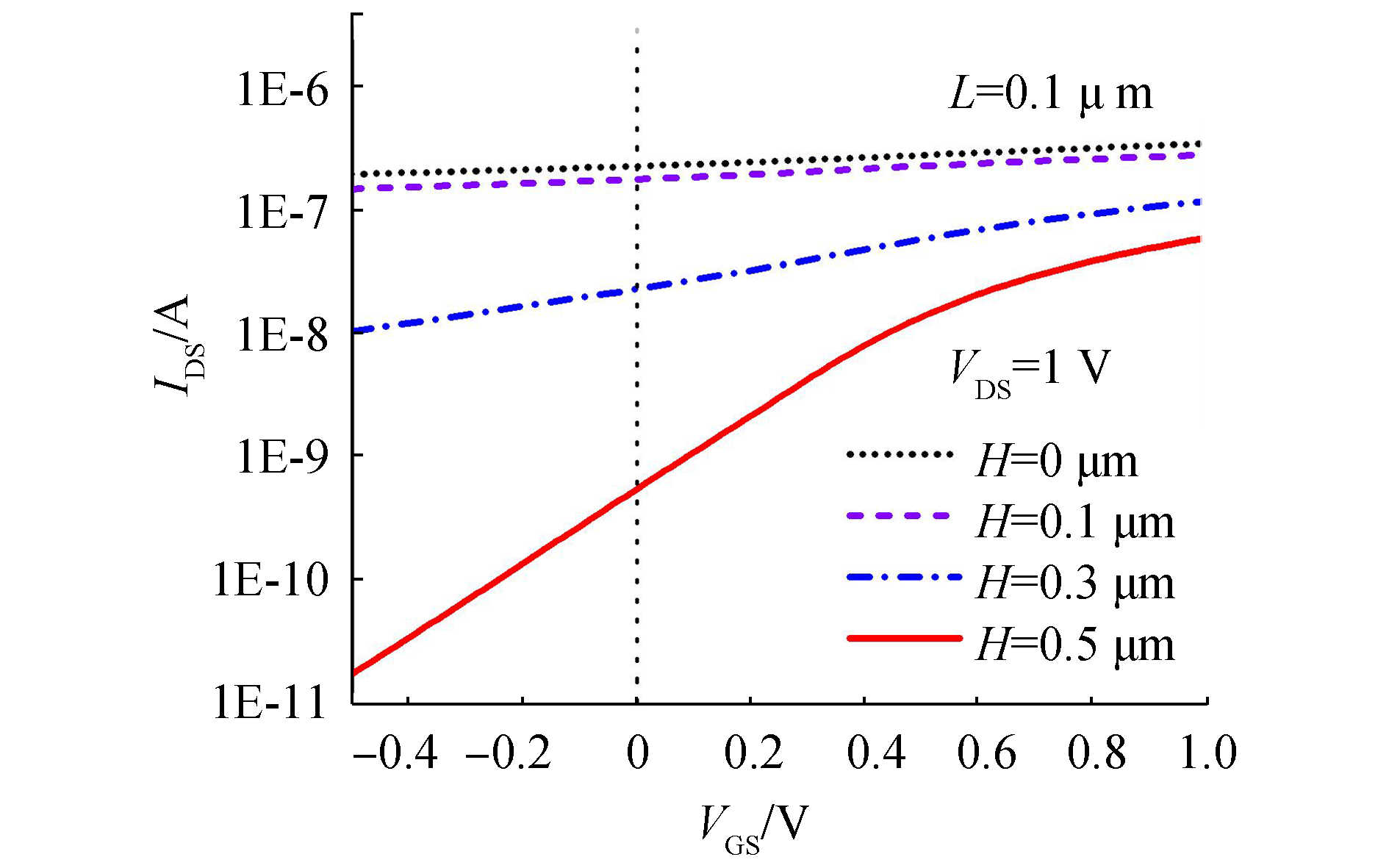

对于低功耗的电路或系统来说,晶体管的漏电情况尤为关键。图 4为非平面沟道晶体管与常规晶体管的输入特性对比。从图中可以看出,常规器件在沟道长度为0.1μm时发生了严重的源漏穿通效应,其转移特性已经完全偏离了长沟器件的转移特性曲线。而对于非平面沟道晶体管来说,其转移特性随着垂直距离的提高而逐渐变好,可以看到在垂直距离为0.5μm时,器件的转移特性与长沟器件十分接近。因此该结构可以有效地改善短沟道效应。

|

Download:

|

| 图 4 不同垂直距离下的转移曲线 | |

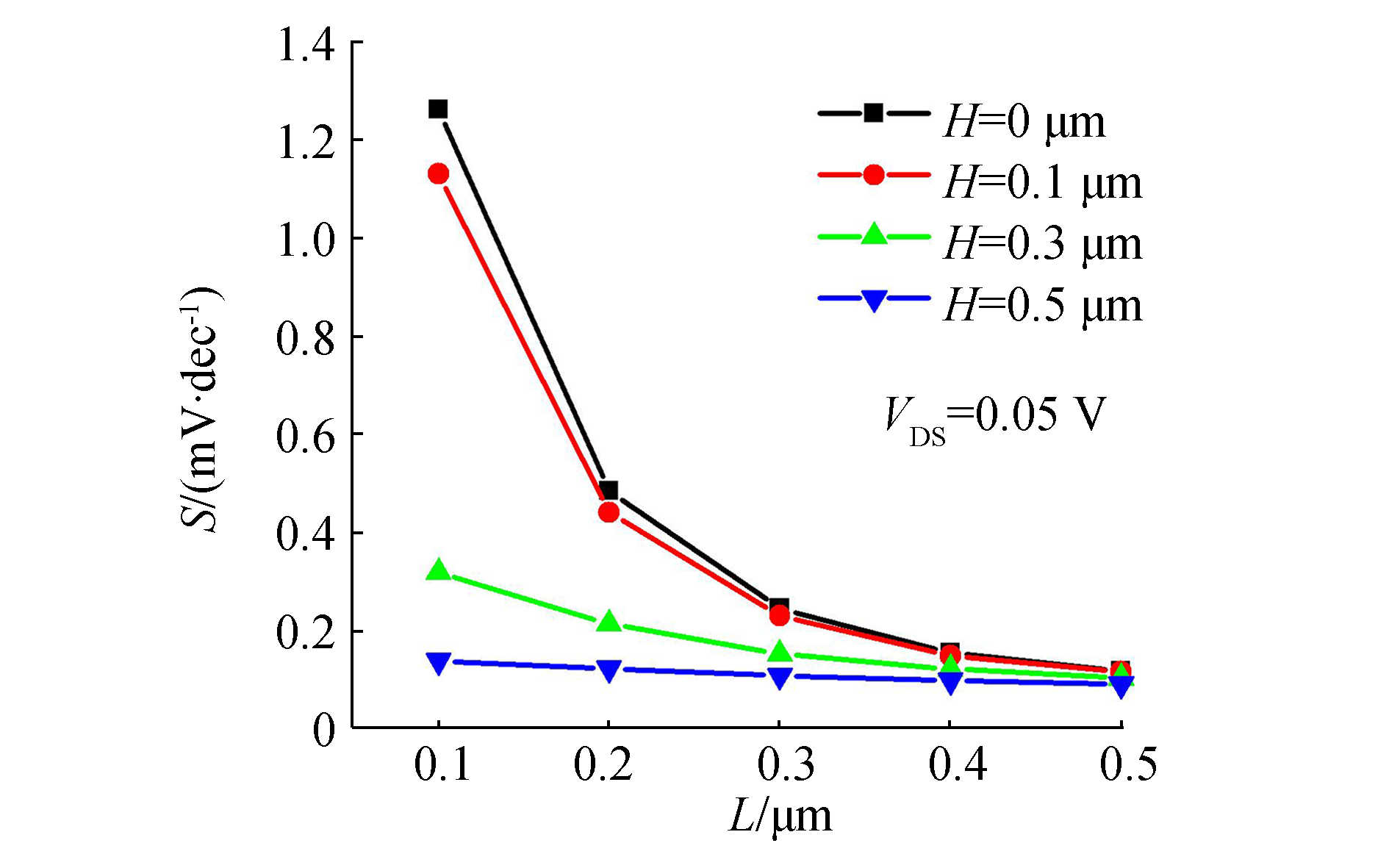

图 5为亚阈值斜率的变化情况对比,亚阈值斜率表征器件的栅极控制能力,亚阈值斜率越低表示栅极控制能力越强,因此亚阈值斜率的大小可以反映出器件的漏电情况。从图中可以看出,对于常规MOSFET,它的亚阈值斜率随着沟道长度的缩小而急剧增大,这意味着其亚阈值特性变得很差,也就是说常规MOSFET的栅极控制能力随着沟道的缩短而逐渐下降。对于非平面沟道晶体管而言,可以看出当垂直距离为0.1 μm时对于亚阈值斜率改善微乎其微,但当垂直距离在0.3 μm时,随着沟道的缩短,亚阈值斜率只是小幅度的上扬。在垂直距离为0.5 μm时,亚阈值斜率几乎没有发生变化,这表明非平面沟道晶体管的亚阈值特性相较于常规晶体管得到了明显的改善。从而说明了该结构对于器件的栅控能力有了极大的增强,器件的漏电情况得到了改善。

|

Download:

|

| 图 5 同垂直距离下的亚阈值斜率变化情况 | |

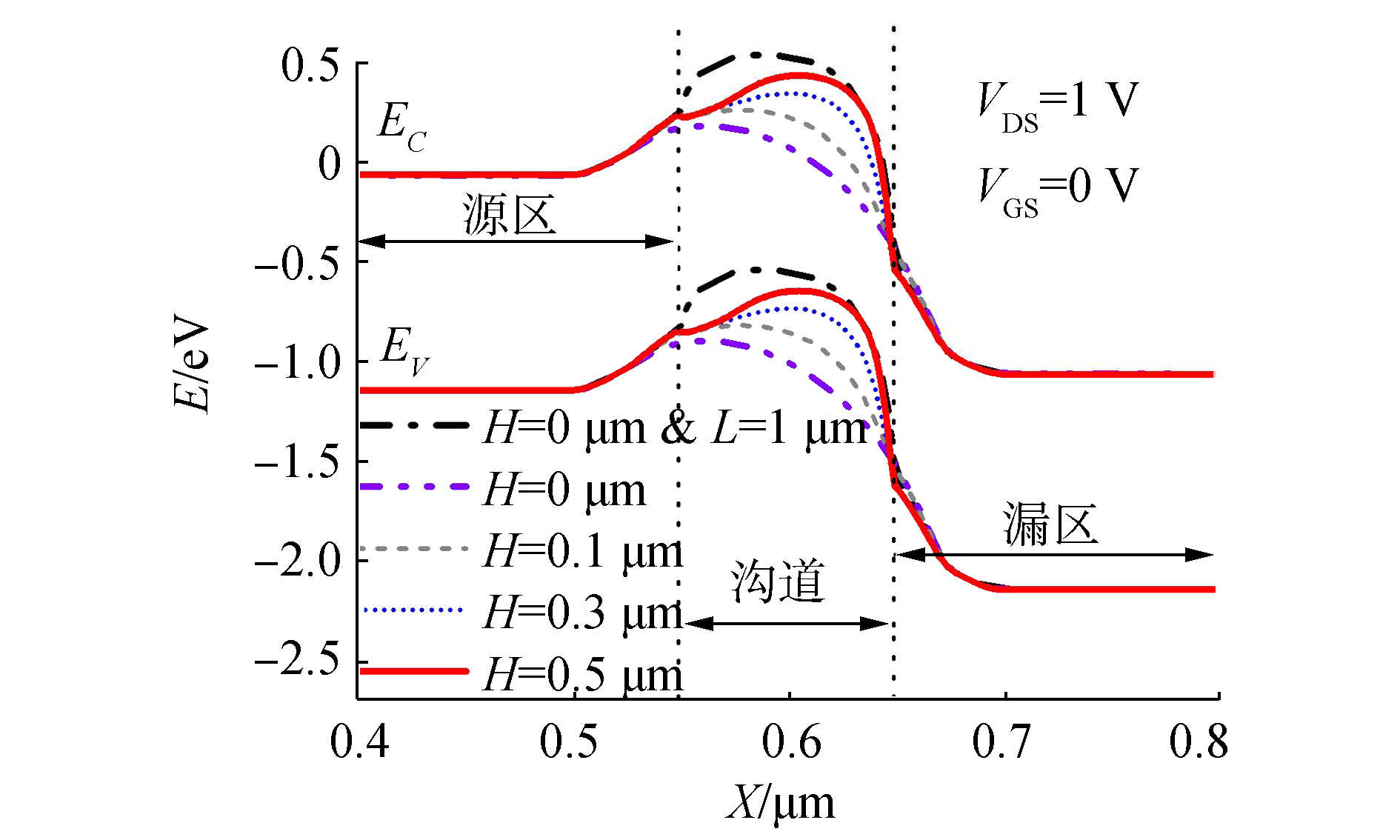

器件漏电的根本原因是势垒降低,导致载流子可以更加轻易地越过PN结的势垒到达沟道区形成漏电流。而短沟道将会引起源端的势垒降低,也即漏致势垒降低效应。漏致势垒降低效应是由于漏区的电势线影响到沟道区的电势分布,降低了源端的势垒,从而导致器件的栅极控制能力下降,漏电流增加。图 6为不同器件结构的能带图,对比了沟道长度为1 μm的常规器件和沟道长度为0.1 μm下的不同垂直距离时的能带分布,从图中可以发现,常规晶体管在短沟道的情况下电子势垒比长沟道的情况下的源区势垒低很多,因此电子可以更容易地越过势垒注入到沟道中形成漏电流,而非平面晶体管的在沟道区中的能带有了很大的提高,这说明了非平面沟道晶体管可以增大器件在关断时的势垒高度,继而说明该结构可以有效抑制漏致势垒降低效应,使得载流子需要更多的能量才能跨越势垒进入沟道,也即器件更难漏电,这就解释了新结构可以降低了漏电流的原因。

|

Download:

|

| 图 6 不同垂直距离下的能带 | |

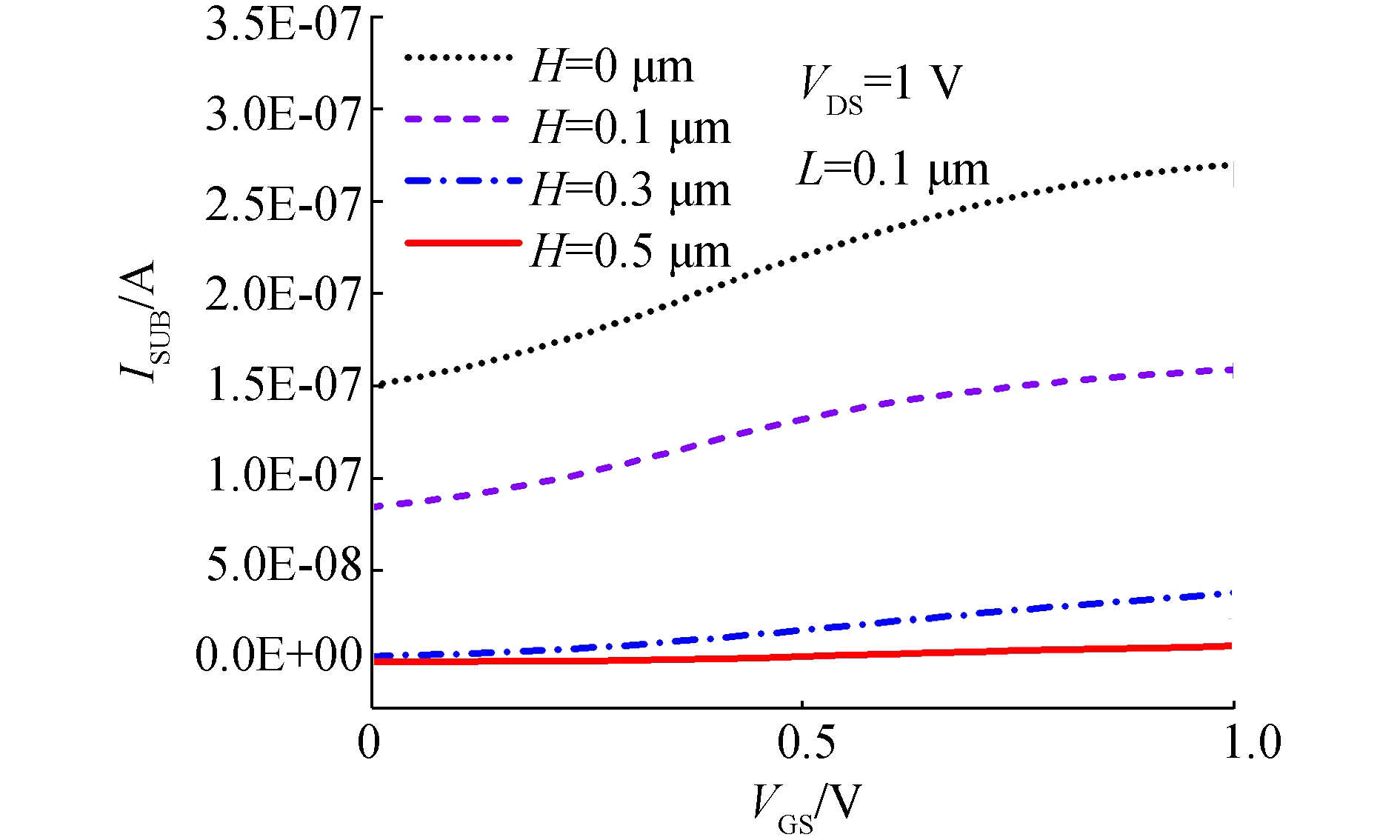

图 7为不同结构下器件衬底电流的大小对比。可以看出,新结构在对衬底电流的抑制作用同样十分明显。由于漏区的高电场,载流子在该区域极易获得高能量从而形成热载流子,该热载流子可以穿过栅氧层到达栅极形成栅电流,也可以形成碰撞电离产生电子空穴对,从而形成衬底电流。该效应会降低器件的可靠性,因此要解决这一问题,可以从降低漏区电场峰值的角度考虑。

|

Download:

|

| 图 7 不同垂直距离下的衬底电流 | |

图 8为表面电场分布对比,图中对比了沟道长度为1 μm的常规器件和沟道长度为0.1 μm的不同垂直距离时的电场分布。

|

Download:

|

| 图 8 不同垂直距离下的电场分布 | |

对于非平面沟道晶体管来说,其栅氧层是非水平的,在靠近漏区的一侧存在着拐角,由于电场集中效应,在该点将会形成电场峰值[13]。在外加相同的漏极电压时,电场的积分即电势也应该是相同的,由于在非平面沟道晶体管中引入了新的电场峰值,因此漏端电场峰值将会降低。器件仿真结果也证实了该推论,从图中可以看出,新结构的电场峰值要较常规结构更低。峰值电场的降低将抑制热载流子的生成和碰撞电离的发生,降低了衬底电流的生成,从而增强了器件的可靠性。

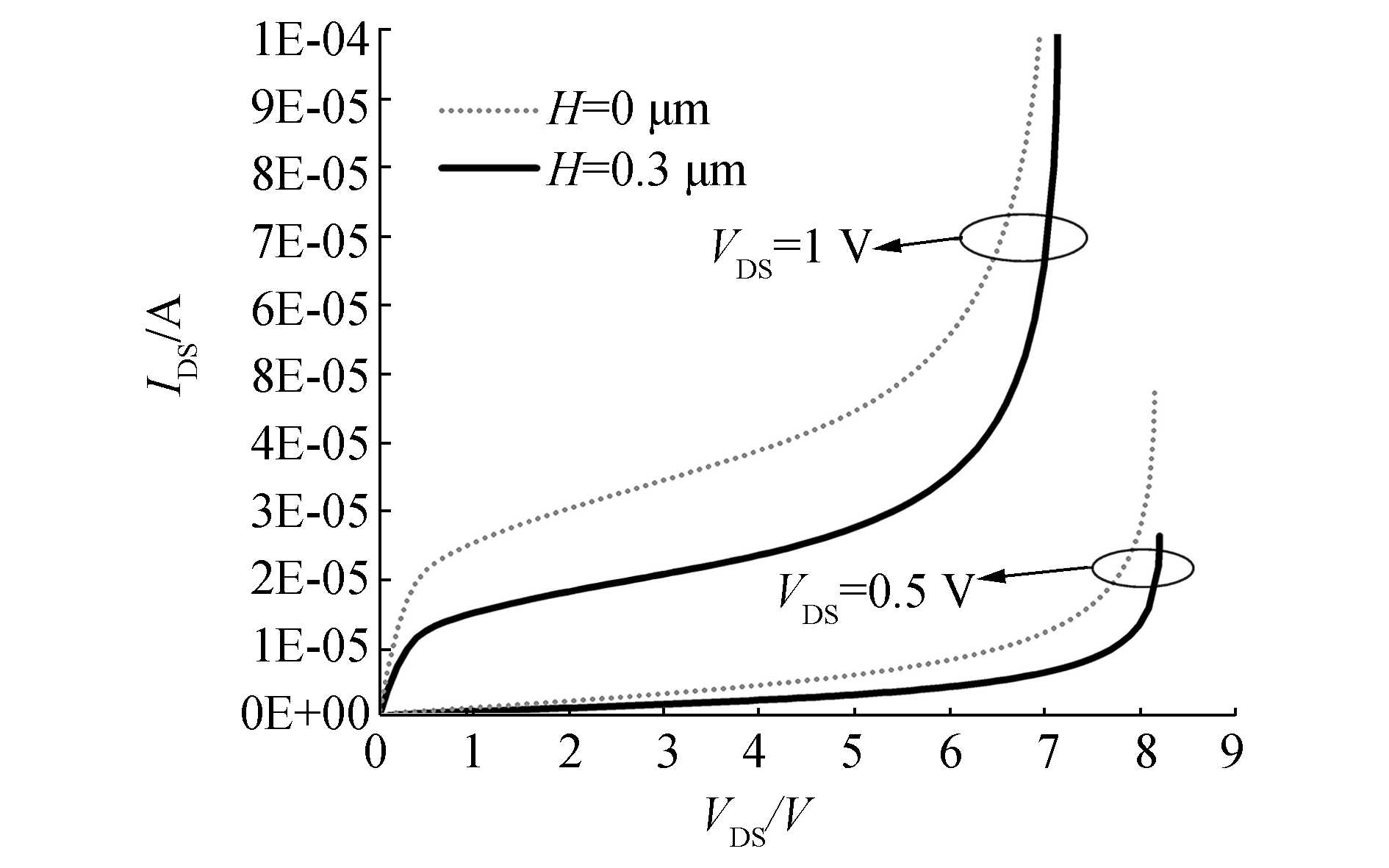

2.4 击穿特性图 9为不同结构下器件的击穿特性对比图,从图中可以发现,非平面沟道晶体管可以有效地提高器件的击穿电压。其改善的机理和对衬底电流改善的机理相同,都是由于漏区电场峰值的降低。新结构器件对于击穿电压的改善,使得器件的可靠性得到了进一步提高。

|

Download:

|

| 图 9 不同器件结构的击穿特性 | |

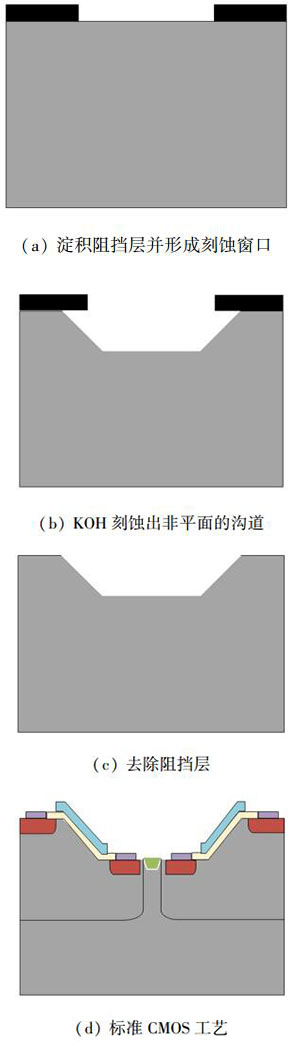

为了制备具有非平面沟道的新结构器件,设计了与标准CMOS相兼容的工艺,如图 10所示。首先,在硅片表面淀积一层Si3N4作为阻挡层;接着进行光刻暴露出刻蚀所需的窗口;然后借助KOH刻蚀硅的各向异性的特点,刻蚀出所需的非平面沟道结构;接着去除阻挡层,形成非平面的沟道;最后使用标准CMOS工艺,进行栅氧及栅极的淀积、离子注入和源漏电极的淀积。

|

Download:

|

| 图 10 非平面沟道场效应晶体管工艺流程 | |

本文提出了一种非平面沟道晶体管,并利用二维器件仿真软件SILVACO对其阈值电压、亚阈值特性、衬底电流、能带、电势和电场分布情况进行了仿真分析。结果表明:

1) 非平面沟道晶体管可以增加器件有效沟道距离,降低了漏区对沟道区的影响,提高了器件在亚阈值区的性能,改善了短沟道效应。

2) 通过引入新的电场峰值,降低漏区的高电场,减少了热载流子的生成,改善了衬底电流并提高了击穿电压,从而增强了器件的可靠性。

| [1] |

SINHA S, YERIC G, CHANDRA V, et al. Exploring sub-20nm FinFET design with predictive technology models[C]//Proceedings of the 49th Annual Design Automation Conference. San Francisco, CA, USA, 2012: 283-288.

( 0) 0)

|

| [2] |

NATARAJAN S, AGOSTINELLI M, AKBAR S, et al. A 14nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0. 0588μm2 SRAM cell size[C]//Proceedings of 2014 IEEE International Electron Devices Meeting. San Francisco, CA, USA, 2014: 371-373.

( 0) 0)

|

| [3] |

WU C C, LIN D W, KESHAVARZI A, et al. High performance 22/20nm FinFET CMOS devices with advanced high-K/metal gate scheme[C]//Proceedings of 2010 International Electron Devices Meeting. San Francisco, CA, USA, 2010: 2711-2714. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=5703430

( 0) 0)

|

| [4] |

WU S Y, LIN C Y, CHIANG M C, et al. A 16nm FinFET CMOS technology for mobile SoC and computing applications[C]//Proceedings of 2013 IEEE International Electron Devices Meeting. Washington, DC, USA, 2013: 911-914. http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=6724591

( 0) 0)

|

| [5] |

KOJIRI T, SUWA T, HASHIMOTO K, et al. Introduction of a high selectivity etching process with advanced SiNx etch gas in the fabrication of FinFET structures[J]. ECS transactions, 2016, 72(4): 23-30. DOI:10.1149/07204.0023ecst ( 0) 0)

|

| [6] |

JENA B, DASH S, MISHRA G P. Electrostatic performance improvement of dual material cylindrical gate MOSFET using work-function modulation technique[J]. Superlattices and microstructures, 2016, 97: 212-220. DOI:10.1016/j.spmi.2016.06.024 ( 0) 0)

|

| [7] |

GOEL E, KUMAR S, SINGH K, et al. 2-D analytical modeling of threshold voltage for graded-channel dual-material double-gate MOSFETs[J]. IEEE transactions on electron devices, 2016, 63(3): 966-973. DOI:10.1109/TED.2016.2520096 ( 0) 0)

|

| [8] |

GHOSH P, HALDAR S, GUPTA R S, et al. An analytical drain current model for dual material engineered cylindrical/surrounded gate MOSFET[J]. Microelectronics journal, 2012, 43(1): 17-24. DOI:10.1016/j.mejo.2011.10.001 ( 0) 0)

|

| [9] |

COLINGE J P, LEE C W, AFZALIAN A, et al. Nanowire transistors without junctions[J]. Nature nanotechnology, 2010, 5(3): 225-229. DOI:10.1038/nnano.2010.15 ( 0) 0)

|

| [10] |

CHOI W Y, LEE W. Hetero-gate-dielectric tunneling field-effect transistors[J]. IEEE transactions on electron devices, 2010, 57(9): 2317-2319. DOI:10.1109/TED.2010.2052167 ( 0) 0)

|

| [11] |

GHOSH B, MONDAL P, AKRAM M W, et al. Hetero-gate-dielectric double gate junctionless transistor (HGJLT) with reduced band-to-band tunnelling effects in subthreshold regime[J]. Journal of semiconductors, 2014, 35(6): 064001. DOI:10.1088/1674-4926/35/6/064001 ( 0) 0)

|

| [12] |

YADAV D S, SHARMA D, RAAD B R, et al. Dual workfunction hetero gate dielectric tunnel field-effect transistor performance analysis[C]//Proceedings of the 2016 International Conference on Advanced Communication Control and Computing Technologies. Ramanathapuram, India, 2016: 26-29. http://ieeexplore.ieee.org/document/7831593/

( 0) 0)

|

| [13] |

CONTI F, CONTI M. Surface breakdown in silicon planar diodes equipped with field plate[J]. Solid-state electronics, 1972, 15(1): 93-105. DOI:10.1016/0038-1101(72)90070-6 ( 0) 0)

|

2018, Vol. 45

2018, Vol. 45