2. 中国科学院大学 微电子学院, 北京 100029

2. School of Microelectronics, University of Chinese Academy of Sciences, Beijing 100029, China

流水线模数转换器(analog digital converter, ADC)是一种能实现高速高精度的模数转换器,被广泛应用于通信系统和互补金属氧化物半导体(complementary metal-oxide-semiconductor transistor,CMOS)图像传感器中。传统的ADC[1]功耗分析中,跨导运算放大器(operational transconductance amplifier,OTA)占了模拟域功耗的主要部分,因此, 设计高性能的OTA对整个ADC来说至关重要。随着CMOS工艺的不断发展,尤其当电源电压降低到1V以下时,晶体管的本征增益迅速下降,OTA的输出摆幅也严重受限。为了解决传统的OTA的性能已经落后于低功耗的设计需求,文献[2-9]提出了一系列解决方案。Shin等[2]提出了过零检测技术,用比较器控制电流源为电容充放电,充分利用了开关电容高效率充放电特性,但这种结构的控制较为复杂,难以实现高精度。Gregoire等[3]提出了相关电平位移技术,引入了一相时钟,并且增加每级的输出电容,但容易影响信号的建立精度。Hershberg等[4]提出了一种的环形放大器,放大器动态工作时,输出能快速锁定到一个固定电压,表现出跨导运算放大器的特性,但这种结构对内部失调电压VOS比较敏感,可能会引起环形放大器会震荡。Lim等[5]采用多晶硅电阻产生内部失调电压,并使用高阈值器件,提高了环形放大器的稳定性。但这种结构的电源抑制特性较差,而且单端工作时,系统的共模抑制能力较差,偶次谐波失真也比全差分结构大。为了解决文献[2-5]问题,本文提出了一种全差分环形放大器,并对所提出的结构作了验证。

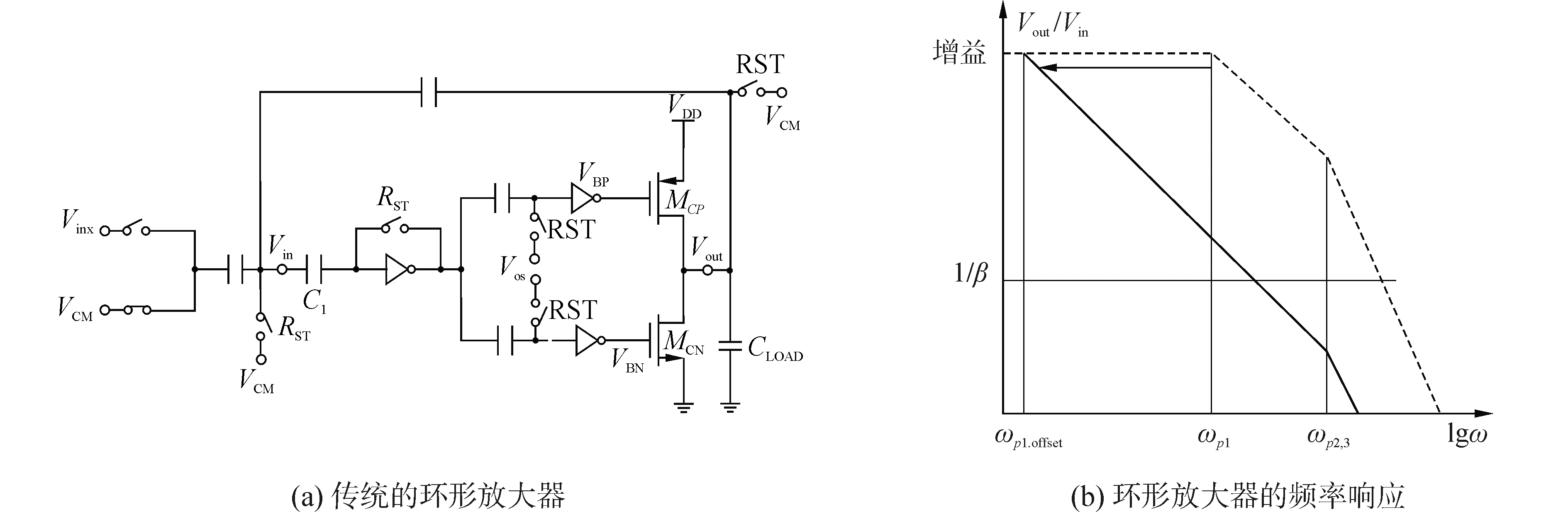

1 环形放大器的工作原理与传统的运算放大器相比,环形放大器[4]是一种新型高能效高摆幅的放大器。简单的环形放大器结构是基于三级反相器级联的环形振荡器,其中第1级反相器输出裂开并在第2级引入内部失调电压。如图 1所示,电容C1的作用是自动调零,即存储输入共模电压(Vcm)和第1级反相器的翻转电压差,以消除Vcm对该电压差的影响,这个电压会在复位时产生周期性的刷新。3级反相器的级联能提供很高的开环增益,而内部失调电压(VOS)保证合适的偏置电压VBP和VBN,使得MOS管MCP和MCN工作在亚阈值区,输出阻抗急剧增大,这样主极点和次主极点的频率相差巨大,系统趋于稳定。放大器的频率响应如图 1(b)所示。由于MCP和MCN工作在亚阈值区,输出Vout几乎能分别达到电源轨和地轨,它的开环增益可以达到80 dB以上,能满足10~12 bit的精度要求;同时,由于它的充放电效率非常高,近似于一个低阻抗的开关充放电,所以它能满足高速应用。

|

Download:

|

| 图 1 传统环形放大器和频率响应 Fig. 1 Conventional ring amplifier and frequency response | |

这种放大器的工作强烈依赖于内部失调电压VOS。如果VOS过小,即VBP和VBN相差较小,MCP和MCN进入线性区,输出阻抗变小。当Vin=Vcm时,放大器相位裕度变小,小的过冲即引发持续震荡;如果VOS过大,MCP和MCN可能会进入截止区,则放大器的带宽降低,不能在指定的时间内完全建立。当考虑工艺角、温度、电源电压等因素时,VOS可能超出正常工作范围,放大器工作会变得异常。

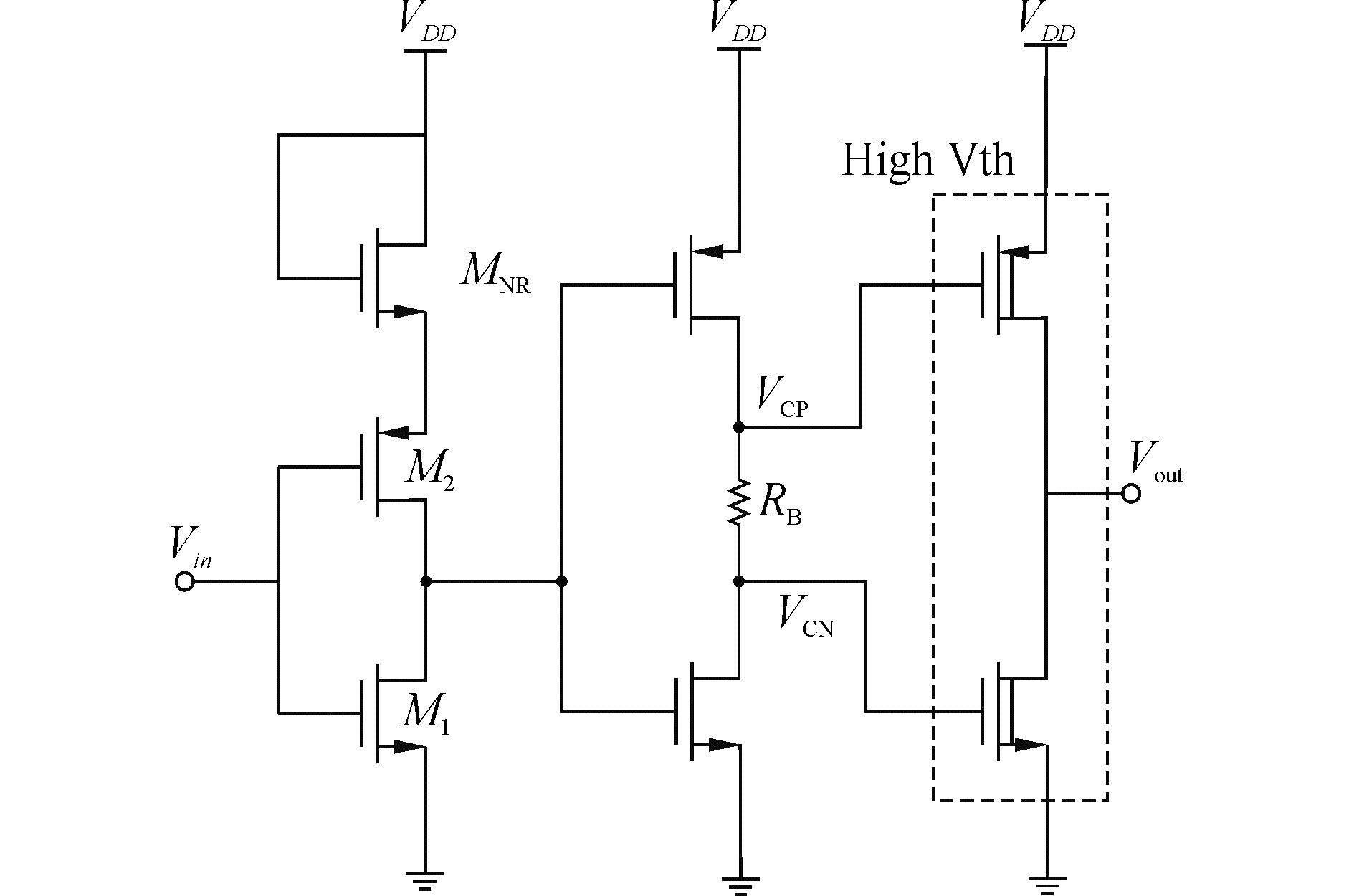

为了解决以上变化引起的问题,同时扩大VBP和VBN的工作范围,文献[5]提出了一种解决方案并简化了放大器的结构。如图 2所示,它在第2级反相器的输出端引入了电阻RB,RB两端的电压差VOS(即VCP-VCN)作为内部失调电压;同时,在输出级引入了高阈值器件。由环形放大器的工作原理[3]可知,只要VOS满足:

| $ {{V}_{\text{THN}}}+\left| {{V}_{\text{THP}}} \right|+{{V}_{\text{OS}}}>{{V}_{\text{DD}}} $ | (1) |

|

Download:

|

| 图 2 本文提出的环形放大器结构 Fig. 2 The proposed ring amplifier structure | |

式中:VTHN和VTHP分别是MCN和MCP的阈值电压,MCN和MCP工作在亚阈值区。由于采用了高阈值器件和自偏置VOS,VTHN和|VTHP|都较大,容易满足条件式(1),因此,这种方案能提高环形放大器的鲁棒性。此外,高阈值器件的引入也提高了输出阻抗,使环形放大器的开环增益得到进一步提升。二极管连接的MNR是为了考虑功耗和噪声的折衷。然而,这种单端结构的共模抑制特性和电源抑制特性依然较差。与传统的反相器相比,电源的扰动依然能直接作用到PMOS管M2的源端,放大器对电源的扰动几乎没有抑制作用;此外,MNR上的压降VGS较大,文献[5]中采用65 nm工艺,这个VGS值约为0.4 V,输入管的跨导和电流可以较好的折衷;但对于0.18 μm工艺,VGS的值约为0.65 V,要获得同样大小的跨导,输入管的尺寸会变的很大,而过大的尺寸会导致输入寄生电容,进而对ADC的精度造成影响。

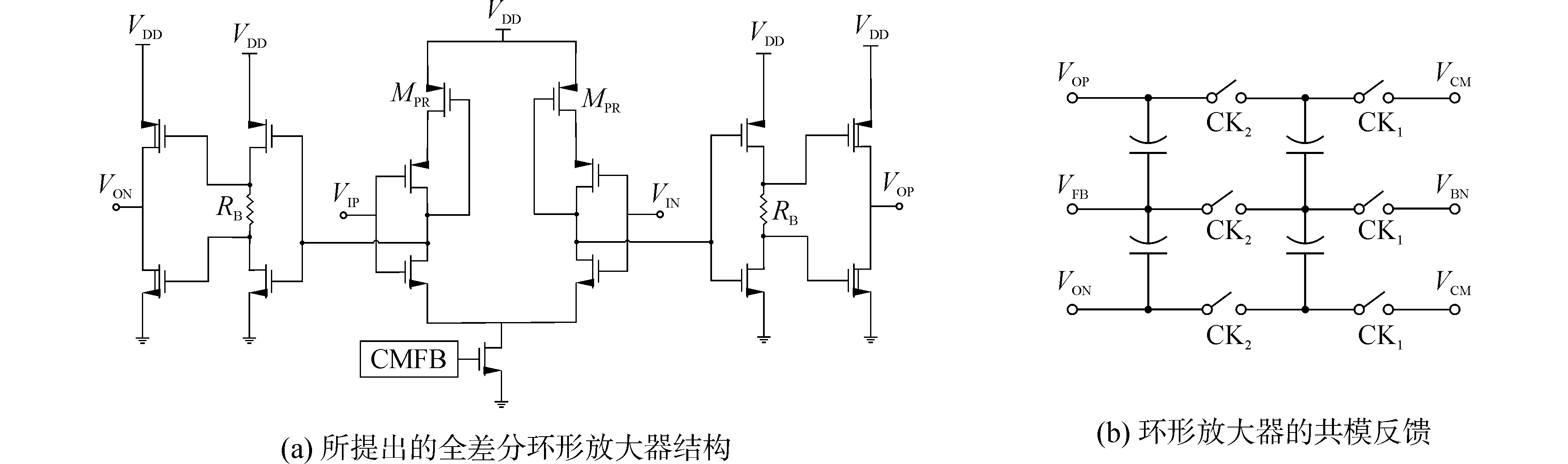

2 环形放大器设计为解决文献[5]中环形放大器的问题,本文提出了一种环形放大器结构。如图 3所示,用PMOS管MPR取代了图 2中的NMOS管MNR,并在第1级的输出引入了负反馈。由于MPR的作用,第1级反相器的输出电压不易发生共模漂移。MPR工作在线性区,合理的调节它的尺寸即可以调节第1级反相器的电流和带宽,从而优化第1级反相器的速度和噪声。第一级反相器的等效跨导为:

| $ \begin{array}{l} {G_{{\rm{m,s}}{{\rm{t}}_{\rm{1}}}}} = - \left( {{g_{{{\rm{m}}_1}}} + \frac{{{g_{{{\rm{m}}_2}}}{g_{{{\rm{o}}_{\rm{3}}}}}}}{{{g_{{{\rm{m}}_2}}} + {g_{{{\rm{o}}_{\rm{2}}}}} + {\rm{ }}{g_{{{\rm{o}}_3}}}}}} \right) \approx \\ \;\;\;\;\;\;\;\;\;\;\; - \left( {{g_{{{\rm{m}}_{\rm{1}}}}} + \frac{1}{2}{g_{{{\rm{m}}_{\rm{2}}}}}} \right) \end{array} $ | (2) |

式中:gm1为M1的跨导;gm2为M2的跨导;go3为MPR的导纳;go3的值和gm2的值近似相等。实际设计时,为了获得更高的速度,M1和M2的宽长比(W/L)会尽可能的大,一般取M2的尺寸为M1的2~3倍,以使反相器的翻转尽可能在中间电平。

由于图 2所示的环形放大器是单端输入单端输出,它始终带有单端结构的缺点,如共模抑制特性较差、偶次谐波失真较大、抗噪声能力较弱等。为了解决这一问题,本文进一步提出了一种全差分环形放大器,如图 3所示。相比于文献[4-5]中的伪差分结构,本文所提出的放大器用NMOS差分对取代了原有的2个单端放大器。该放大器的第1级引入了NMOS尾电流源,由于MPR对第1级输出电平具有稳定作用,故而第1级无需额外的共模反馈;第2级反相器的增益较低,共模电平变化较小,不需使用共模反馈;第3级的输出共模反馈采用开关电容电路[10-11],反馈控制端VFB即是尾电流源的栅极。

|

Download:

|

| 图 3 提出的全差分环形放大器以及共模反馈 Fig. 3 The proposed fully differential ring amplifier and common feedback | |

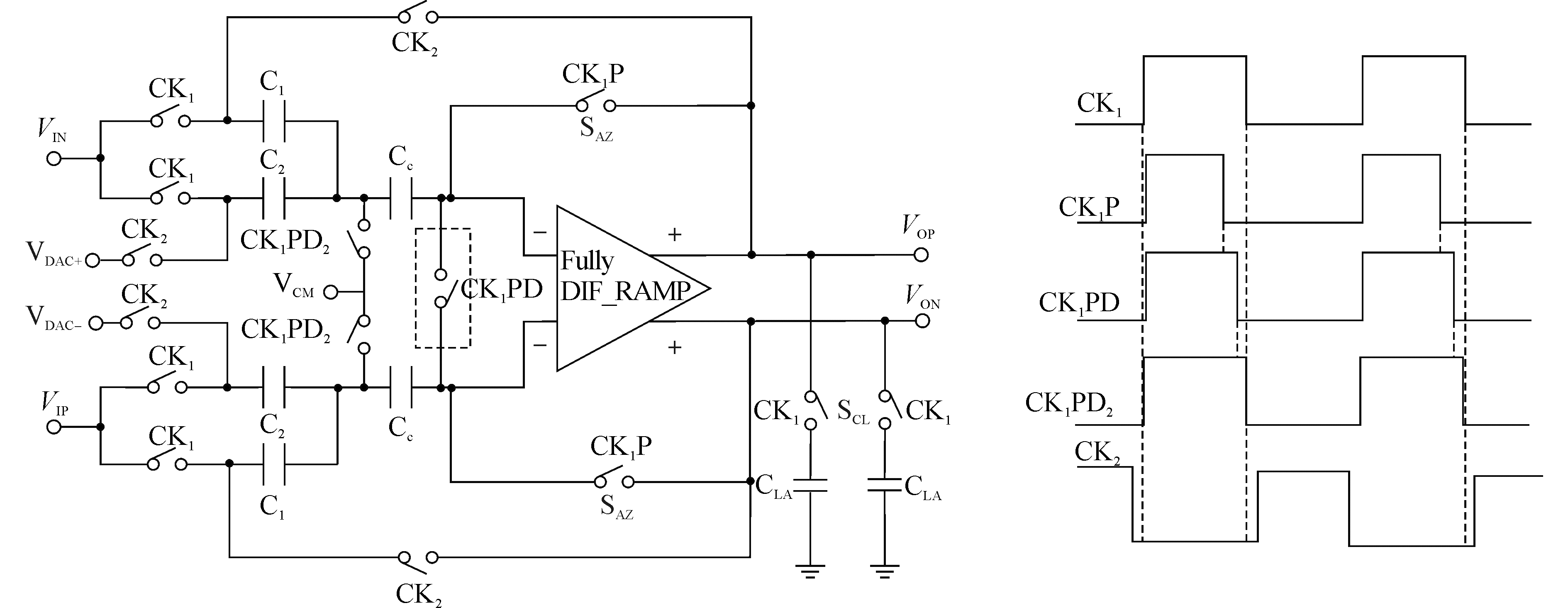

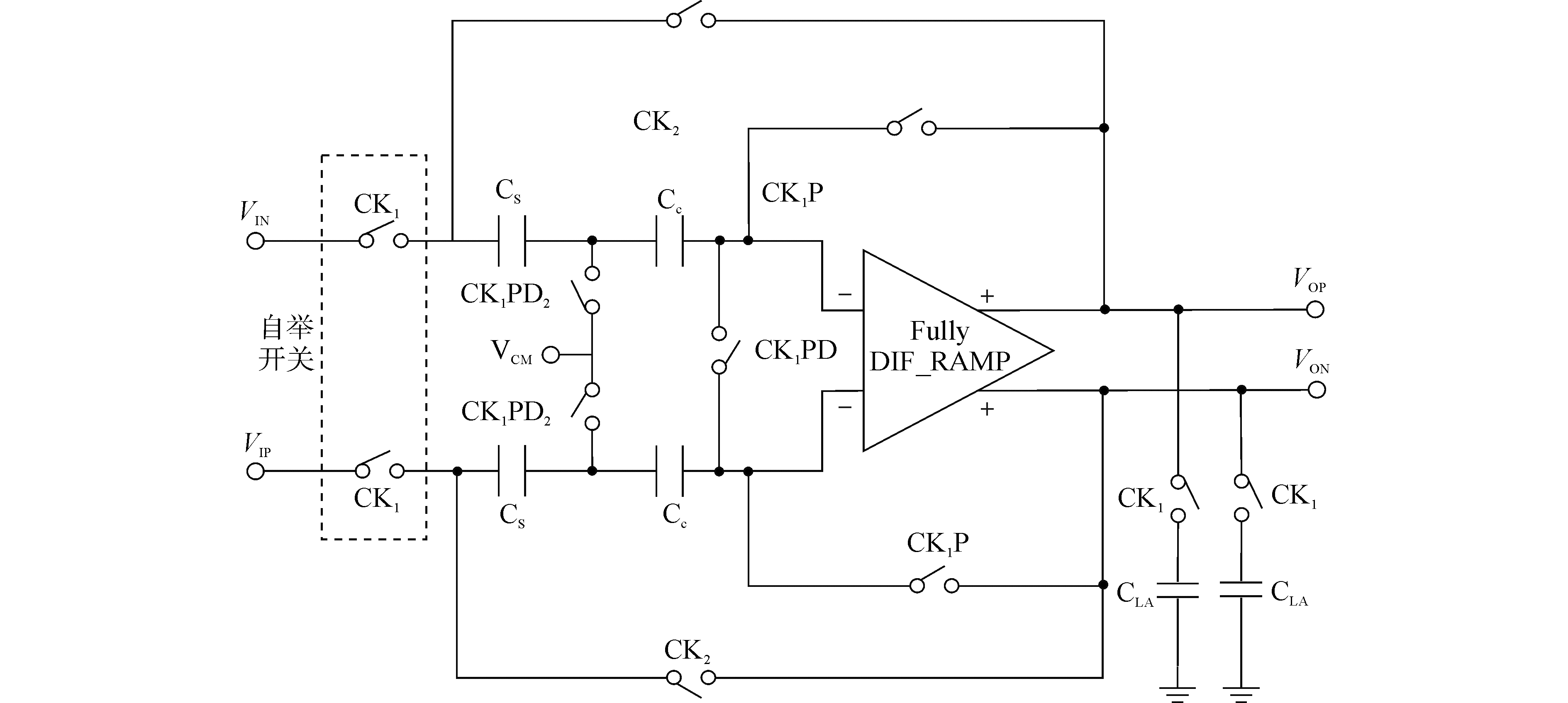

图 4给出的是采用所提出的全差分环形放大器构建的余量增益电路(multiply digital to coalog converter, MDAC)电路结构。MDAC在CK为高时采样,同时环形放大器进行自动调零。由于在采样相时环形放大器的输出等效负载变化较大,存在稳定性问题。为了使放大器在采样相时正常工作,在输出引入了开关SCL和电容CLA,以保证放大器在采样相时的等效负载基本不变。开关SAZ在断开时会对电容CC注入电荷,这些电荷会表现为输出失调。为了消除这一失调,本设计引入了开关Sp,它由CK1PD控制,采用适当的时序,可以消除SAZ引入的失调[12]。图 4给出了MDAC中各项时钟的时序图。采样结束后,调零开关SAZ首先断开,然后Sp断开,这使得环形放大器输入端的电位始终近似相等,开关SAZ引入的失调被消除。此后,由CK1PD2控制的开关Sp2断开,最后CK1再断,由于采样开关断开时的注入电荷没有泄放通路,不会对电路产生影响。为了观察MDAC在不同输入幅度时的增益变化,仿真输入了一些直流值,表 1给出了仿真结果。从表 1中可以看出,MDAC能精确的倍乘输入信号,其输出误差在1 LSB(3.125 mV)。

|

Download:

|

| 图 4 本设计中MDAC的电路结构和开关时序 Fig. 4 MDAC structure and switch timing | |

| 表 1 MDAC仿真结果 Table 1 Simulation results of MDAC |

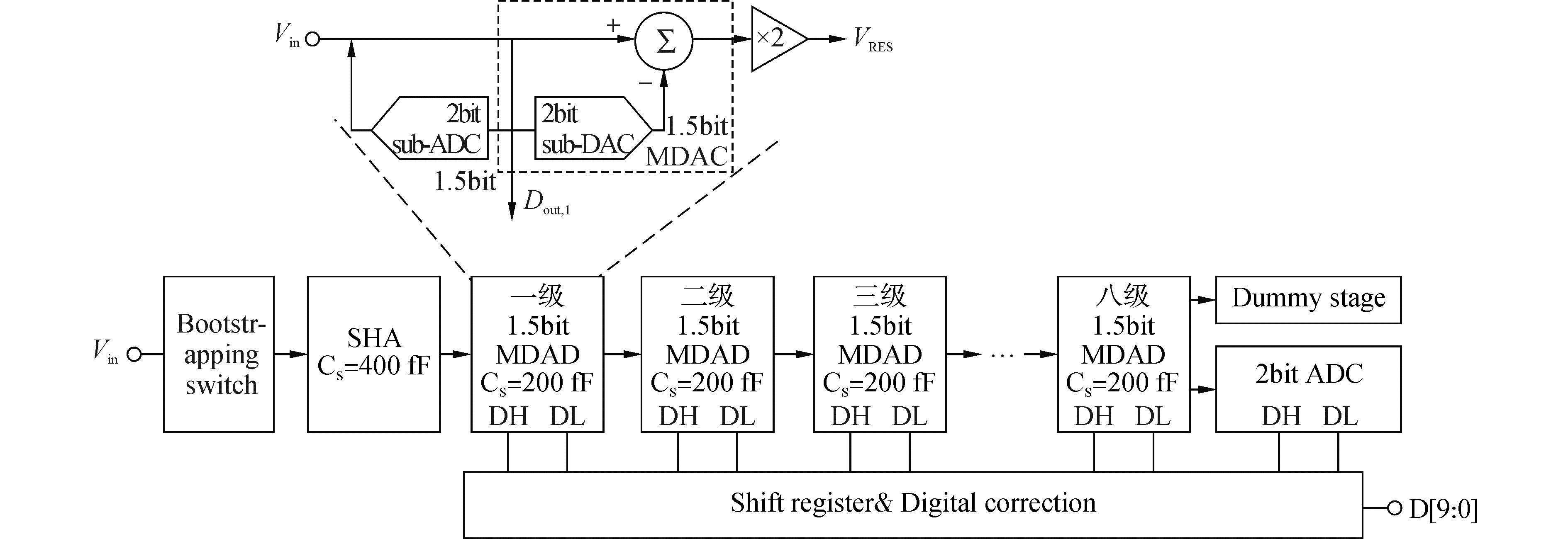

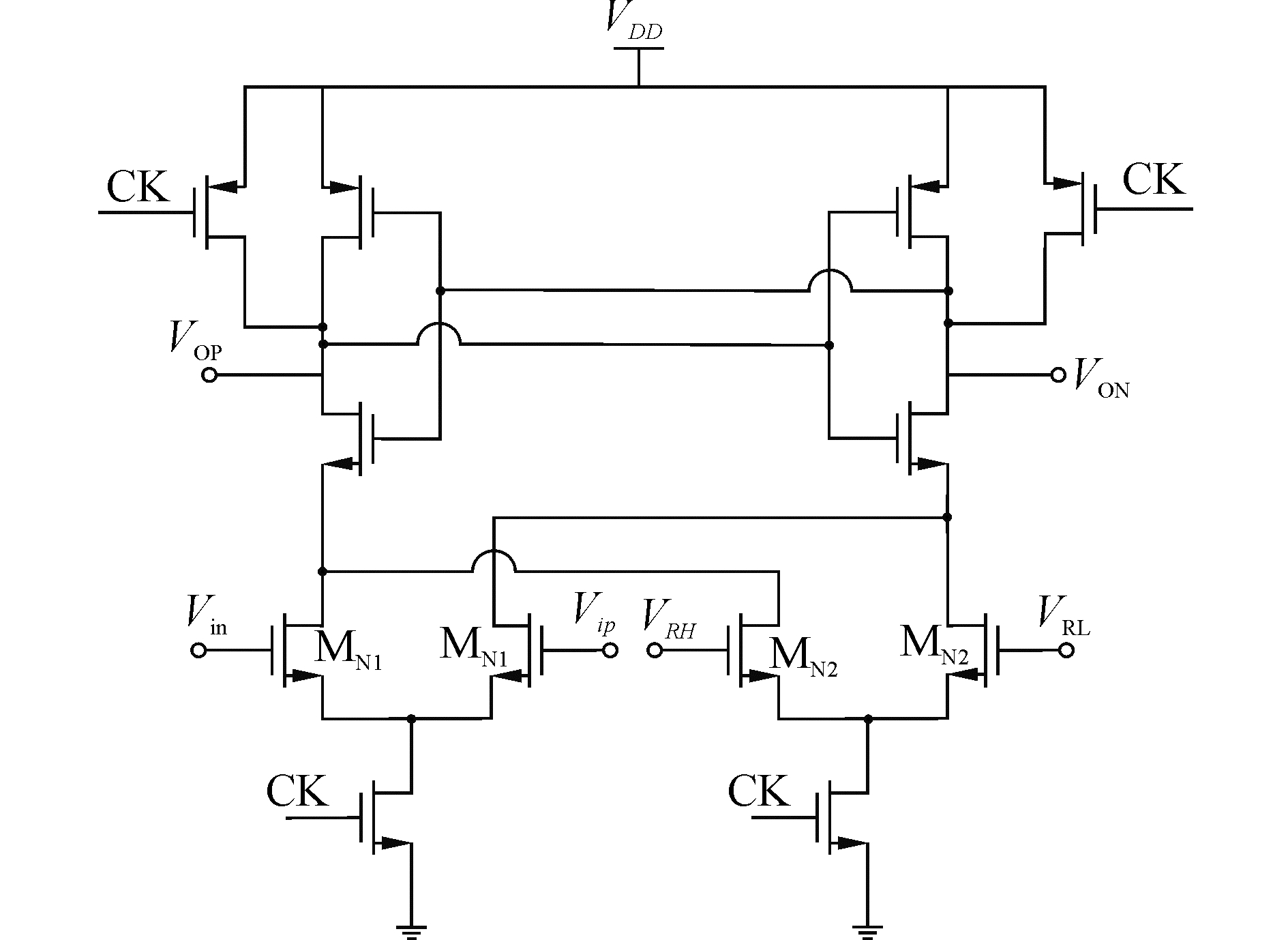

本节采用所提出的放大器结构设计了一款10 bit 40 MS/s流水线ADC。图 5是流水线ADC的整体架构,采用了经典每级1.5 bit的结构。为了避免孔径误差,本设计使用了采样保持器(sample and hold amplifier,SHA)。采样保持器的电路结构如图 6所示,采样电容为400 fF,采用电容翻转式结构,由于反馈系数较大,该结构比电荷重分布式更节省电流。采样开关使用自举开关,以获得更低的导通电阻,采样保持器静态消耗电流约300 μA。ADC每级的MDAC结构与图 4相同,每级的采样电容均为200 fF,前3级的静态时消耗电流约400 μA。由于流水线每级的容忍误差逐级加大,为了降低功耗,分配2~8级每级电流约120 μA,同时增加RB的值,使环形放大器能更快锁定。第8级除了连接最后2 bit ADC外,仍然级联了一个虚拟级,它只接开关和电容,不消耗静态电流,这样第8级在采样和放大时的负载基本一致,环形放大器不会有稳定性问题。Cc的取值不宜过大,也不宜过小,文献[4]指出Cc+CLA>2C1才能保证环路的稳定性,本文取Cc为200 fF。图 7是本设计中的比较器结构,这种比较器在静态时不消耗电流,具有速度快、失调小、功耗低等优点,符合低功耗设计要求。由时钟信号Latch控制的尾电流源可以让输入对管工作在饱和区,这样能降低比较器的失调。为了实现与±0.25 VREF的比较,MN1管的尺寸是MN2管的4倍。VOP和VON为比较器的输出信号,这2个节点对寄生电容较敏感,通常它们会接2个反相器以隔离后级的影响,反相器后再使用SR锁存器,锁存输出给后级使用。由于1.5 bit流水线结构的特点,只要比较器的失调不超过±0.25 VREF,借助数字校正的算法都可以将这种失调引起的误码校正回来。

|

Download:

|

| 图 5 带采样保持器的流水线ADC结构 Fig. 5 Pipeline ADC structure with sample and hold amplifier | |

|

Download:

|

| 图 6 全差分电容翻转式采样保持器 Fig. 6 Fully differential capacitor flip-around SHA | |

|

Download:

|

| 图 7 低功耗动态比较器 Fig. 7 Low power dynamic comparator | |

本设计采用0.18 μm 1P6M 1.8V/3.3V混合信号工艺构建了一个10 bit 40MS/s的流水线ADC,在Cadence ADE spectre平台上进行电路前仿真,并使用Matlab做数据分析。

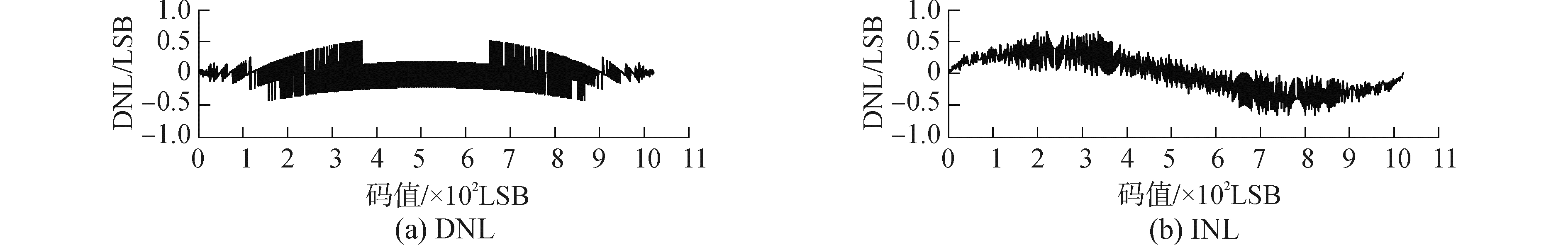

当差分输入一个频率Fin为2.00 195 MHz,幅度为VPP=3.2 V的正弦波信号,采样频率为40 MHz,VDD=1.8 V时,采样4 096个数据点,分析得到ADC的静态特性和动态特性[13-14]。从图 8所示的ADC静态特性仿真结果可以看出,DNL最大值约±0.5 LSB,INL的最大值约±0.65 LSB,对于图像传感器来说,这样的DNL和INL特性满足无失码的要求。仿真得到整个ADC的静态功耗约3.92 mW,平均动态功耗约5.32 mW。

|

Download:

|

| 图 8 ADC的静态特性仿真结果 Fig. 8 ADC static characteristic simulation results | |

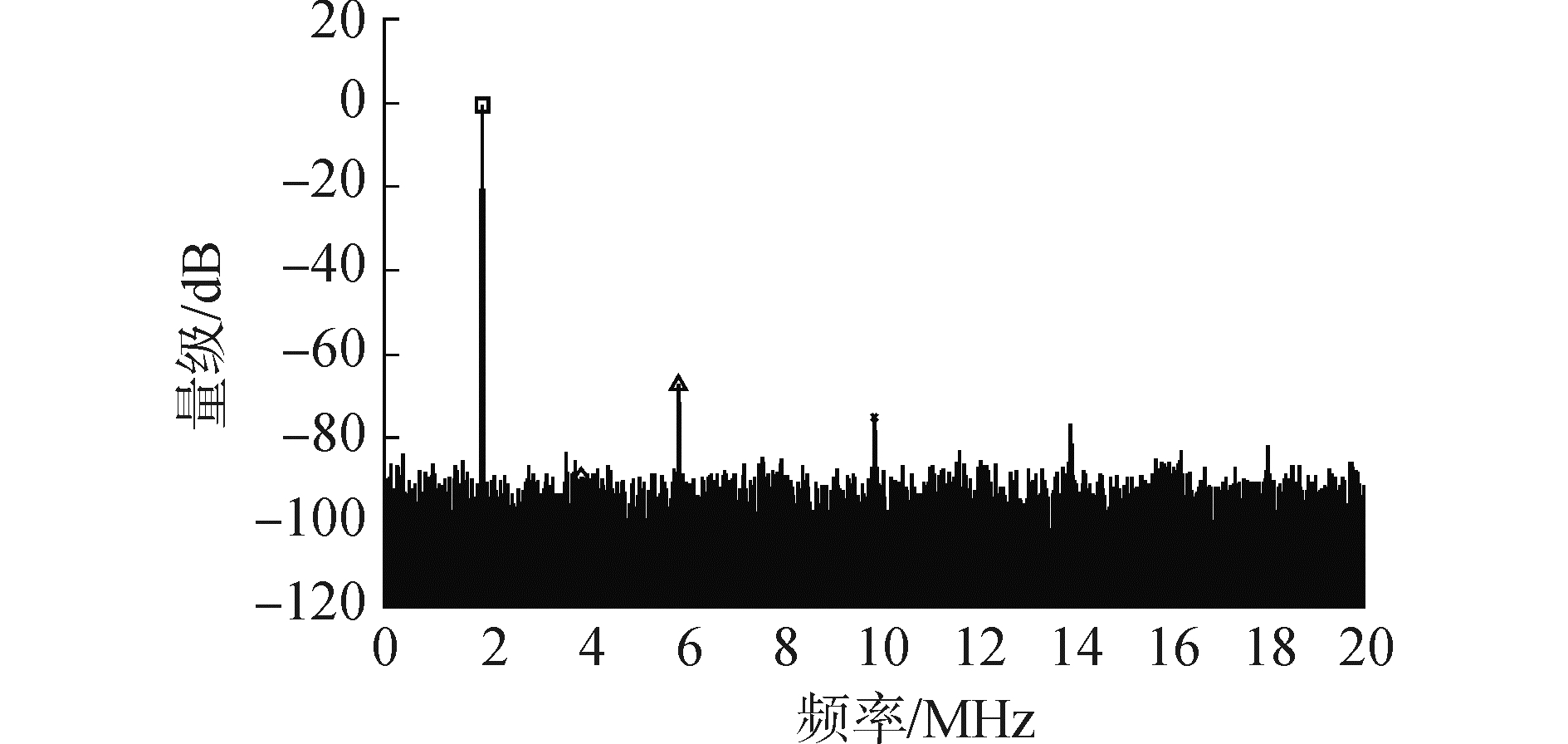

从图 9所示的ADC动态特性仿真结果可以看出,ADC的无杂散动态范围为66.7 dB, 信号噪声失真比为60.4 dB,有效位数约9.74 bit。ADC的品质因数F为ADC在指定的采样频率内完成每一次转换所消耗的,可表示为:

| $ F=\frac{P}{{{2}^{E}}{{f}_{\text{s}}}} $ | (3) |

|

Download:

|

| 图 9 ADC的动态特性仿真结果 Fig. 9 ADC dynamic characteristic simulation results | |

式中:P为功耗;E为有效位数;fs为采样率。从式可以看出,在采样率和精度一定的情况下,功耗越小,F值越低。本设计的F值为152.3 fJ/conv-step。

4 结论1) 仿真结果显示本文所设计的全差分放大器功能完全正常,应用所提出的放大器设计的流水线ADC性能达到了预期设计指标。

2) 对比本设计和近几年文献中流水线ADC的性能指标。可以看出,采用环形放大器的ADC性能明显优于其他结构。本文所设计ADC的品质因数值大于文献[6-9]中的数值。

| [1] |

ABO A M, GRAY P R. A 1.5-V, 10-bit, 14.3-MS/s CMOS pipeline analog-to-digital converter[J]. IEEE journal of solid-state circuits, 1999, 34(5): 599-606. DOI:10.1109/4.760369 (  0) 0)

|

| [2] |

SHIN S K, YOU Yongsang, LEE S H, et al. A fully-differential zero-crossing-based 1.2V 10b 26MS/s pipelined ADC in 65nm CMOS[C]//Proceedings of 2008 IEEE Symposium on VLSI Circuits. Honolulu, HI, USA, 2008: 218-219.

(  0) 0)

|

| [3] |

GREGOIRE B R, MOON U K. An over-60 dB true rail-to-rail performance using correlated level shifting and an opamp with only 30 dB loop gain[J]. IEEE journal of solid-state circuits, 2008, 43(12): 2620-2630. DOI:10.1109/JSSC.2008.2006312 (  0) 0)

|

| [4] |

HERSHBERG B, WEAVER S, SOBUE K, et al. Ring ampliÉers for switched capacitor circuits[J]. IEEE journal of solid-state circuits, 2012, 47(12): 2928-2942. DOI:10.1109/JSSC.2012.2217865 (  0) 0)

|

| [5] |

LIM Y, FLYNN M P. 11.5 A 100MS/s 10.5b 2.46mW comparator-less pipeline ADC using self-biased ring amplifiers[C]//Proceedings of 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers. San Francisco, CA, USA, 2014: 202-203.

(  0) 0)

|

| [6] |

AHMED I, MULDER J, JOHNS D A. A low-power capacitive charge pump based pipelined ADC[J]. IEEE journal of solid-state circuits, 2010, 45(5): 1016-1027. DOI:10.1109/JSSC.2010.2042524 (  0) 0)

|

| [7] |

HERSHBERG B P, WEAVER S T, MOON U K. A 1.4V signal swing hybrid CLS-opamp/ZCBC pipelined ADC using a 300mV output swing opamp[C]//Proceedings of 2010 IEEE International Solid-State Circuits Conference. San Francisco, CA, USA, 2010: 302-303.

(  0) 0)

|

| [8] |

HERSHBERG B, WEAVER S, SOBUE K, et al. A 61.5 dB SNDR pipelined ADC using simple highly-scalable ring ampliÉers[C]//Proceedings of 2012 Symposium on VLSI Circuits. Honolulu, HI, USA, 2012: 32-33.

(  0) 0)

|

| [9] |

RAGAB K, CHEN Long, SANYAL A, et al. Digital background calibration for pipelined ADCs based on comparator decision time quantization[J]. IEEE transactions on circuits and systems Ⅱ:express briefs, 2015, 62(5): 456-460. DOI:10.1109/TCSII.2014.2387532 (  0) 0)

|

| [10] |

RAZAVI B. Operational ampliÉers[M]//AZAVI B. Design of Analog CMOS Integrated Circuits. Boston, MA, USA: McGraw-Hill, 2001: 319-324.

(  0) 0)

|

| [11] |

ENZ C C, TEMES G C. Circuit techniques for reducing the effects of op-amp imperfections:autozeroing, correlated double sampling, and chopper stabilization[J]. Proceedings of the IEEE, 1996, 84(11): 1584-1614. DOI:10.1109/5.542410 (  0) 0)

|

| [12] |

SEPKE T, FIORENZA J K, SODINI C G, et al. Comparator-based switched-capacitor circuits for scaled CMOS technologies[C]//Proceedings of 2006 IEEE International Solid State Circuits Conference-Digest of Technical Papers. San Francisco, CA, USA, 2006: 812-821.

(  0) 0)

|

| [13] |

尹睿.高精度、低功耗流水线型模数转换器的研究与设计[D].上海: 复旦大学, 2010. YIN Rui. A research and design of low power, high resolution of pipeline analog to digital converter[D]. Shanghai: Fudan University, 2010. (  0) 0)

|

| [14] |

谭珺. 3.3伏、100兆采样频率、10比特流水线结构模数转换器的设计和低功耗实现[D].上海: 复旦大学, 2006. TAN Jun.A low power design and implementation of 3.3 V, 100 MSPS/s, 10 bit pipeline analog to digital converter[D]Shanghai: Fudan University, 2006. (  0) 0)

|

2019, Vol. 40

2019, Vol. 40