近年来,随着NAND闪存存储容量的快速增长和成本的大幅下降,以NAND闪存为存储介质的固态硬盘的市场占比已经超过机械硬盘,成为最主要的数据存储设备。NAND闪存存储密度的提升主要依靠半导体制造精度的提升和每单元存储多比特技术的应用。提升半导体制造精度是提高NAND闪存存储密度最直接的办法,但推动生产精度提升所需的投入越来越大,半导体制造工艺的发展已进入瓶颈期。每单元存储多比特的技术能够成倍的提升闪存的存储容量,但是每单元存储的比特数的增多也会使各个状态阈值电压分布更容易产生重叠,导致误码率的增加[1]。

在NAND闪存存储容量的增长速度减慢的同时,当今社会对于存储的需求却与日俱增。因此,为了持续推动NAND闪存存储密度的增大,研究者们提出了3D堆叠技术。不同于以往存储单元只分布在平面上,3D堆叠技术利用了NAND闪存芯片垂直方向上的空间,将存储单元在垂直方向进行堆叠,从而实现即使在使用较老的生产工艺的情况下都能极大地提高NAND闪存的存储容量[2]。3D堆叠技术在使得NAND闪存的存储密度得到极大提升的同时,也导致了NAND闪存的结构更加复杂、信道噪声更加多样,给NAND闪存的可靠性带来了更大的挑战。

2018年,Wu等[3]发现一个块的不同层的字线受到读干扰的影响是非均匀的。2019年,Luo等[4]指出3D NAND闪存相比平面闪存出现3种新的噪声,其中1种为层间制程差异噪声,即不同层的存储单元因为堆叠而产生的物理结构上的差异而产生的噪声。目前对层间制程差异噪声的研究还主要停留在静态的分析上,即在一定的情况下不同层的存储单元的原始误码率的差异。本文对层间差异进行动态的分析,即不同层的原始误码率和阈值电压分布差异随着编程擦除磨损次数和数据保存时间的变化进行了深入分析。

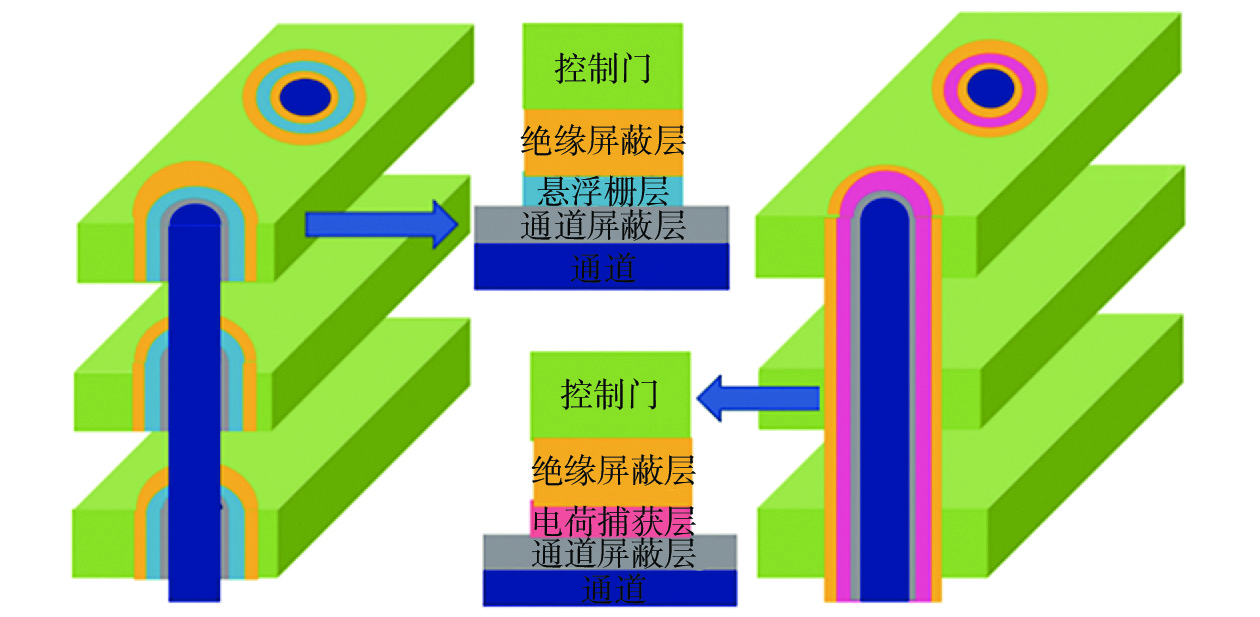

1 3D NAND闪存图1为3D NAND闪存基本存储单元的2种类型,1种是FG型,1种是CT型。2种存储单元都是以圆柱形通道为中心,其他层依次以同心圆的方式一层一层包裹通道,各层从内到外依次是:通道屏蔽层、电荷储存层、绝缘屏蔽层、控制门[5-6]。

|

Download:

|

| 图 1 3D NAND闪存存储单元结构及其组织方式 | |

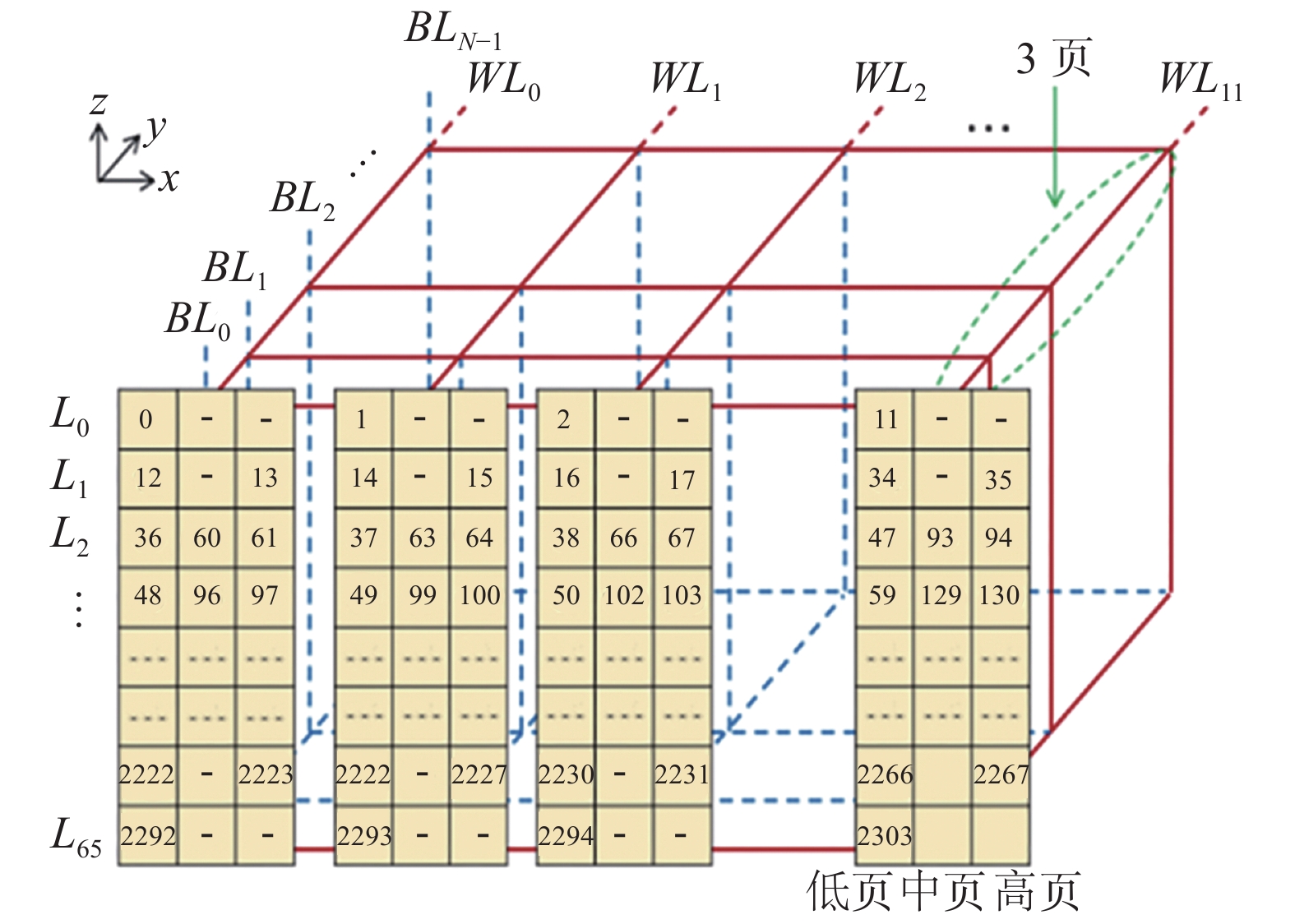

3D NAND闪存的1个块的不同页以一定的规律分布在不同层的不同字线上。1个存储单元存放1 bit、2 bit、3 bit数据分别称为SLC、MLC、TLC类型存储单元,分别对应每个字线划分为1个、2个、3个逻辑页,每个字线的逻辑页以地址高低划分为高页、中页、低页[7]。如图2,堆叠层数为64层、每层有12个字线的3D NAND闪存,其最高和最低的几层因为受到的噪声过大而设计为SLC型或者MLC型,中间的层数为TLC型。MLC类型的层使用单步编程,同时对低页和高页进行编程。TLC类型的层使用两步编程方式,第1步对低页进行编程,第2步对中页和高页进行编程。

|

Download:

|

| 图 2 镁光MT29F1T08EEHAF型号芯片的块结构 | |

由于3D NAND闪存的制作工艺问题,不同层的存储单元在物理结构上存在一定的差异,使不同层的存储单元在特性上产生区别。在3D NAND闪存的制造过程中,需要在垂直方向上构造通道。理想情况下,垂直通道圆柱体不同部位的直径应该是相等的,但是在实际生产中,受重力等因素的影响,层数越高的存储单元的直径会更大。随着3D NAND闪存堆叠层数的不断上升,通道的高度也会上升,通道形变程度也会更加严重[8]。

为了缓解通道的层间差异随着层数的增加而不断增大的问题,闪存生产商使用了串堆叠技术。串堆叠技术在垂直方向上将3D NAND闪存分成多个部分,先对底部的层进行堆叠,然后在已堆叠的层的基础上继续进行堆叠,从而降低每次堆叠的通道的高度,降低了存储单元的层间差异。串堆叠技术虽然解决了层间差异随着层数增加而增大的问题,但是也增加了闪存的加工成本。

2 实验平台与实验设计我们使用NFA100-E闪存芯片测试仪作为实验平台,实现闪存芯片的控制功能。NFA100-E设备有4个独立的通道,能够完成对芯片的擦除、编程、读取、寄存器设置和寄存器读取操作。首先选取测试芯片的一些块作为测试块,并通过实验平台的驱动,将在终端机上生成的测试数据写入到这些测试块中。待对测试芯片进行特定的噪声处理后,对芯片进行扫描并将数据导出到终端机上,进行数据分析。

实验使用的芯片是镁光的3D NAND闪存芯片,其参数如表1所示。

|

|

表 1 实验芯片参数 |

实验芯片为镁光生产的悬浮栅型3D闪存芯片,型号为MT29F081TEEHAF。如图2所示,此型号的芯片在垂直方向上堆叠了66层,中间的62层的存储单元被设计为每单元存储3 bit,上下分别有两层被设计为每单元存储低于3 bit的层,一层为每单元存储1 bit,另一层为每单元存储2 bit。芯片的每个块包含2 304个页,每层有12个字线。此芯片使用了串堆叠技术,分两次对所有的层进行堆叠,首先对下半部分的层进行堆叠,然后在已经完成堆叠的下半部分层之上进行上半部分层的堆叠。

2.1 阈值电压分布扫描方法NAND闪存的存储单元以其存储的电荷量表示存储的数据的值,存储单元存储的电荷量可以表现为阈值电压的大小。因此,可以通过测量存储单元阈值电压的大小从而判断其存储的数据值。每个存储单元的理想状态下的阈值电压应接近一个固定值,但存储单元受到多种噪声和干扰的影响,使存储单元的阈值电压发生不同程度的偏移,存储单元的阈值电压分布呈现一定的模式。

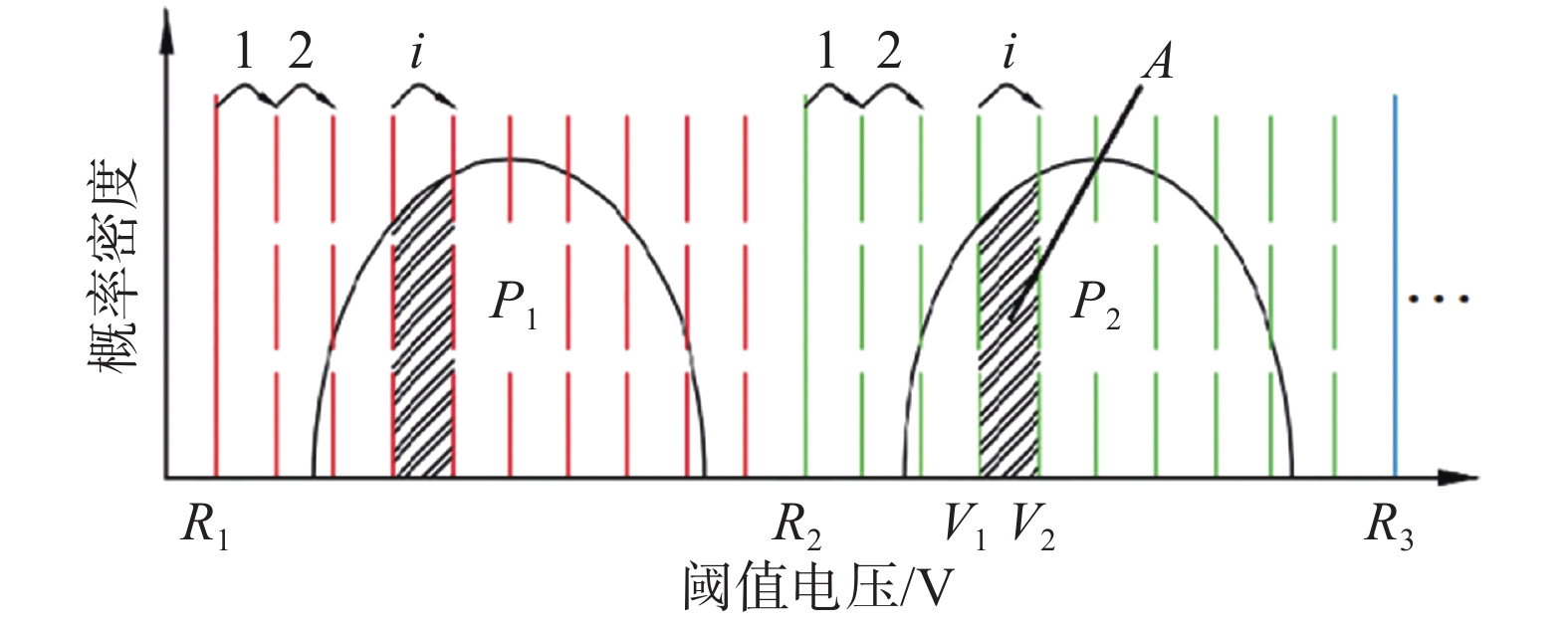

通过闪存芯片的参考电压偏移功能,能够得到存储单元在不同参考电压取值时的状态,判断存储单元的阈值电压所在的区间[9-10]。如图3所示,阈值电压在R1到R2区间内的存储单元的状态为P1,阈值电压在R2到R3区间内的状态为P2,其他状态同理。以阈值电压值在V1到V2区间内,状态为P2的存储单元A为例,在参考电压R2取值小于等于V1,且R3取值大于等于V2时,判决为状态P2;在R2取值大于等于V2,且R1取值小于等于V1时,判决为状态P1。根据R2取值分别为V1和V2时判决状态的差异,则能够判断存储单元的阈值电压取值在V1到V2的区间内。为了获取所有编程状态的阈值电压分布,首先选择1个块写入随机数据;其次,不断重复参考电压偏移和数据读取操作,以得到存储单元在不同参考电压偏移下的读取数据;最后,将读取的数据进行处理,得到每个存储单元阈值电压所在的区间。

|

Download:

|

| 图 3 通过参考电压偏移得到存储单元的阈值电压所在区间 | |

为了能够快速得到芯片在经过长时间电荷泄漏后的性能情况,根据式(1)的阿伦尼乌斯公式计算与芯片常温下的老化时间等效的高温下的老化时间,实现通过对芯片进行高温处理从而加速芯片的老化速度[11]。

| $ k = A{{\rm{e}}^{ - \frac{{{E_a}}}{{RT}}}} $ | (1) |

本实验中使用到的高温等效老化时间如表2所示。

|

|

表 2 高温老化等效时间 |

因为实验芯片的一个块内存在所有层的存储单元,因此我们以块为单位进行测试。经过测试我们发现实验芯片每层的12个字线在误码率和阈值电压分布上的特性基本一致,又因为实验芯片一个块包含的页较多,为了加快测试速度,我们在1个块每层的12个字线中抽取了4个字线进行测试。为了得到不同噪声下的闪存可靠性,我们随机选取一个芯片内的几个块,并磨损到不同的编程擦除循环次数;然后对芯片的几个测试块的所有页写入相同的随机生成数据;最后对芯片进行加热老化,并在老化到测试时间点时对每个块的测试页进行阈值电压扫描。

在获取每个测试点的数据之后,需要对原始误码率和阈值电压分布进行计算。使用默认参考电压下读取出的数据与随机写入数据进行对比,计算得到原始误码率。为了便于后续的分析,使用高斯分布对扫描得到的阈值电压分布进行拟合。使用内德米德单纯形法对扫描得到的分布和构建的高斯分布的均方差进行最小值优化,并使用扫描阈值电压分布的均值和方差作为初值输入,得到拟合的高斯分布参数,最后使用计算得到的高斯分布的参数构建高斯分布作为测试点的阈值电压分布[10,12]。

3 结果分析我们从原始误码率和阈值电压分布2个方面对3D NAND闪存的特性受层间差异的影响进行分析。通过对测试分布拟合出来的高斯分布的均值和方差对阈值电压分布进行分析,同时观察到在实验测试的编程擦除循环次数和数据保存时间下,分布的方差变化较小,因此主要对分布的均值进行分析。

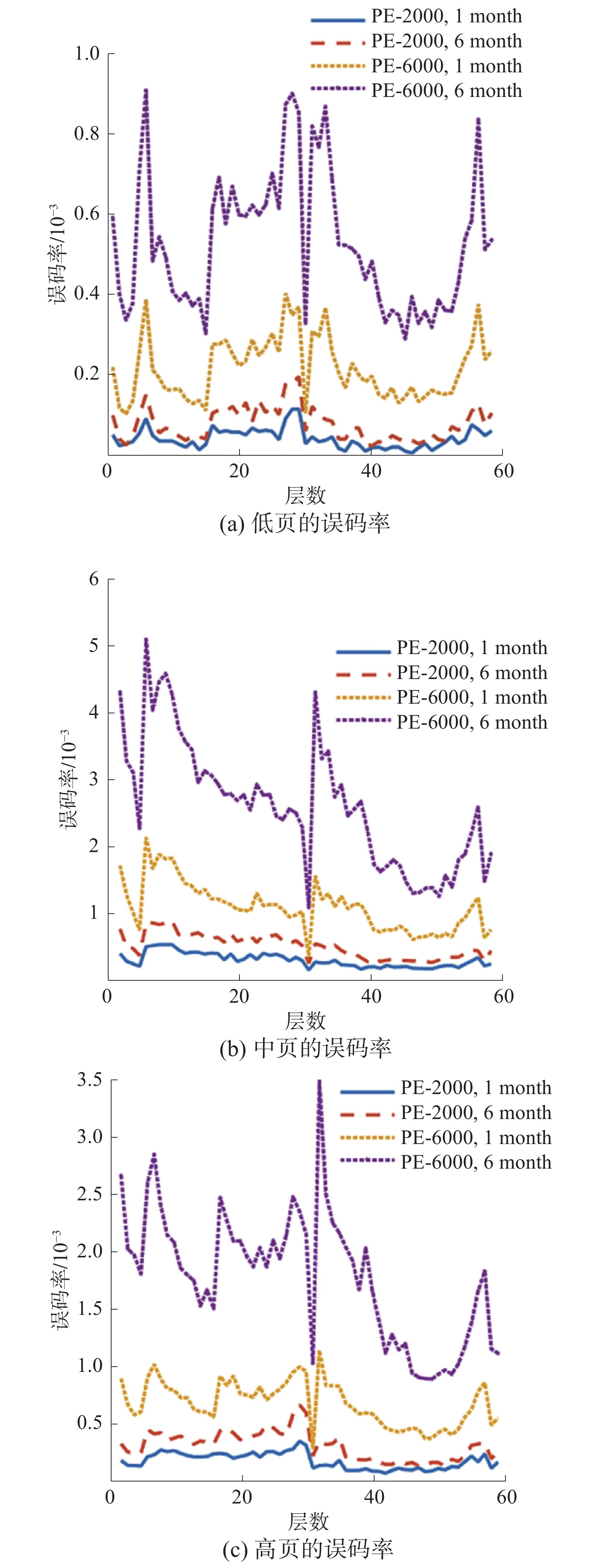

3.1 BER受层间差异的影响如图4所示,层间差异将导致不同层的存储单元的原始误码率出现较大的差异。实验芯片不同层的原始误码率有十分明显的差异,并且在编程擦除循环次数增大或者数据保存时间变久之后,不同层的原始误码率仍然保持相似的变化规律。

|

Download:

|

| 图 4 不同噪声下各层的原始误码率 | |

从图4中观察到以下4个现象:1)低页、中页、高页的原始误码率随层数的变化情况不同,并且串堆叠的高低2个串的各层的原始误码率的变化也有区别。2)低页、中页、高页的原始误码率在中间相邻2个层都存在非常大的差异。这是因为实验芯片在生产过程中使用了串堆叠技术,不同串交界处的两层分别是2个串的通道圆柱体半径最小和最大的2个部分,因此这两层的存储单元的特性会产生较大的差异。3)随着编程擦除循环次数的增大,不同层之间的原始误码率的差异增大。因为层间存在差异,不同层受到编程擦除磨损的影响不同,导致经过磨损之后不同层的误码率的差异增大。4)随着数据保存时间的增大,不同层的误码率的差异会显著增大,并且编程擦除循环次数越大,不同层的原始误码率差异越显著。因为层间差异导致不同层的存储单元对电荷泄漏的屏蔽能力不同,不同层经过一定时间的电荷泄漏之后的误码率也不同。受磨损更严重的层电荷保留能力也越差,误码率的增长也比其他层更多。

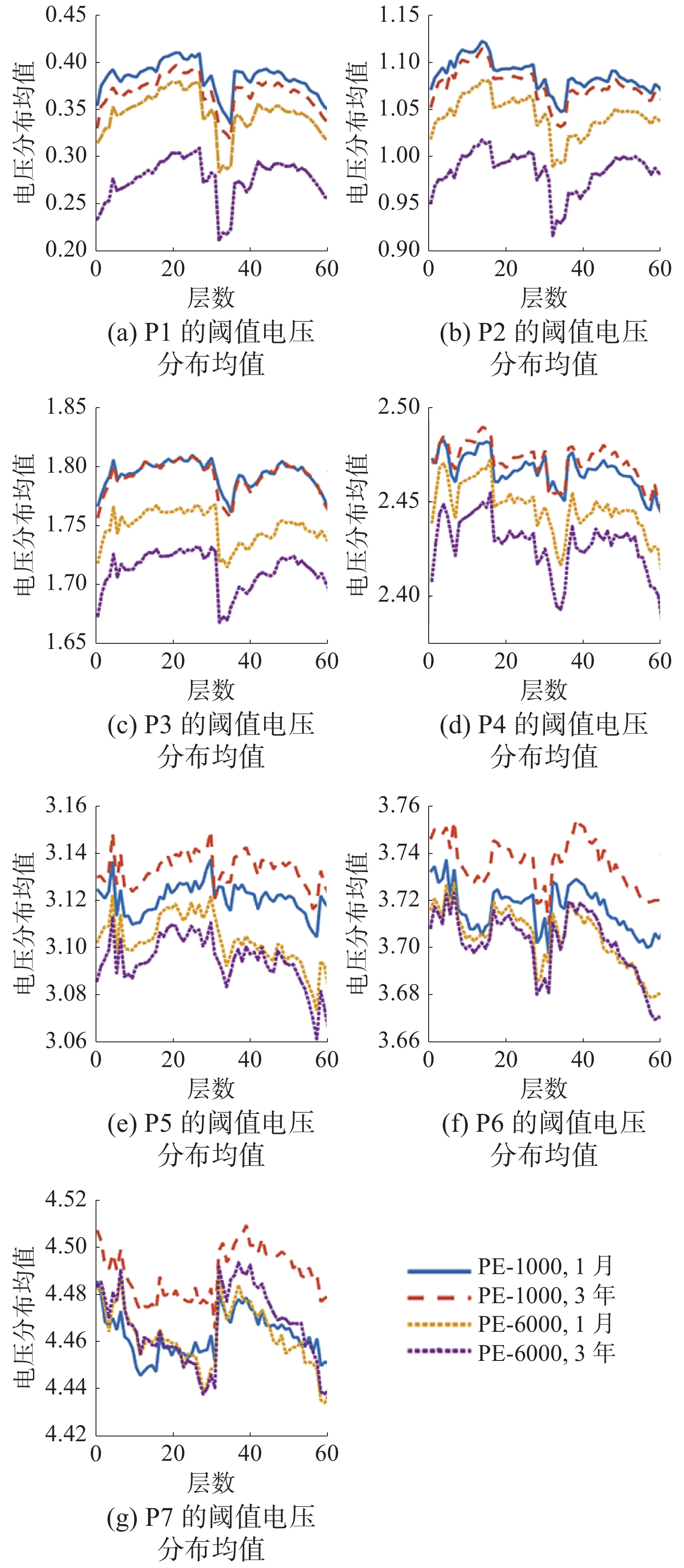

3.2 阈值电压分布均值受层间差异的影响图5为层间差异将导致不同层的各个编程状态的阈值电压分布的均值出现较大的差异,但仍然有一定的规律。串堆叠的高低2个串的阈值电压分布均值变化情况也不相同。

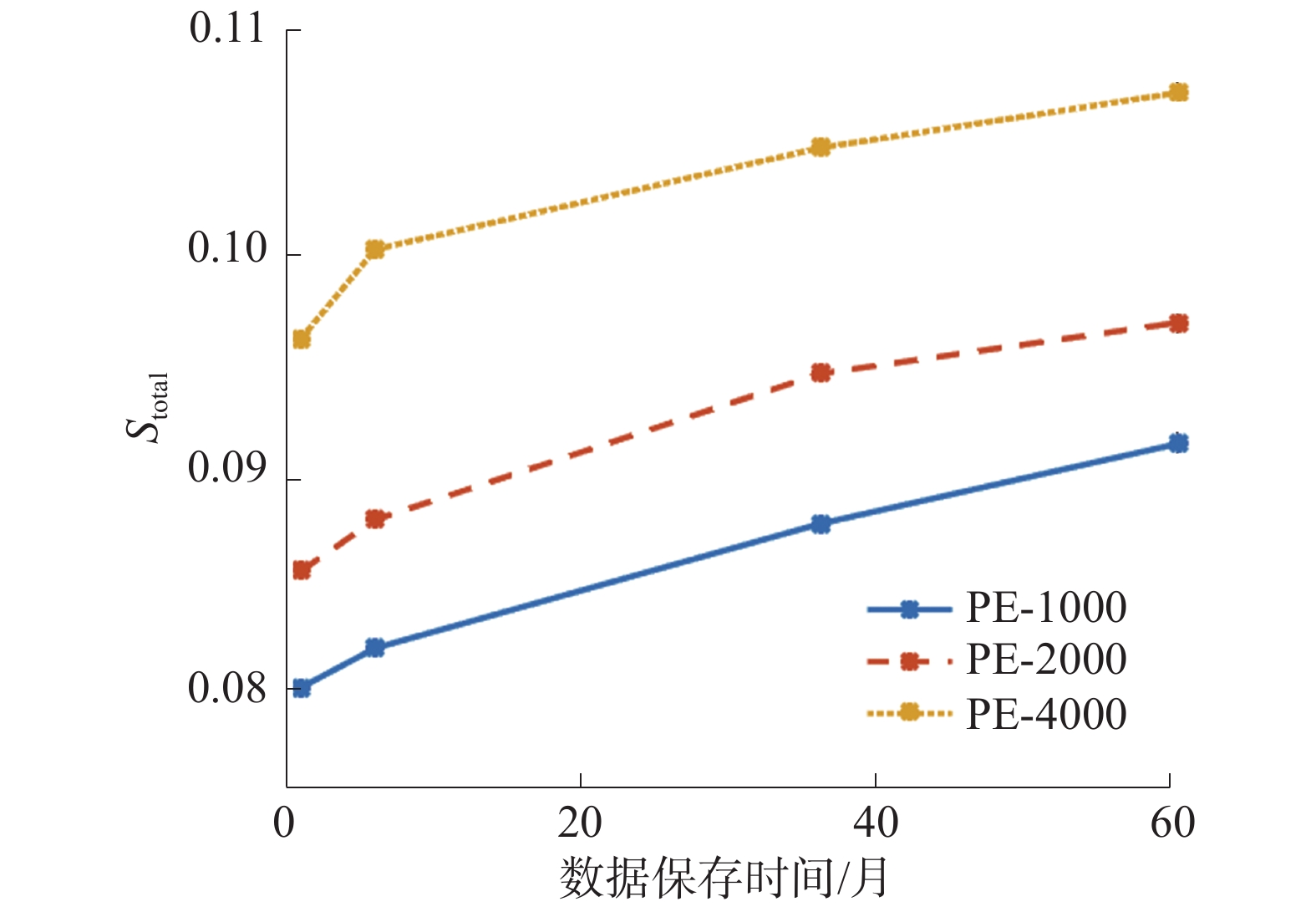

| $ \begin{array}{c}{S}_{\mathrm{t}\mathrm{o}\mathrm{t}\mathrm{a}\mathrm{l}}=\sum\limits _{s}\sum\limits _{l}{\left({m}_{s,l}-{\mu }_{s}\right)}^{2}\end{array} $ | (2) |

式中:

|

Download:

|

| 图 5 不同噪声下各层的阈值电压分布均值 | |

计算了各个噪声下的总层间差异后,可以得到图6。随着数据保存时间的增大,层间差异将导致不同层的不同编程状态的阈值电压分布的均值的大小的差异更加明显。层间差异使3D NAND闪存的不同层的存储单元的半径大小出现差异,存储单元半径大小的不同会导致存储单元的电荷屏蔽层的厚度存在差异,从而导致不同层的存储单元对电荷的保留能力产生差别。因此不同层的存储单元在经过相同的数据保存时间后,其电荷泄漏的严重程度也不相同。数据保存时间越长,不同层的存储单元因为电荷泄露产生的阈值电压分布偏移情况差异越大。

|

Download:

|

| 图 6 各层的阈值电压分布均值的方差之和 | |

随着编程擦除循环次数的增大,层间差异将导致不同层的不同编程状态的阈值电压分布的均值的差异增大。在一定的编程擦除磨损次数下,因磨损而产生的屏蔽层陷阱数量大致相同,屏蔽层的面积较小的存储单元陷阱的密度更高,也更加容易产生电荷泄漏。在一定的擦除循环次数范围内,擦除循环次数越大,不同层的阈值电压分布均值的差异也越大。

4 结论3D NAND闪存在堆叠过程中会出现垂直通道圆柱体的半径不一致的情况,导致不同层的存储单元存在不同程度的差异,使不同层的存储单元在性能上出现一定的差别。实验分析得出以下结论:

1)串堆叠的使用将导致不同串的交界处的几个层的原始误码率和各个编程状态的阈值电压分布均值产生较大的差异,并且不同串的相同高度的层的存储单元性能也存在差异。

2)不同层的存储单元受到相同的编程擦除磨损后,部分层的性能下降相比其他层更大,并且在一定的擦除循环次数范围内,擦除循环次数越大,不同层性能差异越大。

3)层间差异导致不同层存储单元对电荷的保留能力不同,受擦除循环影响更加严重的层电荷保留能力越差。

本实验对使用了串堆叠技术的3D闪存芯片不仅进行了各层的原始误码率测试,还对各层的阈值电压分布进行了测试。相比其他对3D闪存层间差异的研究,我们对层间差异受噪声的影响进行了动态分析。根据实验结果,当3D闪存的擦除循环次数达到一定的次数或者数据保存达到一定时间,不同层的差异较大,需要对不同层使用不同的处理方式。

| [1] |

SUZUKI K, SWANSON S. A Survey of trends in non-volatile memory technologies: 2000−2014[C]//Proceedings of 2015 IEEE International Memory Workshop. Monterey, USA, 2015, DOI: 10.1109/IMW.2015.7150274.

( 0) 0)

|

| [2] |

FUKUCHI M, SAKAKI Y, MATSUI C, et al. 20% system-performance gain of 3D charge-trap TLC NAND flash over 2D floating-gate MLC NAND flash for SCM/NAND flash hybrid SSD[C]//Proceedings of 2018 IEEE International Symposium on Circuits and Systems. Florence, Italy, 2018, DOI: 10.1109/ISCAS.2018.8351309.

( 0) 0)

|

| [3] |

WU Fei, ZHU Yue, XIONG Qin, et al. Characterizing 3D charge trap NAND flash: observations, analyses and applications[C]//Proceedings of the IEEE 36th International Conference on Computer Design. Orlando, USA, 2018, DOI: 10.1109/ICCD.2018.00064.

( 0) 0)

|

| [4] |

LUO Yixin, GHOSE S, CAI Yu, et al. Improving 3D NAND flash memory lifetime by tolerating early retention loss and process variation[J]. ACM SIGMETRICS performance evaluation review, 2018, 46(1): 106. ( 0) 0)

|

| [5] |

MICHELONI R, ARITOME S, CRIPPA L. Array architectures for 3-D NAND flash memories[J]. Proceedings of the IEEE, 2017, 105(9): 1634-1649. DOI:10.1109/JPROC.2017.2697000 ( 0) 0)

|

| [6] |

VENKATESAN S, AOULAICHE M. Overview of 3D NAND technologies and outlook invited paper[C]//Proceedings of 2018 Non-Volatile Memory Technology Symposium. Sendai, Japan, 2018, DOI: 10.1109/NVMTS.2018.8603104.

( 0) 0)

|

| [7] |

PAPANDREOU N, POZIDIS H, PARNELL T, et al. Characterization and analysis of bit errors in 3D TLC NAND flash memory[C]//Proceedings of 2019 IEEE International Reliability Physics Symposium. Monterey, USA, 2019, DOI: 10.1109/IRPS.2019.8720454.

( 0) 0)

|

| [8] |

GODA A, PARAT K. Scaling directions for 2D and 3D NAND cells[C]//Proceedings of 2012 International Electron Devices Meeting. San Francisco, USA, 2012, DOI: 10.1109/IEDM.2012.6478961.

( 0) 0)

|

| [9] |

CAI Yu, HARATSCH E F, MUTLU O, et al. Threshold voltage distribution in MLC NAND flash memory: characterization, analysis, and modeling[C]//Proceedings of 2013 Design, Automation & Test in Europe Conference & Exhibition. Grenoble, France, 2013, DOI: 10.7873/DATE.2013.266.

( 0) 0)

|

| [10] |

LUO Yixin, GHOSE S, CAI Yu, et al. Enabling accurate and practical online flash channel modeling for modern MLC NAND flash memory[J]. IEEE journal on selected areas in communications, 2016, 34(9): 2294-2311. DOI:10.1109/JSAC.2016.2603608 ( 0) 0)

|

| [11] |

HSIAO W H, WANG Nianjia, LI Mingyi, et al. Modeling of apparent activation energy and lifetime estimation for retention of 3D SGVC memory[C]//Proceedings of 2019 IEEE International Reliability Physics Symposium. Monterey, USA, 2019, DOI: 10.1109/IRPS.2019.8720463.

( 0) 0)

|

| [12] |

PARNELL T, PAPANDREOU N, MITTELHOLZER T, et al. Modelling of the threshold voltage distributions of sub-20nm NAND flash memory[C]//Proceedings of 2014 IEEE Global Communications Conference. Austin, USA, 2014, DOI: 10.1109/GLOCOM.2014.7037159.

( 0) 0)

|

2021, Vol. 48

2021, Vol. 48