2. 中国科学院自动化研究所 国家专用集成电路设计工程技术研究中心, 北京 100190

2. National ASIC Design Engineering Center, Institute of Automation, Chinese Academy of Sciences, Beijing 100190, China

无线通信技术的发展,给数字基带处理带来了很大挑战,全球DSP大厂,如德州仪器(Texas Instruments,TI)、CEVA、飞思卡尔等,纷纷推出了一系列基于DSP的无线通信解决方案[1-2],处理器中集成了一系列加速引擎作为协处理器对复杂算法进行加速。协处理器架构采用一维配置[3],加速引擎阵列直接挂接到总线,导致互连网络功耗比较大[4-5]。加速引擎由主处理器激活,当任务调度频繁时,总线带宽占用比比较大。本文分析了一维配置下协处理器架构特点和不足,提出一种二维可配置协处理器架构。

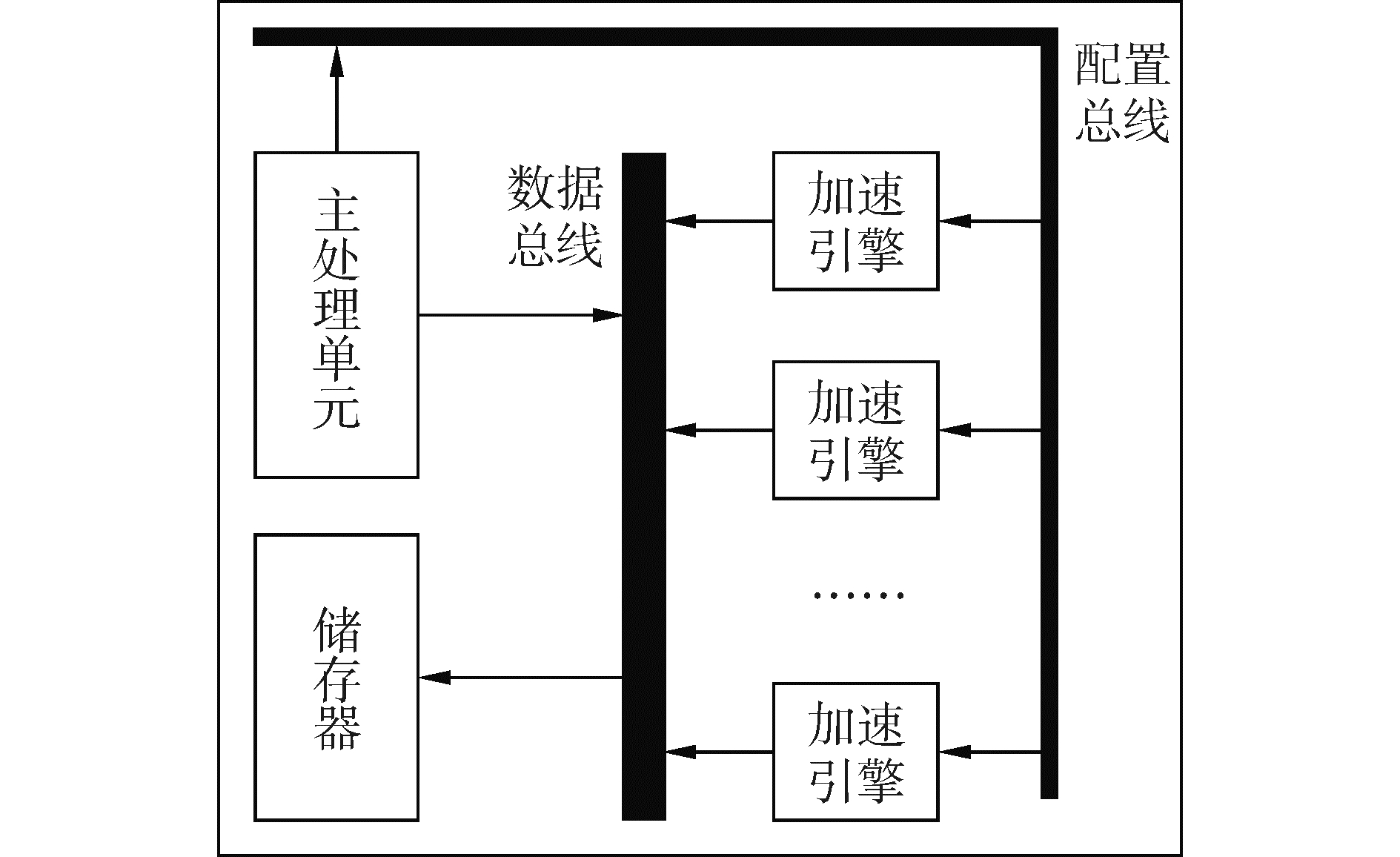

1 主流通信专用协处理器架构 1.1 互连网络功耗以TI TMS320C667和CEVA-XC处理器为代表,其协处理器架构属于经典协处理器架构,如图 1所示。一系列加速引擎直接挂接到总线,由主处理单元进行调度管理。

|

Download:

|

| 图 1 经典协处理器架构 Fig. 1 The classical coprocessor architecture | |

文献[6]通过网络仿真工具OPNET对2D-Mesh和2D-Torus网络拓扑结构进行了互连网络功耗评估,仿真方案采用均匀流量的网络通信模式,仿真表明:随着互连网络节点数目增加,网络功耗随之增加,并呈现出线性增长关系。

文献[7]基于分析模型提出了一种片上互连建模工具,并利用40 nm CMOS电路仿真结果进行校准。该工具得出了功耗评估模型:

| $ {\text{power}} = N \times {\text{DW}} \times ({C_{{\text{wire}}}}{\text{VD}}{{\text{D}}^2} + {C_{{\text{mux}}}}{\text{VD}}{{\text{D}}^2}) $ | (1) |

式中:N表示节点数目,DW表示总线数据位宽,Cwire是输入信号、输出信号和内部转换信号线电容总和,Cmux表示多路复用器转换一个数据位时所有门电路电容和扩散电容之和,VDD表示电压。

由功耗评估模型可以看出,总线接入节点数目越多,总线电容负载越大,功耗也越大。文献[8]通过90 nm CMOS设计,得出了互连网络功耗关于N和DW的函数模型。当N < 32时,功耗为O(N2DW),并附加25%~50%额外功耗开销;当N≥32时,功耗为N的超二次函数,并附加40%~80%额外功耗开销。对于总线功耗的研究表明,互连网络功耗约占导线总功耗的90%[9]。随着总线位宽的增加,总线功耗占比会越来越大。

根据以上分析可以看到主流商用DSP架构的明显不足:当总线接入节点数量较多时,总线互连网络功耗比较大。

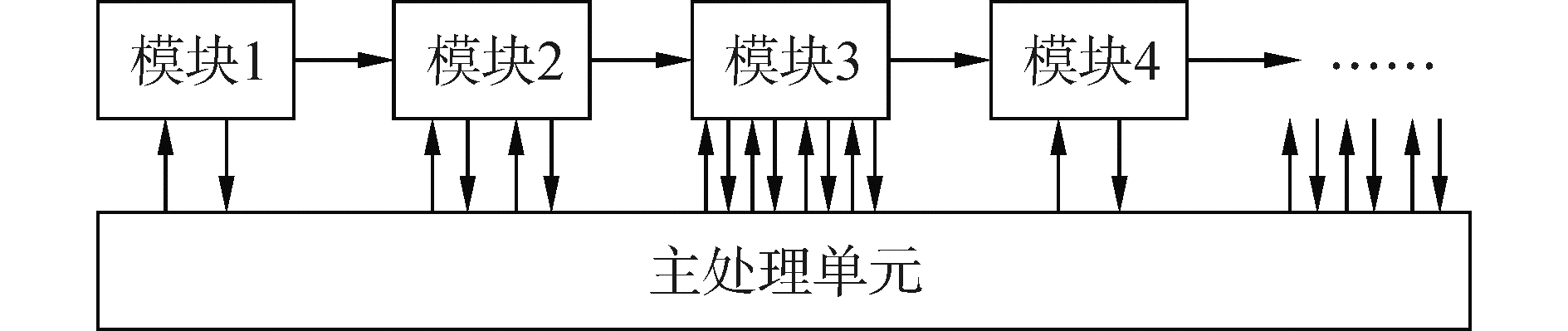

1.2 调度经典协处理器架构支持一维配置,即主处理器对每个加速引擎的工作参数进行配置,如MorphoSys协处理器[10],加速引擎阵列通过“Context Word”进行配置。后期协处理器类型不断演进,功能更加复杂,不再是单纯的代数运算逻辑,而是针对某些复杂算法特殊设计的加速引擎[11-13]。主处理器根据任务队列,对加速引擎进行任务下发,加速引擎工作结束后发出中断通知主处理单元,工作时序如图 2所示。协处理器一维配置下调度频繁:1)对总线访问频率比较高,2)寄存器配置、加载开销比较大,3)协处理器频繁调度会增加主处理器时序控制复杂度。

|

Download:

|

| 图 2 主处理器与加速引擎之间调度时序 Fig. 2 The scheduling timing between the main processor and the accelerators | |

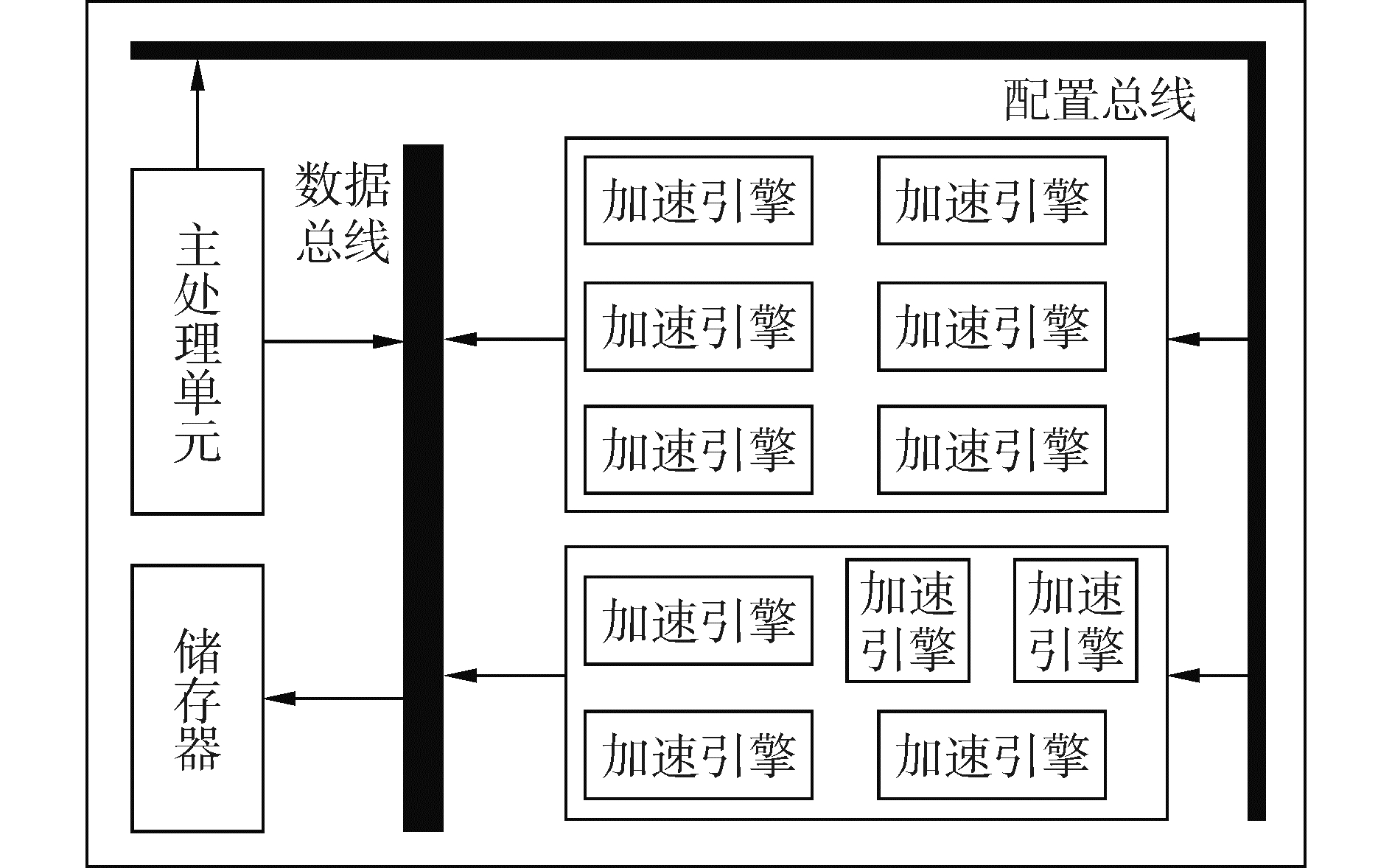

基于目前主流通信专用协处理器架构互连网络功耗大、调度频繁问题,本文提出一种新型二维可配置协处理器架构,如图 3所示。将加速引擎阵列依据发送和接收分离的准则进行分簇,簇间通信由主处理器控制,并通过总线桥接完成。经过分簇后的加速引擎阵列,分时共享簇内一组总线接口。协处理器采用二维配置,第一维配置为工作模式和协处理器公共参数配置,由主处理器发起,协处理器实时响应;第二维配置为加速引擎私有参数配置,由主处理器离线完成。这部分配置参数预先存储于指定区域,协处理器激活后,自行读取私有配置信息进行工作。协处理器配置支持查询机制,当主处理单元检测到协处理器处于空闲状态时,可以随时发起下一次配置。该配置属于半动态配置,即协处理器簇可实时响应配置,但簇内加速引擎需等待协处理器簇整体空闲后,才能响应下一次配置。二维配置减少了主处理单元与协处理器交互频率,在互连网络功耗、总线带宽占用比、软件调度频率方面提高了系统性能。

|

Download:

|

| 图 3 二维可配置协处理器架构 Fig. 3 The two level reconfigurable coprocessor architecture | |

基于互连网络功耗模型和电路级仿真结果,对新型二维可配置协处理器架构下互连网络功耗进行评估。假设协处理器中加速引擎个数为N,经典协处理器架构互连网络功耗为Pt。本文所提协处理器架构将加速引擎分簇,假设分簇数目为n,则分簇后相当于n个节点接入总线,互连网络功耗为

| $ {p_n} = a{p_t} $ | (2) |

式中:a表征总线分簇比,且a=n/N。总线分簇比越小,互连网络功耗越低。

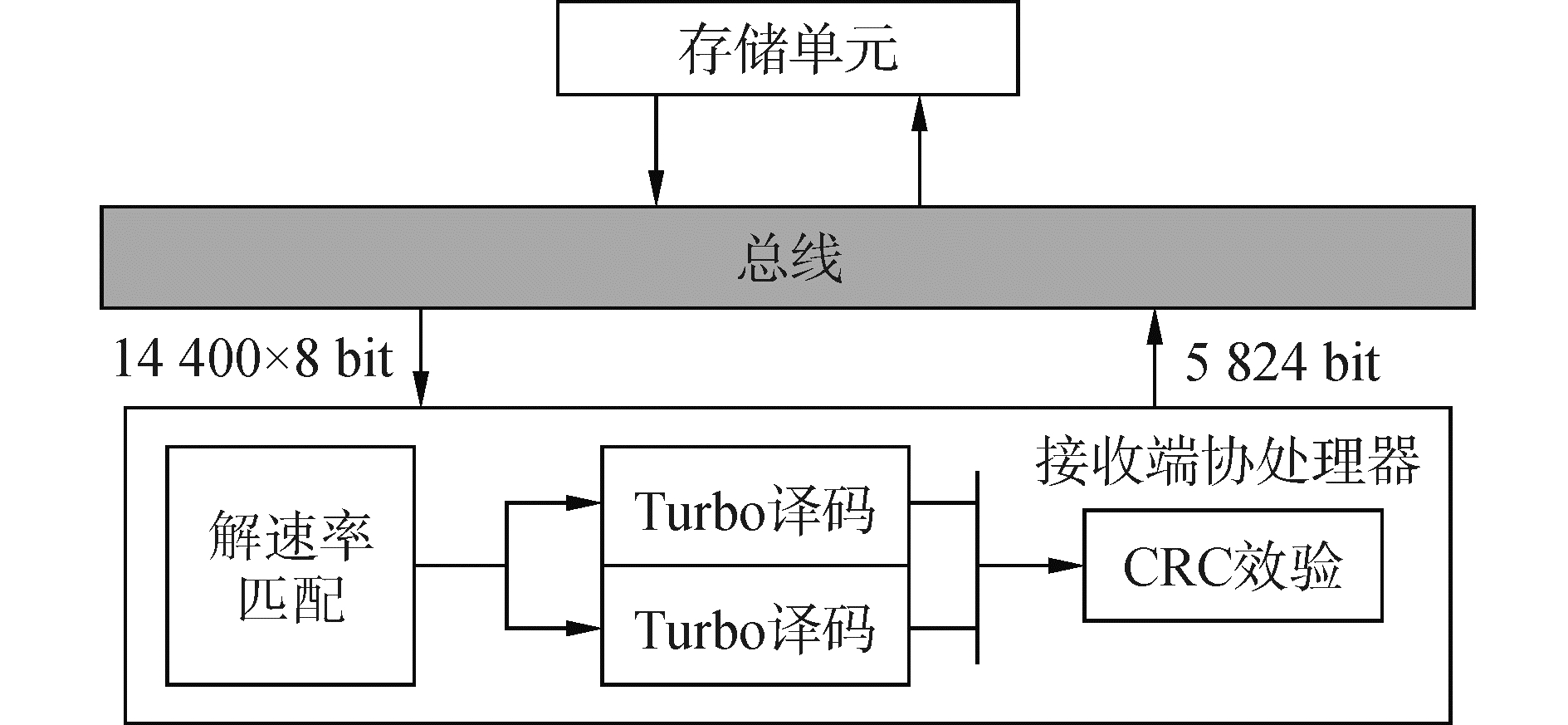

接下来以无线通信系统中标准数据帧处理,分析新型架构下互连网络动态功耗。无线通信接收端比特级数据处理包括解速率匹配→HARQ合并→turbo译码→CRC校验,对应的加速引擎有DeRM、TDC、CRC。基站侧对数据吞吐要求比较高,通常需集成多个TDC模块。

单位数据通过互连网络传输,产生的功耗包括三部分:交换开关功耗Pswitch、链路功耗Ppath和时钟树功耗Pclocktree:

| $ {P_{{\text{network}}}} = {P_{{\text{switch}}}} + {P_{{\text{path}}}} + {P_{{\text{clocktree}}}} $ | (3) |

若节点i到节点j之间传输数据包个数为M,则节点i到节点j之间互连网络功耗为

| $ {P_{i \to j}} = \sum\limits_{k = 0}^{M - 1} {({P_{{\text{switch}}}}\left( k \right) + {P_{{\text{path}}}}\left( k \right)) + {P_{{\text{clocktree}}}}} $ | (4) |

当互连网络节点数目为N时,互连网络总功耗:

| $ {P_{{\text{total}}}} = \sum\limits_{s = 0}^{N - 1} {\sum\limits_{k = 0}^{M - 1} {\left( {{P_{{\text{switch}}}}\left( {s, k} \right) + {P_{{\text{path}}}}\left( {s, k} \right)} \right) + {P_{{\text{clocktree}}}}\left( N \right)} } $ | (5) |

式中时钟树功耗抽象为网络节点数目N的函数。互连网络功耗与节点间传输数据包长度以及节点数目有关,可以进一步将互连网络功耗表示为

| $ {P_{{\rm{total}}}} = ({P_{{\rm{switch}}}} + {P_{{\rm{path}}}}) \cdot BW + {P_{{\rm{clocktree}}}}\left( N \right) $ | (6) |

式中:BW表示总线访问带宽,表征访问节点数目以及节点间传输的数据包长度。

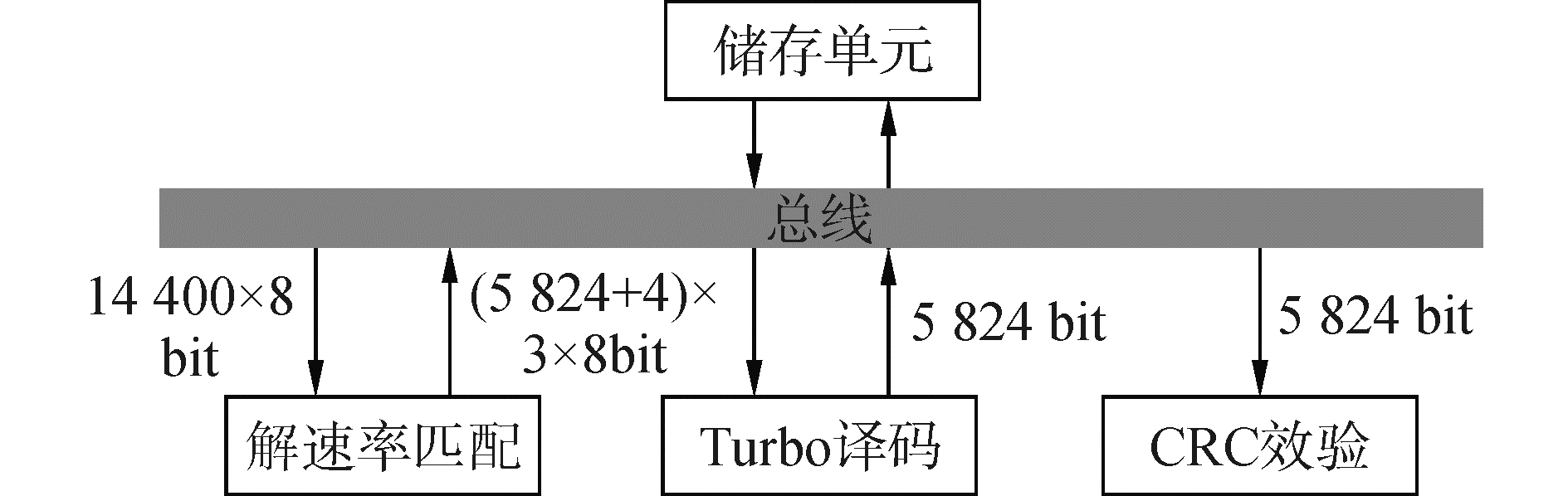

假设接收机1 ms内处理的一个标准数据帧长为75 376 bit,分割成的码块长度为5 824 bit,码块个数为13。分簇前,1 ms内总线带宽访问如图 4所示。

|

Download:

|

| 图 4 分簇前总线带宽访问 Fig. 4 Bus bandwidth access before clustering | |

带宽访问量为

| $ \begin{gathered} \left( {14\;400 \times 8 + 2 \times 5\;828 \times 3 \times 8 + 5\;824 \times 2} \right) \times \hfill \\ \;\;\;\;\;\;\;\;\;\;\;\;\;13 = 5\;285\;696{\text{ bit}}/{\text{ms}} \hfill \\ \end{gathered} $ | (7) |

分簇后,协处理器对总线带宽访问如图 5所示。

|

Download:

|

| 图 5 分簇后总线带宽访问 Fig. 5 Bus bandwidth access after clustering | |

协处理器带宽访问量为

| $ \left( {14\;400 \times 8 + 5\;824} \right) \times 13 = 15\;73\;312\;{\text{bit}}/{\text{ms}} $ | (8) |

不足经典协处理器架构的1/3。分簇前后,总线带宽访问量如图 6所示,系统功耗包括簇内功耗和总线互连功耗,簇内模块产生的结果数据可以直接送入下一模块进行消费,降低了数据流动。信号翻转引起的电容充放电是动态功耗的主要来源,通过分簇,降低数据搬运次数,减少互连网络功耗,进而降低系统整体功耗。

|

Download:

|

| 图 6 分簇前后带宽访问量 Fig. 6 Comparison of bandwidth access before and after clustering | |

配置总线占用带宽比较小,这里只讨论数据总线带宽占用比。经典协处理器架构下,每个加速引擎需从总线加载数据,并将结果写回总线,占用总线带宽用BWl、BWs来表示,协处理器占用总线带宽为

| $ {\text{B}}{{\text{W}}_{{\text{total}}}} = {\text{BW}}_l^0 + {\text{BW}}_s^0 + \ldots + {\text{BW}}_l^{N - 1} + {\text{BW}}_s^{N - 1} $ | (9) |

对加速引擎进行分簇后,簇内某些加速引擎产生的结果数据可以立即被下一加速引擎消耗,无需通过总线传递。协处理器内部根据工作模式配置,可以将DeRM输出结果直接写入TDC缓存区,TDC输出结果直接写入CRC缓存区,如图 7所示。

|

Download:

|

| 图 7 簇内数据处理流 Fig. 7 Data process in the cluster | |

此种工作模式下,协处理器占用总线带宽为

| $ {\rm{B}}{{\rm{W}}_{{\rm{novel - total}}}} = {\rm{BW}}_l^0 + {\rm{BW}}_s^{N - 1} $ | (10) |

下面仍以标准数据帧长75 376为例讨论协处理器总线带宽占用比。协处理器处理一个码块总线带宽访问量如图 4所示。假设总线位宽为128 bit,时钟频率为600 MHz,协处理器架构优化前总线带宽占用比如为

| $ \begin{array}{l} \;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;{r_{{\rm{before}}}}{\rm{ = }}\\ \frac{{\left( {14\;400 \times 8 + 2 \times 5\;828 \times 3 \times 8 + 5\;824 \times 2} \right) \times 13 \times 1\;000}}{{600 \times 128 \times {{10}^6}}}\\ \;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\;\; \approx 0.068\;8 \end{array} $ | (11) |

协处理器架构优化后总线带宽占用为

| $ {r_{{\rm{after}}}} = \frac{{\left( {14\;400 \times 8 + 5\;824} \right) \times 13 \times 1\;000}}{{600 \times 128 \times {{10}^6}}} \approx 0.020\;5 $ | (12) |

与传统通信处理器架构相比,二维协处理器架构总线带宽占用比由6.88%降到2.05%,大大缓解了总线压力。

2.3 软件调度频率无线通信系统中存在频繁调度某个加速引擎的情况,例如信道译码是分码块进行的,码块数目越多,对译码加速引擎调度越频繁。无线通信接收端多码块信道译码流程如图 8所示。

|

Download:

|

| 图 8 信道译码流程 Fig. 8 Channel decoding process | |

假设一个传输块分为n个码块,经典协处理器架构下主处理器对DeRM、TDC、CRC加速引擎调度次数为ft=2n+1。新型架构下,将加速引擎以特定工作模式进行联结,可以使调度次数成倍降低。例如将DeRM与TDC进行联结,则信道译码处理流程如图 9所示,此种工作模式下协处理器调度次数为fDeRM+TDC=n+1。本文所提架构还可以将DeRM、TDC与CRC进行联结,作为另一种工作模式进行调度,此种模式下,主处理器只需调度一次协处理器即可实现多码块信道译码。

|

Download:

|

| 图 9 模块联结后数据处理流程 Fig. 9 Data processing flow after module connection | |

当前处理器朝着异构多核方向发展,片上集成了处理器、加速器、存储器等模块,体系结构设计时任务划分和任务调度不可忽视[14]。新型协处理器架构,通过增加工作模式和公共参数配置,可以大大降低主处理器对协处理器调度频率,尤其在高性能计算机[15]中,主处理器本身承担了大量数据处理任务,通过对协处理器进行二维配置,可以将主处理器从频繁调度中解放出来,减少协处理器与主处理器交互频率,从而降低软件开销。

3 协处理器性能评估本文完成了无线通信接收端协处理器设计与实现,其整体架构如图 10所示。在TSMC 28 nm标准单元库下,利用Synopsys Design Compiler工具进行综合,其主频可达600 MHz,面积为1.98 mm2,功耗为490.408 1 mW。

|

Download:

|

| 图 10 通信专用接收端协处理器整体架构 Fig. 10 Coprocessor architecture for communication receiver | |

该协处理器主要面向基站数字基带处理,具有高性能的优势。协处理器中译码器数据通量与主流处理器TMS320C6670对比如表 1所示。TMS320C6670中的译码器数据通量均来自官方发布的用户手册。为了对比公平,viterbi译码器数据通量均是在码长40 bit,主频333 MHz下得出的;turbo译码器数据通量均是在码长6 144 bit,主频600 MHz下得出的。通过同一外部条件对比可以看出,本文中的viterbi译码器数据通量约为TMS320C6670的3.3倍,turbo译码器数据通量约为TMS320C6670的2.8倍。

| 表 1 本文协处理器与TMS320C6670数据通量对比 Table 1 Throughput comparison for the proposed coprocessor and TMS320C6670 |

1) 通过将加速引擎根据任务相关性进行分簇,总线互连网络功耗仅为主流通信处理器架构的1/3;

2) 一个标准数据帧处理,总线带宽占用比由6.88%降到2.05%;

3) 协处理器支持二维配置,提高了软件编程灵活度。二维配置协处理器架构为多模通信模块复用进行了有益探索,通过分簇可以充分对存储单元进行复用,大大提高芯片能效比。

4) 该架构在总线互连网络功耗、带宽占用比、加速引擎调度频率和硬件开销方面取得了良好的性能。

| [1] |

Texas Instruments Incorporated. TMS320C6670 Multicore fixed and floating-point system-on-chip. data manual, SPRS689D. Texas Instruments Incorporated[EB/OL]. http://www.ti.com/lit/ds/symlink/tms320c6670.pdf.

(  0) 0)

|

| [2] |

Freescale Semiconductor. MSC8157: Six-core digital signal processor[R]. Freescale Semiconductor, 2011.

(  0) 0)

|

| [3] |

HARJU L, NURMI J. A synchronization coprocessor architecture for WCDMA/OFDM mobile terminal implementations[C]//Proceedings of 2005 International Symposium on System-On-Chip. Tampere, 2005: 141-145.

(  0) 0)

|

| [4] |

MARCULESCU R, OGRAS U Y, PEH L S, et al. Outstanding research problems in NoC design:system, microarchitecture, and circuit perspectives[J]. IEEE transactions on computer-aided design of integrated circuits and systems, 2009, 28(1): 3-21. DOI:10.1109/TCAD.2008.2010691 (  0) 0)

|

| [5] |

王俊辉.高性能多核处理器的低功耗片上网络研究[D].长沙: 国防科学技术大学, 2015. WANG Junhui. Low-power on-chip networks in high-performance multi-core processors[D]. Changsha: National University of Defense Technology, 2015. http://www.wanfangdata.com.cn/details/detail.do?_type=degree&id=D01107947 (  0) 0)

|

| [6] |

黄岗. MPSoC互连网络功耗模型及其应用[D].西安: 西安电子科技大学, 2011. HUANG Gang. The research and application of power model for interconnection network in MPSoC[D]. Xi'an: Xidian University, 2011. http://www.wanfangdata.com.cn/details/detail.do?_type=degree&id=Y1865331 (  0) 0)

|

| [7] |

CAKIR C, HO R, LEXAU J, et al. Modeling and design of high-radix on-chip crossbar switches[C]//Proceedings of the 9th International Symposium on Networks-On-Chip. Vancouver, BC, 2015: 20.

(  0) 0)

|

| [8] |

PASSAS G, KATEVENIS M, PNEVMATIKATOS D. Crossbar NoCs are scalable beyond 100 nodes[J]. IEEE transactions on computer-aided design of integrated circuits and systems, 2012, 31(4): 573-585. DOI:10.1109/TCAD.2011.2176730 (  0) 0)

|

| [9] |

LIU Daka, SVENSSON C. Power consumption estimation in CMOS VLSI chips[J]. IEEE journal of solid-state circuits, 1994, 29(6): 663-670. DOI:10.1109/4.293111 (  0) 0)

|

| [10] |

SINGH H, LEE M H, LU Guangming, et al. MorphoSys:an integrated reconfigurable system for data-parallel and computation-intensive applications[J]. IEEE transactions on computers, 2000, 49(5): 465-481. DOI:10.1109/12.859540 (  0) 0)

|

| [11] |

JUNG C Y, SUNWOO M H, OH S K. Design of reconfigurable coprocessor for communication systems[C]//Proceedings of 2004 IEEE Workshop on Signal Processing Systems. Austin, TX, 2004: 142-147.

(  0) 0)

|

| [12] |

CHIEN H Y, YANG C S, HOU H P. Non-linearity cannot help RFID resist full-disclosure attacks and terrorist fraud attacks[J]. Security and communication networks, 2013, 6(12): 1490-1495. DOI:10.1002/sec.v6.12 (  0) 0)

|

| [13] |

TANG Liang, AMBROSE J A, PARAMESWARAN S. Reconfigurable pipelined coprocessor for multi-mode communication transmission[C]//Proceedings of the 50th Annual Design Automation Conference. Austin, TX, 2013: 134.

(  0) 0)

|

| [14] |

BOUDJADAR J, KIM J H, NADJM-TEHRANI S. Performance-aware scheduling of multicore time-critical systems[C]//Proceedings of 2016 ACM/IEEE International Conference on Formal Methods and MODELS for System Design. Kanpur, 2016: 105-114.

(  0) 0)

|

| [15] |

WANG Donglin, DU Xueliang, YIN Leizu, et al. MaPU: a novel mathematical computing architecture[C]//Proceedings of 2016 IEEE International Symposium on High Performance Computer Architecture. Barcelona, 2016: 457-468.

(  0) 0)

|

2018, Vol. 39

2018, Vol. 39