波束形成[1]是鱼雷自导信号处理系统中至关重要的一个环节,而数字波束形成(DBF)作为更为灵活、有效的波束形成方式,能够抑制空间干扰与环境噪声,并为多目标DOA分辨,目标识别等后续信号处理操作提供重要的信息。

根据所处理信号的频带宽度进行划分,波束形成器可以分为窄带波束形成器和宽带波束形成器。窄带波束形成技术采用移相方式来间接控制各通道信号延时,实现过程较为简单,占用资源少,在远距离低频自导探测中常采用。对于中程以及近距离情况,需要对目标进行精确估计与识别,一般所采用具有一定时宽和带宽的信号。在宽带信号场景下,由于孔径效应,采用窄带移相的方式会带来很大的误差[2]。

对于宽带信号的DBF可以基于频域算法或者空时域处理方式来进行。其中频域算法基于子带条件下的窄带DBF方法实现,较为简单,但是受各频域子带之间相干性[3]的影响,同时还存在着由于块处理方式而留下的信号拼接[4]问题,对波束形成的实时性和后续信号处理级有很大的影响。时域处理按照能够实时地处理阵列信号,在高采样率的条件下能够获得较好的处理结果,但是计算量较大,对硬件电路有一定的要求。

现阶段鱼雷自导通常为宽带系统[5],接收机中时域宽带波束形成具体实现多采用DSP芯片进行处理,而FPGA相较于DSP而言拥有并行处理的优势,对于多通道波束形成等乘累加操作,并行处理更为合适。此外自导宽带DBF系统中对非整数倍的采样间隔造成的延迟常采用直接取整的方法,这种做法需要依靠较高的采样率以达到主波束的准确指向以及旁瓣的较高抑制效果。当采样率受限时,主瓣指向发生偏移,副瓣抑制效果变差,整体信噪比降低,从而产生不准确的波束形成结果。针对鱼雷自导多通道高信号处理系统的需求,应用分数时延滤波器技术,研究设计了基于FPGA的鱼雷自导系统中宽频带精确时延波束形成器,弥补了低采样速率时由于应用延迟线而造成的DBF不精准问题,同时也有效改善了信噪比。

1 鱼雷自导时域宽带波束形成 1.1 时域宽带波束形成方法以简单的均匀直线阵为例,满足远场条件的水声场中均匀分布着M个水听器阵元,其间距为d,d在通常情况下取波长的一半,信号入射方向为θ,则相邻2个阵元之间时延差为

| $ {s_i} = x(t - (i - 1)\tau ) + {n_i}(t),i = 1,\cdots ,M。$ | (1) |

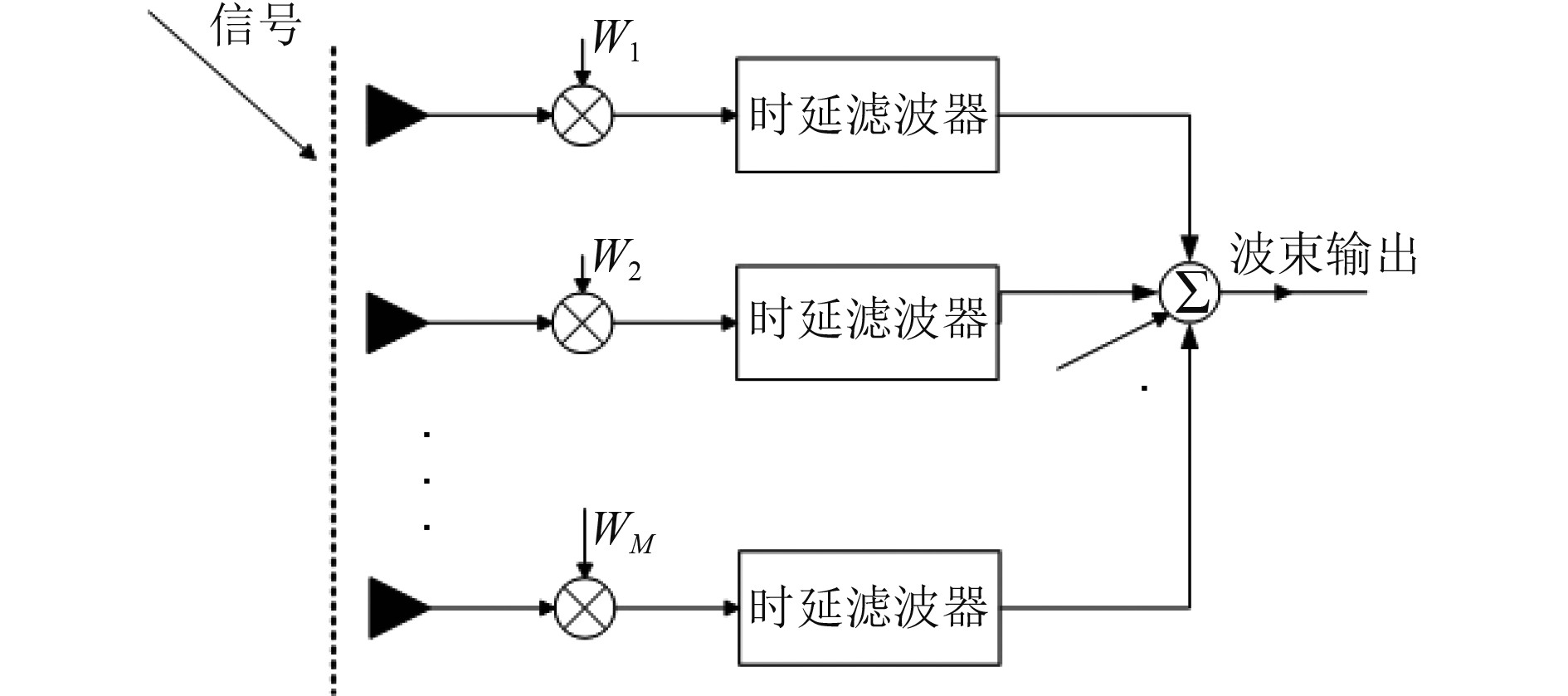

时域宽带波束形成器结构如图1所示。

|

图 1 经典时域宽带波束形成器结构 Fig. 1 Classic time-domain Broadband beamformer structure |

可以看出,不同阵元的阵列信号进入波束形成器后乘以加权因子,进行波形调整,用于波束主瓣宽度和旁瓣高低的平衡,经过时延滤波器进行延迟的补偿,在主波束方向确定的情况下,补偿的延迟仅与基准阵元的相对位置有关。整个波束形成器输出为:

| $ {s_o} = \sum\limits_{i = 1}^M {{w_i}{s_i}(t - (i - 1)\Delta )} + {n_i}(t),$ | (2) |

用时间序列的方式可以描述为:

| $ {s_o} = \sum\limits_{i = 1}^M {{w_i}{s_i}(n - (i - 1)\Delta /Ts)} + {n_i}(n)。$ | (3) |

其中Ts为采样周期。

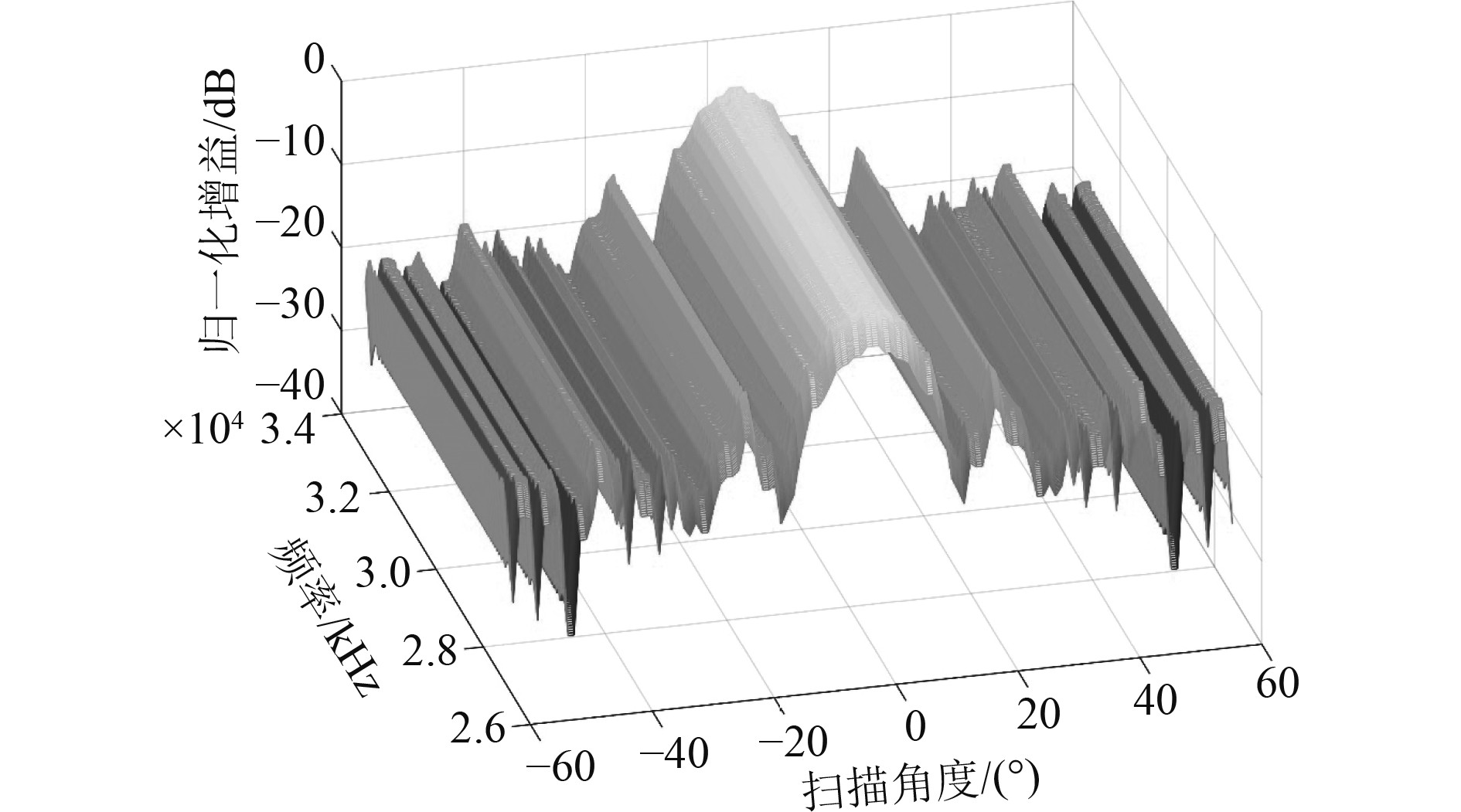

采用上述方法,得到的时域波束形成结果如图2所示。8阵元均匀线列阵,调频信号的频率范围为27 ~33 kHz,采样频率fs取200 kHz,主波束方向0°。仿真过程中直接采用移位的方式进行波束形成,移位原理和数字延迟线类似,都是基于整数倍的采样周期进行延迟。

|

图 2 时域波束形成结果 Fig. 2 Time-domain beamforming results |

可以看出,时域波束形成较好地实现了所需要的波束,规避了以往移相相加而造成的由于频率展宽而导致的主波束偏移、主瓣展宽以及分辨有效率降低等问题[6],但是直接在时域上延时往往会由于延迟精度的取舍以及时频域相互转换等原因,造成很多误差从而影响到信噪比,难以得到类似频相调整较为完美的波束图。

1.2 存在的问题由图1和式(3)可知,时延滤波器一般采用数字延迟线或者一定阶数的FIR滤波器来实现。

精确波束形成的核心在于对传播过程中非整数倍采样周期延迟补偿的处理,常见的处理方式有:多采样率信号处理(抽取、插值)、全通IIR滤波器、FIR滤波器等,对于FPGA的具体实现而言,采用FIR滤波器方式更为有效,且拥有较为稳定的线性相位。

2.1 理想分数延迟滤波器由式(3)可得,第m个阵元通道经过非整数倍采样周期的延迟补偿后得到信号y(n)中有:

| $ {\tau _m} = \dfrac{{(m - 1)d\sin \varphi }}{c} = (L + P)Ts,$ | (4) |

| $ y(n) = x(n - (L + P))。$ | (5) |

其中:d为阵元间距;c为自导接收环境下声速;φ为指定波束方向;L为整数;P为小数。可以求得系统函数为:

| $ H({e^{jw}}) = \dfrac{{Y({e^{jw}})}}{{X({e^{jw}})}} = \dfrac{{{e^{ - jw(L + P)}}X({e^{jw}})}}{{X({e^{jw}})}} = {e^{ - jw(L + P)}}。$ | (6) |

对式(6)求离散时间傅里叶反变换,可以求得冲激响应为:

| $ {{h}_{{id}}}(n) = \dfrac{1}{{2{\text{π}} }}\int_{ - {\text{π}} }^{\text{π}} {{e^{ - jw(l + p)}}{e^{jwn}}\text{d}w} = \sin c(n - l - p)。$ | (7) |

相位信息一般可以采用群延迟来表示,即

| $ {\tau _g}(w) = - \dfrac{{\partial \theta (w)}}{{\partial w}}。$ | (8) |

P为小数时,理想滤波器的冲激响应无限长且为一个非因果系统,不适用于实际工程,需要用合理的方式让有限阶数的滤波器对理想情况进行逼近[9]。

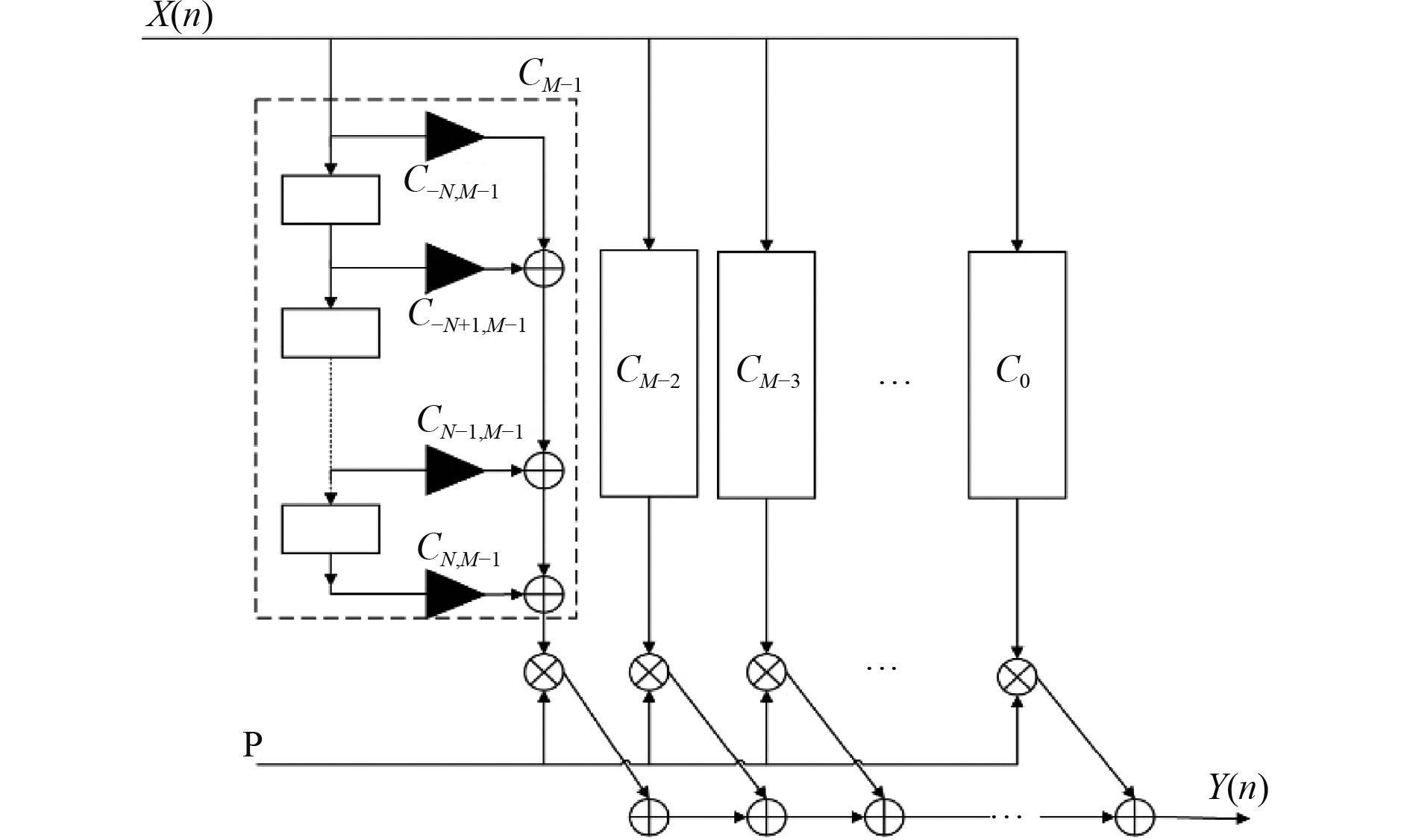

2.2 滤波器设计方法设计应用中有窗函数法、最小二乘法、拉格朗日插值等方式对滤波器进行求解,不同的设计方法对通带纹波、波形失真以及时延波动有着不同的影响。采用不同方式的窗函数进行截取一定程度上能够抑制通频带内的幅度波动,抑制程度和窗函数自身的特点有关。最小二乘设计方式要求误差函数最小时FIR滤波器权系数矢量的值,但在实际使用过程中受硬件电路限制。另外还存在一种可变分数延迟滤波器,其实现主要采用了Farrow结构,将小数延迟p作为输入,以固定的电路来形成可变的延迟结果[10]。如图3所示,Farrow结构可以看做M阶FIR滤波器的并联结构,其电路占用扩大了M倍,实现结构更加复杂,运算量也更大。

|

图 3 Farrow滤波器结构 Fig. 3 The structure of Farrow filter |

自导系统工作时通常要保证较低的旁瓣和平稳的幅度响应,相比于矩形窗和汉宁窗,海明窗在减小旁瓣幅值方面效果更好,而对比布莱克曼窗而言,海明窗主瓣较窄,属于折中方案,故采用海明窗进行截取。

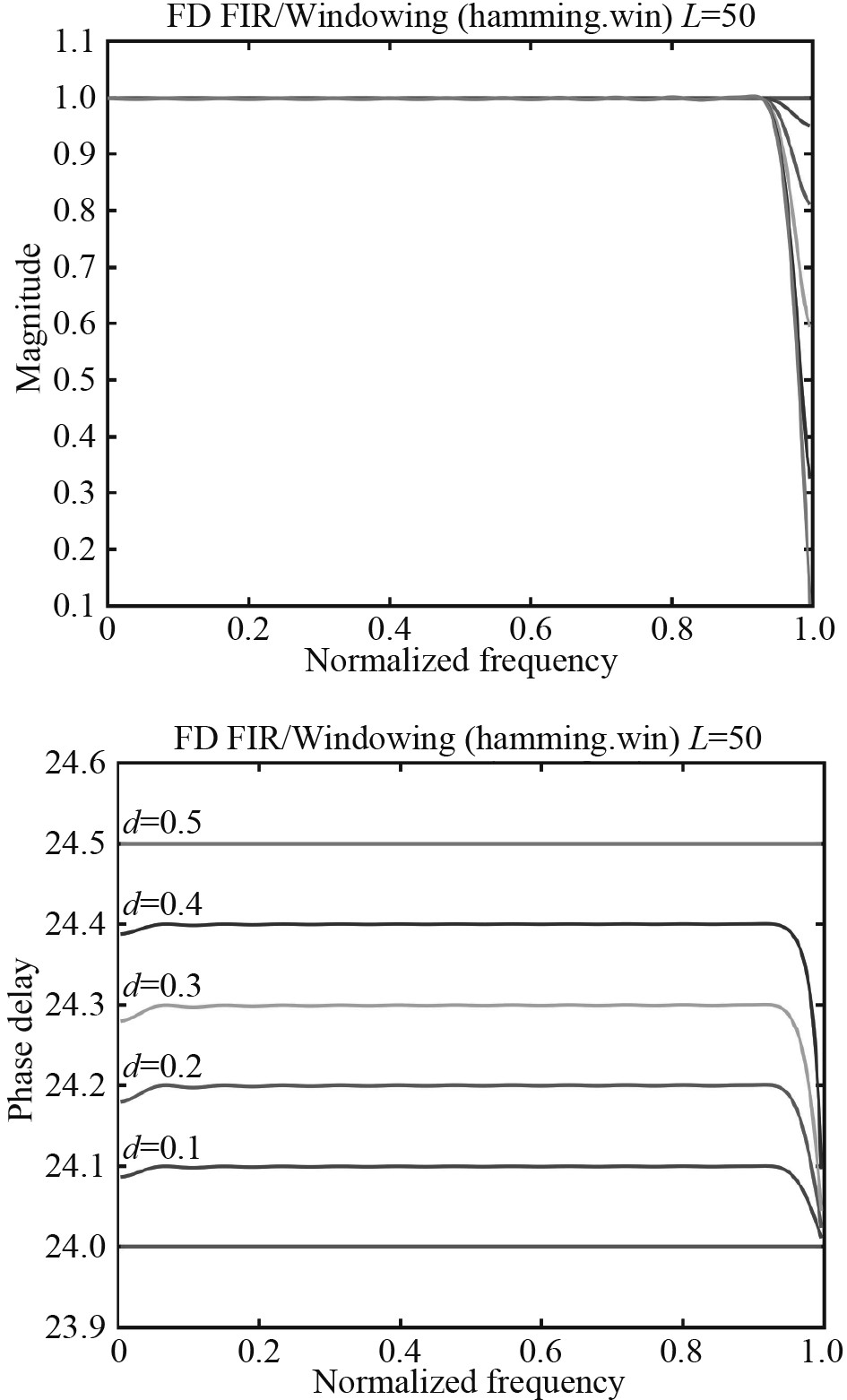

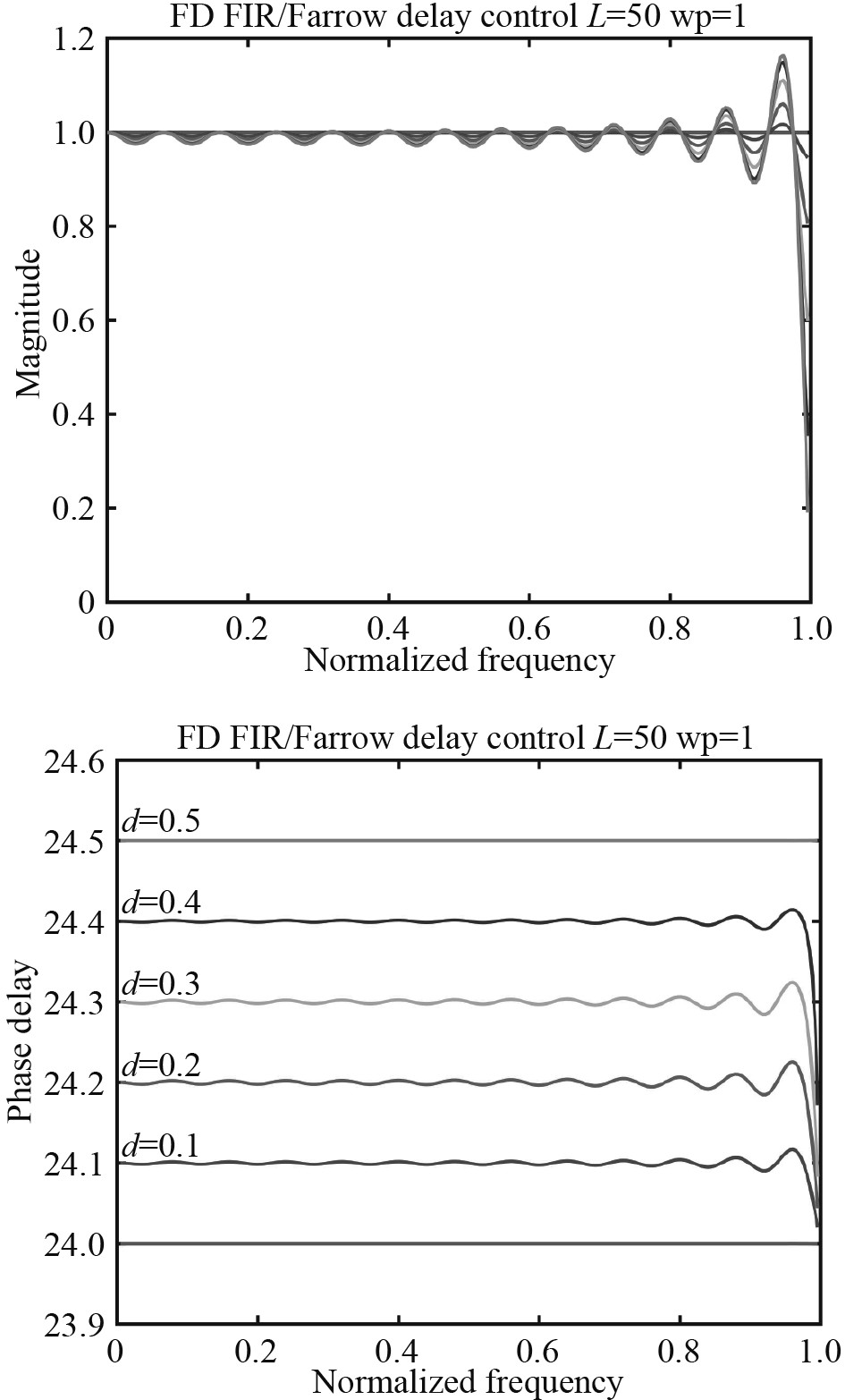

对比所提到的窗函数典型海明窗以及Farrow结构滤波器在一定阶数下仿真生成的群延迟结果与幅频响应结果,如图4和图5所示。

|

图 4 采用hamming进行截取,滤波器长度为50 Fig. 4 FIR filter with hamming structure which length is 50 |

|

图 5 采用Farrow结构的滤波器,长度为50,多项式阶数为4 Fig. 5 FIR filter with Farrow structure which length is 50,and which polynomial order is 4. |

可以看到,在滤波器长度一定的情况下,2种方法形成的滤波器群延迟响应在归一化频率0.2~0.6频带较为稳定,接近1时逐渐产生失真。其幅度响应均有不同程度的波动,波动随延迟量的增加而增大,但是在滤波器长度有限的情况下,窗函数法的波动更小。以上2种方式的具体使用应根据实际工程情况而,本文采用hamming窗截取的窗函数法进行滤波器设计。

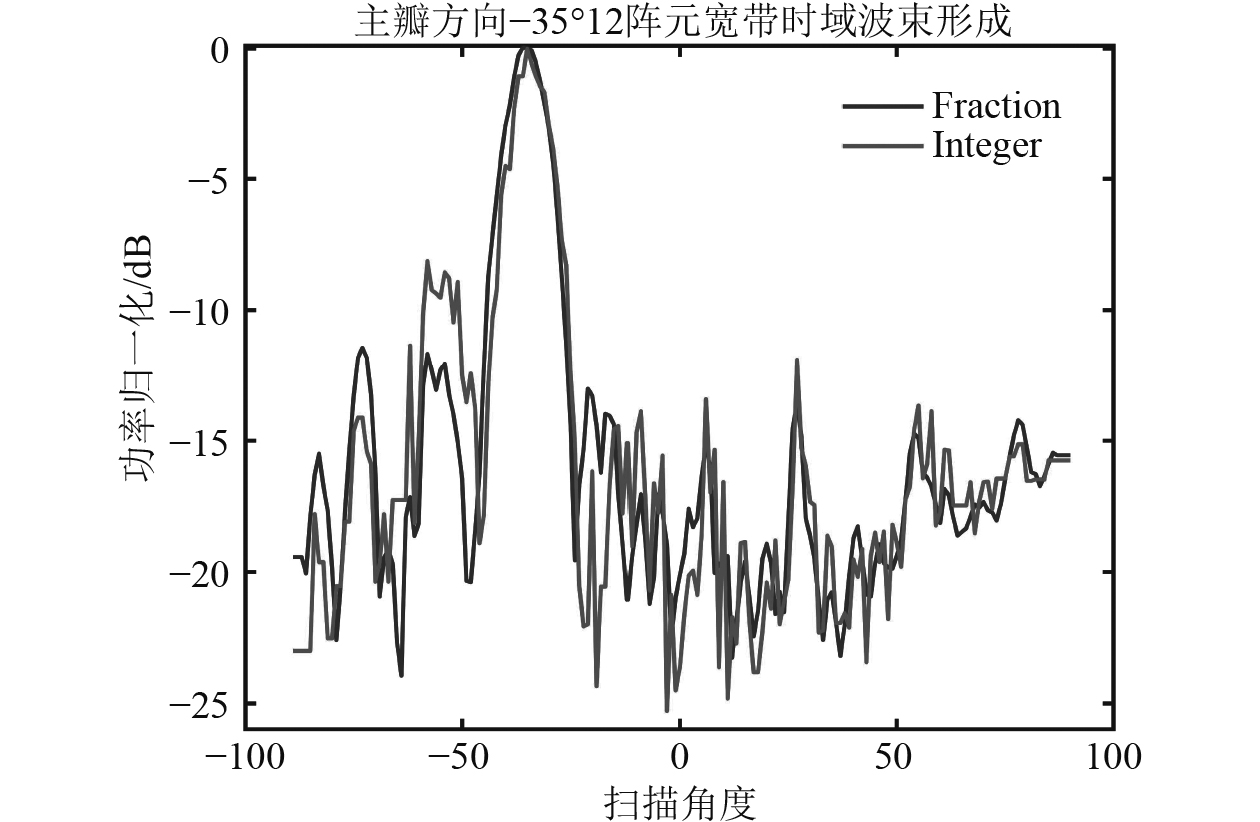

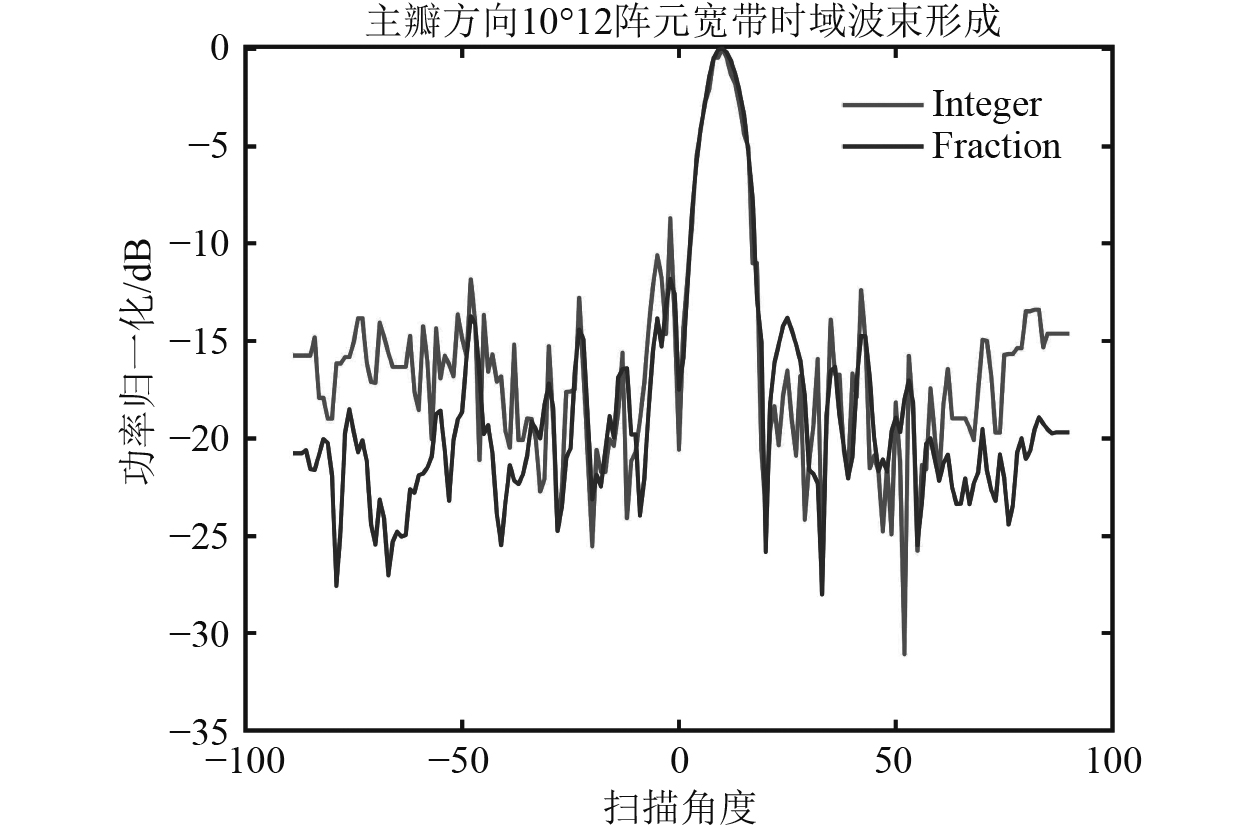

2.3 精确波束形成仿真对比以接收环境12阵元(间距为半波长)组成的均匀线列阵来仿真分析精确波束形成方法的性能,信号仍采用LFM信号,主瓣方向分别为−35°与10°,以hamming窗截断的滤波器来实现,滤波器阶数为128阶,传统波束形成采用数字延迟线的仿真方式,对比结果如图6和图7所示。

|

图 6 精确延迟对波束形成结果的影响(–35°主瓣) Fig. 6 The effect of precise delay on beamforming results (angle of –35°) |

|

图 7 精确延迟对波束形成结果的影响(10°主瓣) Fig. 7 The effect of precise delay on beamforming results (angle of 10°) |

由图6可知,主瓣方向为–35°时,传统方式旁瓣约为−8 dB,而采用精确方式的旁瓣在–13 dB左右,在主瓣两端相对持平,并且精确波束形成修复了传统方式存在的主瓣偏移若干角度的问题。由图7可知,在远离法线方向的角度,精确方式对归一化功率的优化达到5 dB以上,对提高整体的信噪比提供了很大的帮助。

综上所述,精确波束形成器在旁瓣控制与整体信噪比的抑制表现均优于传统的延迟线或者整数时延滤波器手段,这种优势在主瓣方向贴合法线方向(10°)更为明显,主瓣方向远离法线方向时,由小数部分造成的对时延精确度的影响也逐渐减少。

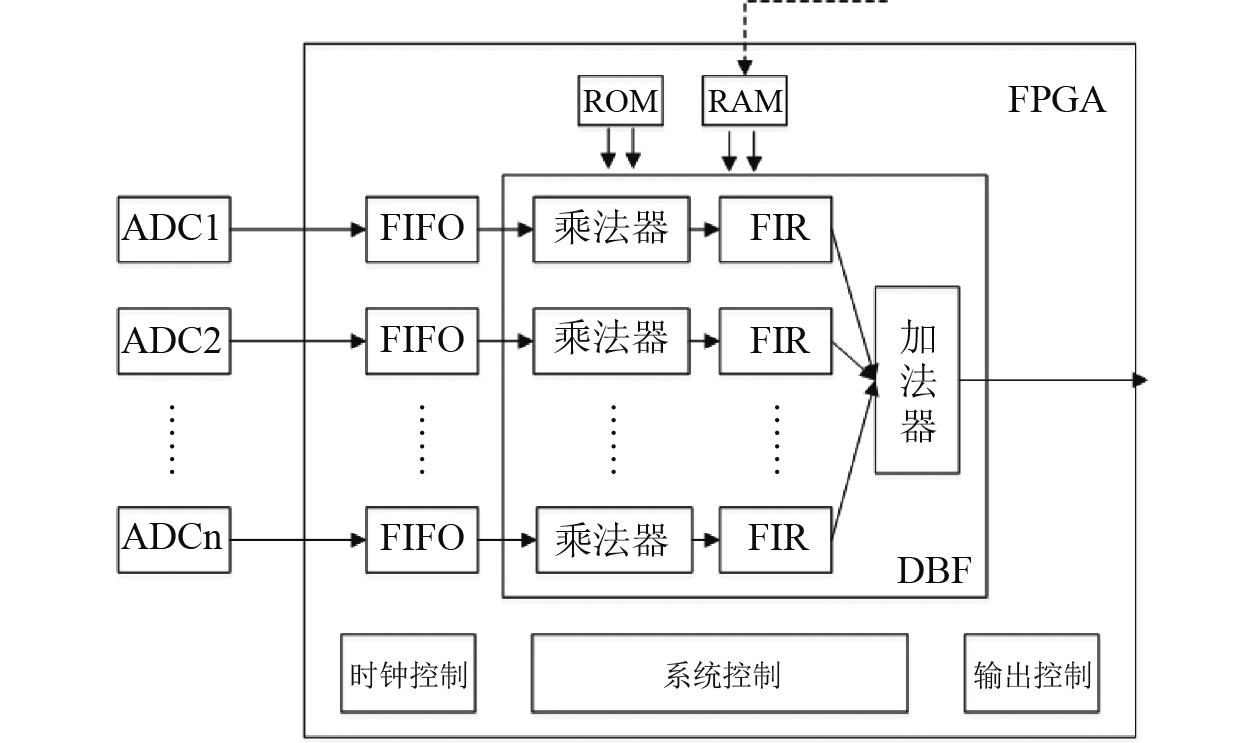

3 软硬件实现及验证 3.1 系统结构及硬件实现图8所示的自导系统中DBF接收机的结构框图包含了声呐阵列(线阵或平面阵等),模拟预处理端(模拟信号的滤波放大),数字接收组件(AD采集降频等),DBF(数字波束形成),数字信号处理(特征提取、目标识别与分辨等),由信号处理所得到的信息再反馈给全雷系统,以针对不同战斗情况的应答。

|

图 8 系统结构组成 Fig. 8 System structure. |

可以看出,DBF是水声DSP前重要的一环,是阵列信号对不同角度入射波形响应的一种体现,其实现的基本原则是能够合理接收前级数字接收组件传递来的多路采样信号,其处理结果能够以特定方式传递给后续DSP处理级。

本文设计主要实现8通道宽频带精确波束形成器,主波束方向为45°,输入线性调频信号带宽为6 kHz,中心频率30 kHz,对于水下阵列,其阵列间距取半波长0.025 m,采用常规加权的方式,对分数倍的数据延迟采用幅频响应较为平稳的hamming加窗方式,滤波器阶数为65阶。设计系统采用搭载1片Xilinx Virtex-7系列FPGA芯片与8路AD7768采集芯片的信号处理开发板。Virtex-7 FPGA芯片中内置了大量IP硬核系统级模块,其中包括应用广泛的的36KB BlockRAM、功能强大的二代25x18DSP Slices、系统监控功能、带集成数字时钟管理器(DCM)和锁相环(PLL)时钟生成器的增强型时钟管理模块,以及高级的配置选项[9],其硬件实现结构如图9所示。

|

图 9 DBF的硬件构成 Fig. 9 The hardware structure of DBF. |

FIFO负责将AD采集数据进行暂存以及时钟域的调整,乘法器处理波形幅值与权系数相乘的步骤,其中的权系数由ROM进行存储,FIR进行相应延迟操作,加法器将不同通道加权延迟结果进行累加,RAM存储对应FIR的乘累加系数,既可以直接进行读取,也可以通过外部计算写入,执行在线更新延迟的操作,以达到改变波束指向的目的;时钟控制主要接收前级基准时钟,并产生系统工作时钟;系统控制主要负责产生RAM读写地址与ROM读地址,以及控制FIFO读取,FIR使能信号的开闭;输出控制负责调整加法器输出字长,以及对输出数据的存储等调整。系统中FIFO、单口ROM与双口RAM等部分可以通过配置Virtex-7内置的IP核来实现,灵活地应用IP核能够提高系统配置的的灵活性和准确性。

3.2 运行结果及资源占用为验证系统硬件实现的可行性,利用Vivado平台进行仿真测试。将Matlab中产生的调频信号源通过testbench文件导入的方式作为AD采样模块的输出。由于仿真产生的信号幅值为[–1,1]的浮点数,需要在导入过程中进行数值的转换,按照比例将信号源放大215倍,预留一位为符号位,在验证过程中,系统的所有数据和加权系数均以16 bit有符号补码形式进行计算。

4 精确波束形成实现方法验证在硬件实现平台上并不能直观地观察波束形成结果,为了能够更好地测试波束形成器的性能,得到有效的波束图,采用System Generator软件的Hardware Co-Simulation模块[11],将FPGA开发板上已经生成的设计编译导入Simulink仿真中,通过在Matlab中调用相应的Simulink子模块,实现对入射信号方向的不断改变以及波束形成器的不断调用过程。

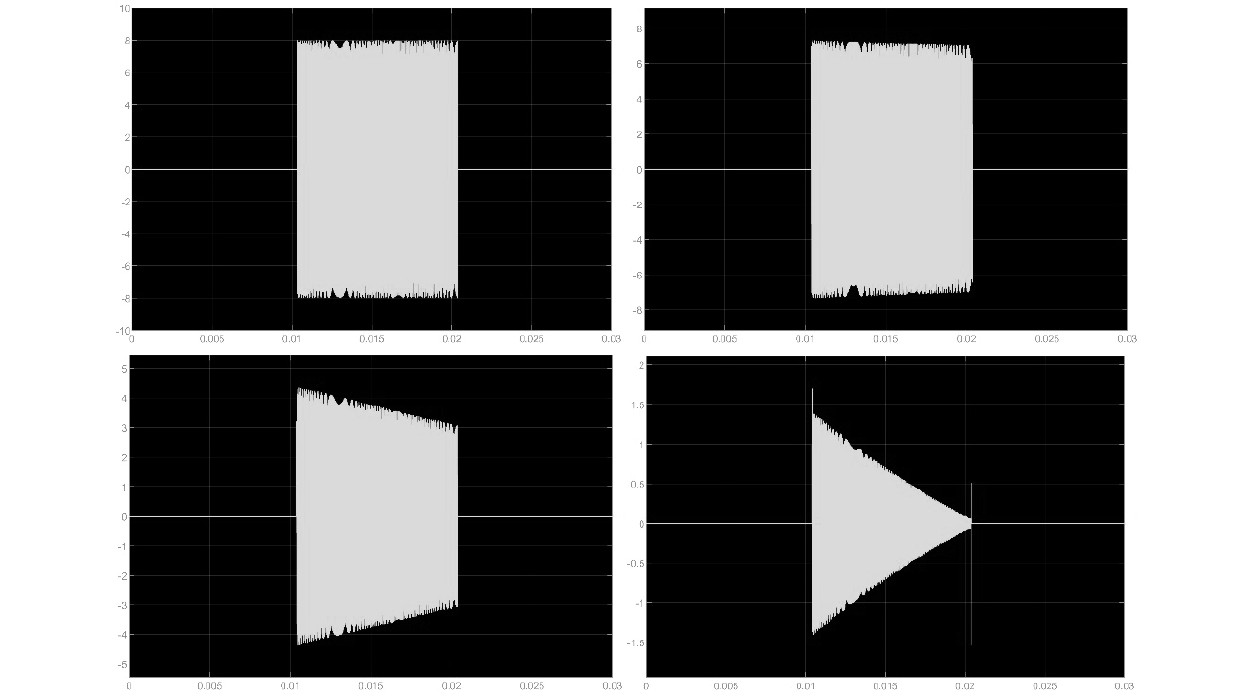

通过输出端口相连接的示波器可以观察波束形成输出结果,图10展示了输入脉宽0.05 s,周期0.5 s的调频信号,在分别偏离波束方向0°,3°,9°与15°情况下一个周期内系统的输出结果。

|

图 10 示波器显示DBF输出波形变化 Fig. 10 Oscilloscope shows the output change of DBF |

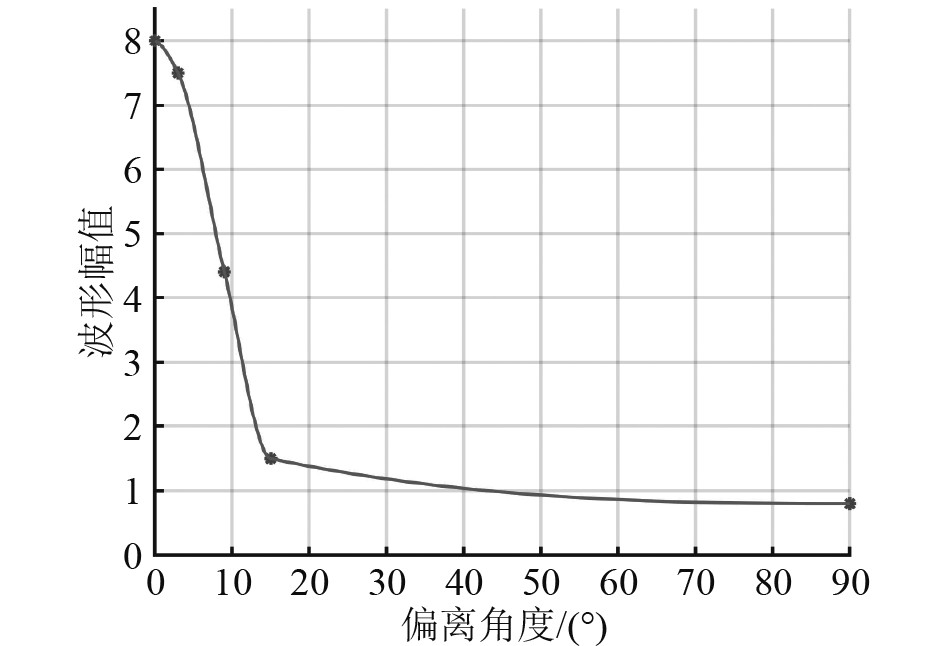

可以看到,波束输出波形在逐渐偏离主瓣方向会有不同程度的畸变,并且由图11可以看到偏离主瓣的方向具有明显的幅度衰减,在波束图中体现为阵列的方向性。调整输入信号角度,计算输出波形功率并归一化,得到波束图如图12所示。

|

图 11 偏离波束的波形幅值衰减 Fig. 11 Amplitude attenuation of deviating beam |

|

图 12 调用Matlab画波束图 Fig. 12 Call Matlab to draw pattern |

可以看出,波束图主轴方向为45°,其主瓣宽度(–3 dB)为16°,系统只对波束主瓣范围内有着较高的响应,旁瓣整体在–10 dB左右,在个别角度达到–8 dB。主要原因为在硬件实现过程中由于量化产生的误差以及电路固有的传输延迟对精确时延造成了影响,可以通过调整输入滤波器系数改变阵列主瓣指向,以应对不同的战斗需求。

5 结 语本文设计实现了一种基于精确时延滤波器的多通道宽带数字波束形成器,分析了时域宽带波束形成的原理,分数时延滤波器的设计及仿真,硬件电路的设计及功能仿真,并通过与Matlab的协同仿真,验证了此设计的可靠性。

| [1] |

鄢社锋, 马远良. 传感器阵列波束优化设计[M]. 北京: 科学出版社, 2009.

|

| [2] |

夏彦泽. 基于宽带波束形成技术的信号处理板的设计与实现[J]. 舰船电子对抗, 2017(2): 78-81. |

| [3] |

刘铸华, 林桂道. 时域宽带数字波束形成技术研究[D]. 北京: 中国舰船研究院, 2015.

|

| [4] |

唐建生. 时域宽带波束形成方法及实验研究[D]. 西安: 西北工业大学, 2004.

|

| [5] |

CAO W, FENG H, WANG S. The application of DBF neural networks for object recognition[J]. Information Sciences, 2004, 160(1): 153-160. |

| [6] |

贾艳红. 宽带数字阵实时延迟技术[D]. 成都: 电子科技大学, 2010.

|

| [7] |

ZEESHAN A, SONG Yao-liang, QIANG D. Adaptive wideband beamforming based on digital delay filter[J]. Journal of Microwaves, Optoelectronics and Electromagnetic Applications, 2019, 15(3). |

| [8] |

VESA V, LAAKSO T I. Principles of fractional delayfilters[C]// IEEEICASSP. Istanbul, Turkey, 2000: 21-26.

|

| [9] |

李小娅. 多天线系统中小数倍实验补偿及其FPGA实现[J]. 数字通信, 2014(2): 45-49. DOI:10.3969/j.issn.1005-3824.2014.02.011 |

| [10] |

徐露. 基于FPGA的频域宽带波束形成器[J]. 网络新媒体技术, 2017(4): 45-51. DOI:10.3969/j.issn.2095-347X.2017.04.009 |

| [11] |

何时.Xilinx. FPGA数字信号处理系统设计指南[M]. 北京: 中国工信出版集团, 2019.

|

| [12] |

郭涛, 吴亚军. 实测宽带阵列流形快速获取方法[J]. 鱼雷技术, 2011, 19(4): 268-270+306. |

2022, Vol. 44

2022, Vol. 44