2. 中国科学院大学 北京 100049

2. University of Chinese Academy of Sciences, Beijing 100049, China

射频四极场(Radio Frequency Quadrupole, RFQ)可用于加速从离子源中发出的低能粒子,并具有纵向群聚、横向聚焦等多个功能,常被用作高能加速器的注入器或者低能强流加速器的前级加速器[1]。RFQ腔内加载电磁波后,电磁场会在RFQ表面产生电流,腔壁及腔翼表面均会因为功率热损耗造成温度升高[2],从而发生变形,引发腔体的失谐,造成功率馈送效率损失和束流品质下降[3]。

低电平控制系统是RFQ高频系统的重要组成部分,它一方面稳定RFQ内的加速场的幅度和相位;另一方面对RFQ进行调谐控制。因为重离子加速器的束流对于电场非常敏感,常用的机械调谐结构不适用于RFQ的动态调谐[4]。为了应对RFQ在工作过程中发生的失谐,目前一般有两种办法:1)通过低电平(Low Level Radio Frequency, LLRF)控制系统提高馈入RFQ的功率,提高入腔功率的方法可以快速稳定加速腔压,但会严重增加功率源的负担,并且工作频率范围严重受限于腔的品质因子;2)通过控制RFQ腔翼和腔壁内冷却水的水温来实现对RFQ谐振频率的调整。冷却水温控制的方法是目前通用的动态调谐方法,考虑到冷却水的加热和冷却都是个相对缓慢的过程,该方法在冷却水刚开始工作或者RFQ加速腔压发生改变时,需要几十分钟来使得冷却水达到一个动态平衡的过程[5]。为了实现更加便捷的加速器调试和连续的功率提升,希望RFQ在腔压变化过程中始终处于谐振状态。本文设计了可以实时跟踪RFQ谐振频率,同时稳定加速腔内的幅度和相位的低电平控制系统。当水温缓慢变化的过程中,加速腔始终处于谐振状态,加速场的幅度和相位也可以同时保持稳定,这可以加快RFQ的老练和调试过程中的功率提升速度。

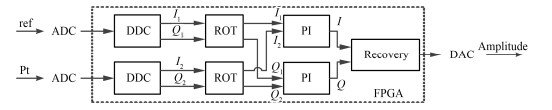

1 低电平控制系统的设计与实现RFQ的低电平控制系统包括两个环路:频率跟踪环路和幅相控制环路。频率跟踪环路的主要作用是通过监控入腔信号和腔上采样信号的相位变化,实时调整馈入RFQ的微波频率,使得RFQ始终处于谐振状态;幅相控制环路的主要作用是将腔上采样信号的幅度和相位信息与参考信号(ref)的幅相信息进行比较,并实现闭环控制,从而稳定RFQ形成的加速场的幅度和相位。

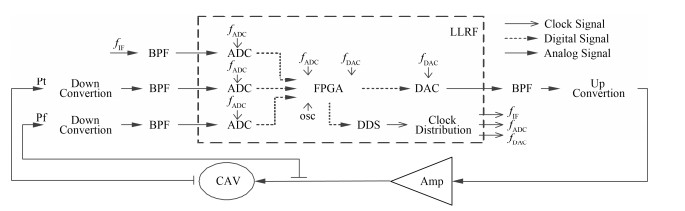

如图 1所示,RFQ低电平控制系统对参考信号(ref)、RFQ的馈入功率耦合信号(Pf)和RFQ的腔上采样信号(Pt)进行实时监测。这三个信号经过带通滤波器后,由模数转换器(Analog-to-Digital Converter, ADC)采样得到数字信号,数字信号在可编程逻辑门阵列(Field Programmable Gate Array, FPGA)内的算法包括两个部分:一个是幅相环路算法,该算法根据ref和Pt的幅相差别,利用PI算法产生控制数模转换器(Digital-to-Analog Converter, DAC)的数字信号;另一个是频率跟踪算法,该算法根据Pf和Pt的相位差控制直接数字合成器(Direct Digital Synthesis, DDS)的输出信号频率,进而调整ADC和DAC的采样频率,最终改变馈入RFQ的微波信号频率。

|

图 1 频率追踪原理框图 Figure 1 Schematic diagram of frequency tracking |

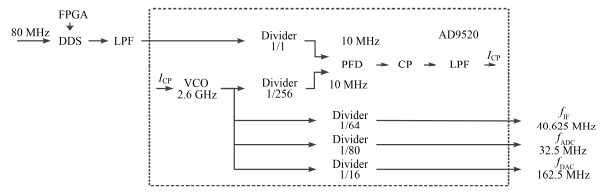

低电平控制系统工作时钟的产生是基于直接数字频率合成和锁相环(Phase-locked Loop, PLL)技术,时钟的产生和分配如图 2所示。DDS具有相位连续、分辨率高、频率转换速度快等优点[6],而PLL对杂散的抑制性能良好,将DDS和PLL两种频率合成技术结合起来,可以满足对输出频率进行精确控制的需求[7]。DDS的输出频率与工作时钟SYSCLK之间的关系满足:

|

图 2 时钟产生和分配 Figure 2 Clock generation and distribution |

| $ {f_{{\rm{out}}}} = \frac{{{\rm{FTW}} \times {\rm{SYSCLK}}}}{{{2^N}}} $ | (1) |

式中:SYSCLK是由信号发生器产生的;FTW (Frequency tuning word)是DDS的频率调谐字,由外部控制模块配置;N是内部位相累加器的位宽。从式(1)可以看出,DDS输出频率可以通过芯片内的FTW实时调整。本设计的参考频率是80 MHz,由外部信号发生器产生;DDS芯片采用Analog Devices公司的AD9858,该芯片带有可以工作到1G采样次数每秒(Sample Per Second, SPS)的10位DAC,100 MHz输出时的相位噪声145 dBc/Hz @ 1kHz;内部位相累加器位宽N为32。

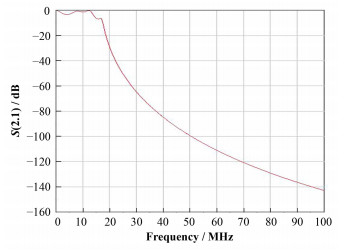

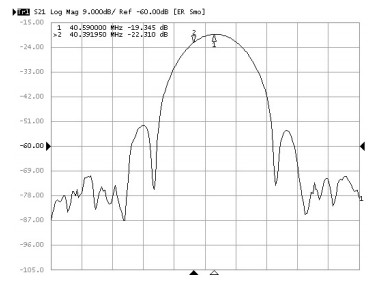

DDS根据FTW产生10 MHz的信号,该信号将作为PLL的参考信号,为了滤除其中的杂散成分,在DDS输出端与PLL的输入端之间引入了一个7阶π型LC低通滤波器。使用Advanced Design System软件可以得到该滤波器的传输特性(图 3)。本设计中DDS 10 MHz输出的混淆频率为70 MHz,从图 3可以看出,该频率可以得到有效滤除。

|

图 3 低通滤波器的正向传输系数 Figure 3 S(2.1) coefficient of the low pass filter |

时钟产生芯片选用Analog Devices公司的AD9520-0,该芯片内嵌一个锁相环和一个2.53~ 2.95GHz连续可调谐的电压控制振荡器(Voltage Controlled Oscillator, VCO),还提供多路时钟分配输出。DDS输出的10 MHz信号作为参考信号输入到AD9520-0。内部鉴频鉴相器(Phase Frequency Detector, PFD)的一个输入是该10 MHz参考信号,另一个输入通过设置除法器R和除法器N将VCO做260倍除法运算得到。PFD根据相位差控制电荷泵输出电压的大小,再用该电压微调压控晶体振荡器的频率,使得晶体振荡器输出的时钟频率和参考时钟频率锁定,从而实现时钟信号对参考信号的跟踪功能。电荷泵输出端的低通滤波器,可以减少锁相环的相位噪声,提高频率控制的准确度。利用AD9520-0提供的多路时钟分配输出,将VCO的输出频率做64倍分频得到40.625 MHz的参考信号fIF,做80倍分频得到ADC采样时钟信号fADC,做16倍分频得到162.5 MHz的DAC采样时钟信号fDAC。该时钟方案中,ADC工作在欠采样方式下,fIF/fADC=5/4;DAC工作在4倍采样方式下,fIF/fDAC=1/4。

1.2 频率跟踪控制环路的设计加速腔的输入信号Pf和腔上采样信号Pt的相位差是高频腔的失谐角φ,该角度存在关系[8]:

| $ \tan \varphi = 2{Q_{\rm{L}}}\left( {\frac{{{f_{\rm{r}}}-{f_{\rm{c}}}}}{{{f_{\rm{c}}}}}} \right) $ | (2) |

式中:fr是RFQ的谐振频率;fc是RFQ入射功率的频率;QL是RFQ的带载品质因子。从式(2)可以看出,腔的失谐状态可以通过测量失谐角φ得到。

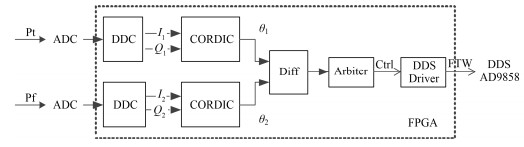

根据这一原理设计了一套频率跟踪算法,如图 4所示。腔前的输入信号Pf和腔上的采样信号Pt经过ADC数字采样后转换为数字信号,该信号首先经过数字下变频,得到正交的I分量和Q分量。数字下变频的方法是将ADC得到的数字信号与数字DDS算法产生的两组相位差90°的离散信号fcos和fsin相乘,得到正交的I、Q和−I、−Q。正交的IQ (In-phase and Quadrature)信号经过CORDIC (Coordinate Rotation Digital Computer)算法将IQ数字信号中的位相信息提取出来,对入腔信号Pf和腔上采样信号Pt的相位进行对比得到失谐角φ,进而可以知道腔的失谐状态。频率跟踪环路中引入了一个仲裁模块,该模块根据Pf和Pt的相位差来增加或者减小DDS的FTW值,使DDS输出频率变大或者减小,因为PLL的VCO与DDS输出信号是锁相的,所以PLL输出的时钟频率随之变化,使DAC输出信号的频率发生变化,最终使微波信号和RFQ的谐振频率处于锁定状态。

|

图 4 频率跟踪环路 Figure 4 Frequency tracking loop |

在实际应用中相位差会有一定波动,为了避免LLRF的输出频率发生频繁变化,我们设置了一个启动阈值,只有当失谐角绝对值超过启动阈值时才会启动频率跟踪功能。跟踪算法中的仲裁模块会根据相位差的符号确定频率调整的方向,使RFQ的输入频率逐渐逼近其谐振频率。当失谐角减小到阈值以下时,对DDS的频率调谐字的更新也会停止。该启动阈值在远程界面设置,经过通讯模块传输到FPGA。当冷却水达到热平衡之后,可以从远程界面关闭频率跟踪功能,使系统工作频率稳定。

1.3 幅相控制环路的设计RFQ腔内射频加速场的幅度和相位是由低电平控制系统的幅相环路控制的。如图 5所示,参考信号ref和RFQ的腔上采样信号Pt经过ADC进行模数转换,得到的数字序列通过数字下变频后得到正交的IQ数组,该数组反映了ADC输入信号的幅度和相位。对ref和Pt的I分量和Q分量分别做PI算法,得到用于信号还原的IQ数组,该数组经过还原算法得到可做D/A转换的数字序列,并用DAC还原为中频信号。在实际使用中,不论是调谐还是其他过程产生的幅相变化,都可通过该控制环路进行抑制,达到稳定RFQ内加速场幅度相位的目的。

|

图 5 幅相控制环路 Figure 5 Amplitude-phase control loop |

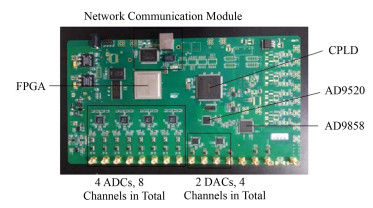

基于以上设计的硬件实物板卡如图 6所示。作为系统核心的FPGA选用Altera公司的Stratix Ⅱ EP2S64;ADC采用Linear公司的LTC2185,该款ADC是16位位宽、双通道,最高采样率达125MSPS;DAC采用Intersil公司的ISL5927,该DAC具有14位位宽、双通道,最高采样率达260MSPS。本文还引入复杂可编程逻辑器件(Complex Programmable Logic Device, CPLD)对ADC的工作模式进行配置。

|

图 6 数字信号处理板卡 Figure 6 Digital signal processing board card |

在实现的板卡中共有4路8通道ADC、两路4通道DAC、一块AD9858芯片、一块AD9520芯片、一个CPLD芯片,并采用100 M以太网模块与远程服务器进行通信。

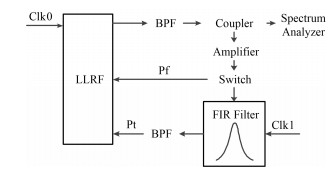

3 模拟腔测试实验平台原理如图 7所示,根据束腔相互作用的电路等效模型,高频腔的行为可以被等效为RLC电路[9],对于不同频率输入的响应相当于带通滤波器。本文的离线实验基于Altera公司Stratix Ⅱ数字信号处理(Digital Signal Processing, DSP)开发板设计了一个有限单位冲激响应(Finite Impulse Response, FIR)滤波器模拟高频腔,FIR滤波器频率响应如图 8所示,滤波器中心频率40.59 MHz,3 dB带宽0.4 MHz。

|

图 7 实验原理图 Figure 7 Schematic diagram of the experiment |

|

图 8 FIR滤波器频率响应 Figure 8 FIR filter frequency response |

根据离散时间傅里叶变换的时移和频移性质[10],当改变FIR滤波器工作时钟Clk1的频率时,滤波器的通带也会相应的产生移动,所以可以以此来模拟谐振频率的漂移。当系统的频率跟踪环路正常工作时,调整FIR数字滤波器的工作频率,使得模拟腔的中心频率从40.00 MHz变化到41.45 MHz,利用频谱仪测试LLRF的输出频率。测试结果如表 1所示,可以看出,LLRF的输出信号频率能跟随FIR滤波器的谐振频率。在实际测试中,为了防止对DDS的FTW进行频繁操作,DDS的操作阈值限制在1°。

| 表 1 LLRF输出频率随FIR滤波器中心频率的变化 Table 1 LLRF output frequency changes with FIR filter center frequency |

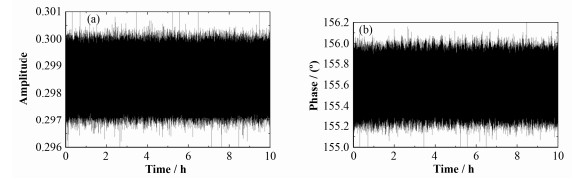

在频率跟随功能开启的状态下,我们进一步测试了幅相环路闭环下虚拟腔的幅度和相位稳定度,测试程序每0.1 s记录一次虚拟腔的幅度和相位信息,测试持续了10 h,测试结果如图 9所示。从图 9中可以看出,幅度稳定度达到±0.5%,相位稳定度达到±0.5°。

|

图 9 幅度稳定度(a)和相位稳定度(b) Figure 9 Amplitude stability (a) and phase stability (b) |

本文设计和实现了一种适用于RFQ的低电平控制系统,该控制系统可以实时跟踪RFQ的谐振频率,同时可以稳定RFQ加速场的幅度和相位。频率跟踪是基于DDS和PLL技术,通过分析馈入腔体的入射功率Pf和加速腔采样信号Pt的相位差推断出RFQ的失谐状态,最终改变馈入RFQ的微波频率,实现RFQ始终处于谐振状态的目标。在频率跟踪的同时,低电平控制系统还实现了RFQ加速场的幅相闭环控制,确保频率跟踪过程中加速场的幅度和相位稳定。本文引入以FIR滤波器为基础的虚拟腔搭建了离线模拟测试平台,验证了该方案的频率跟踪和幅相控制功能,测试结果表明:该方案能在对虚拟腔谐振频率进行跟踪的同时,实现±0.5%的幅度稳定度和±0.5°的相位稳定度。未来我们将会在实际使用的RFQ上进行在线测试。

| [1] |

Wangler T P. Principle of linear accelerators[M]. New York: John Wiley & Sons, Inc. 1998: 225.

|

| [2] |

Padamsee H, Knobloch J, Hays T, et al. RF superconductivity for accelerators[M]. New York: John Wiley & Sons, Inc. 1998: 44.

|

| [3] |

彭朝华, 关遐龄. 强流质子RFQ加速腔热特性分析[J]. 原子能科学技术, 2005, 39(2): 160-163. PENG Zhaohua, GUAN Xialing. Thermal analysis of high current proton RFQ cavity[J]. Atomic Energy Science and Technology, 2005, 39(2): 160-163. DOI:10.3969/j.issn.1000-6931.2005.02.014 |

| [4] |

Xin W Q, Ouyang H F, Xu T G. Resonance control cooling system for 973 RFQ at IHEP[J]. Nuclear Physics Review, 2013, 30(2): 136-139. DOI:10.11804/NuclPhysRev.30.02.136 |

| [5] |

Wang J, Huang J L, Zhang X Q, et al. Frequency tuning with RFQ temperature in China ADS injector Ⅱ[J]. Chinese Physics C, 2016, 40(3): 037003. DOI:10.1088/1674-1137/40/3/037003 |

| [6] |

董芳驰. 基于PLL实时跟踪DDS的高线性调频源技术研究[D]. 成都: 电子科技大学, 2008. DONG Fangchi. High linear frequency modulation source technology based on PLL real-time tracking DDS[D]. Chengdu: University of Electronic Science and Technology of China, 2008. |

| [7] |

王轶. 基于DDS PLL技术的高性能频率源研究与实现[D]. 长沙: 国防科技大学, 2004. WANG Yi. Research and realization of a highperformance frequency synthesizer based on DDS hybrid PLL[D]. Changsha: National University of Defense Technology, 2004. |

| [8] |

唐兴海, 刘亚娟, 张俊强, 等. 基于MicroTCA的自动频率控制系统[J]. 核技术, 2016, 39(7): 070102. TANG Xinghai, LIU Yajuan, ZHANG Junqiang, et al. An automatic frequency control system based on MicroTCA[J]. Nuclear Techniques, 2016, 39(7): 070102. DOI:10.11889/j.0253-3219.2016.hjs.39.070102 |

| [9] |

初晨, 黄贵荣, 金凯, 等. 储存环束流Robinson不稳定性的分析和测量[J]. 强激光与粒子束, 2011, 23(10): 2732-2736. CHU Chen, HUANG Guirong, JIN Kai, et al. Analysis and measurement of storage ring Robinson instability[J]. High Power Laser and Particle Beams, 2011, 23(10): 2732-2736. DOI:10.3788/HPLPB20112310.2732 |

| [10] |

Oppenheim A V, Willsky A S, Nawab S H. 刘树棠, 译. 信号与系统[M]. 二版. 西安: 西安交通大学出版社, 1998: 265-266. Oppenheim A V, Willsky A S, Nawab S H. LIU Shutang Trans. Signals and systems[M]. 2nd ed. Xi'an: Xi'an Jiaotong University Press, 1998: 265-266. |