2. 中国科学院粒子天体物理重点实验室 北京 100049;

3. 中国科学院大学 北京 100049

2. Key Laboratory of Particle Astrophysics, Chinese Academy of Sciences, Beijing 100049, China;

3. University of Chinese Academy of Sciences, Beijing 100049, China

星载数据总线是航天器中各设备之间完成通信、信息共享和数据交换的通道[1]。SpaceWire总线是欧空局(European Space Agency, ESA)与美国国家航空航天局(National Aeronautics and Space Administration, NASA)等国际空间组织合作,通过改进IEEE 1355的可靠性、功耗等,使其能更好地满足航空航天应用而提出的一种专门用于空间高速数据传输的总线标准[2]。目前已经在国外多个航天器上得到了应用,由于国内对这一技术有极大的需求,所以多家科研院所开展了航天器SpaceWire信息网络构建与知识产权核(Intellectual Property Core)的国产化研究,并取得了一些成果。γ射线监视器(Gamma Ray Monitor, GRM)采用SpaceWire总线进行科学、工程数据的收发以及和其他载荷之间进行信息共享。

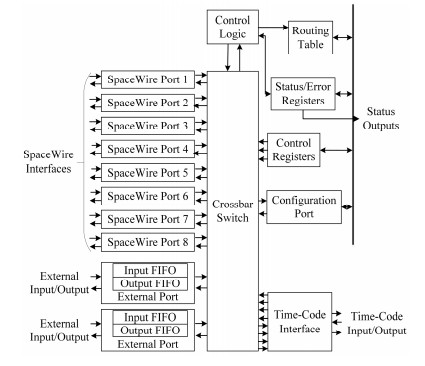

1 SpaceWire总线和GRM简介SpaceWire总线网络具有低成本、高速度、高容错等特点[3]。数据采用数据/选通编码(Data-Strobe encode, D/S),用低电压差分信号(Low-Voltage Differential Signaling, LVDS)进行传输,设计的通信速率为2‒400Mbit·s-1,目前最高可达到200Mbit·s-1,可实现点对点的传输或通过路由构造一个节点可达255个的星型网络;在同一网络中可同时使用多条总线,通过增加总线数量的方法可以成倍提高整个网络的数据传输速度[4]。GRM设计采用SpaceWire路由芯片AT7910,支持灵活的基于无阻塞交叉交换结构的路由,可连接任意输入端口到任意输出端口,符合SpaceWire标准[5],外部并行端口最多可达31个,包含输入FIFO (First Input First Output)和输出FIFO各一个[6],其结构如图 1所示。

|

图 1 SpaceWire路由框图 Figure 1 Block diagram of SpaceWire routing |

芯片有低功耗设计,当数据准备发送时端口可设置为自动启动,无数据发送时端口会自动停止以节省功耗。内部配置端口可通过交叉交换结构从任意SpaceWire的外部并行端口读写。

在2021年以后,国际上现有的γ射线暴触发探测卫星Swift/BAT(Burst Alert Telescope,爆发警示望远镜)、Fermi/GBM(Gamma-ray Burst Monitor,伽玛射线暴监视系统)、Integral等将进入寿命后期或者已经退役。中法合作太空望远镜项目天基多波段空间变源监视器(Space Variable Objects Monitor, SVOM)卫星搭载的载荷GRM,作为大面积、大视场、高探测效率的探测器,要完成硬X射线、软γ射线的能谱观测和γ暴(Gamma Ray Burst, GRB)触发等工作,并将与ECLAIRs(SVOM卫星法方载荷)共同成为γ暴发现触发的主要仪器,为其它多波段、多信使望远镜提供观测目标。

分系统单机电控箱是GRM的重要组成部分,电控箱的数据管理模块主要任务是对获取的数据进行组织管理形成物理数据包,采集系统的工作状态形成工程数据包,并与星上计算机通过SpaceWire总线数据接口实现物理数据和工程数据的交互。

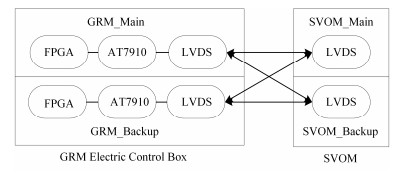

2 数据管理模块物理链路SpaceWire数据管理模块电路硬件上采用现场可编程门阵列(Field Programmable Gate Array, FPGA),它具有性能好、规模大、可重复编程、开发投资小等优点,已经大量应用于航天电子学的设计中。电控箱利用FPGA实现数据组织管理和通讯控制功能,完成基于SpaceWire总线的数据交互。选用的FPGA芯片为美国XILINX公司的Virtex-2系列,型号为XQ2V3000。利用LVDS接收/驱动器实现AT7910通信链路接口信号的转变。其链路如图 2所示。

|

图 2 数据管理模块物理链路框图 Figure 2 Block diagram of data management module physical link |

图 1中,AT7910共有8个通道(SpaceWire Ports),每个通道包括D/S发送[7]、D/S接收,共4个信号,工作速率2‒200Mbit·s-1,可根据需求通过芯片初始化配置,在允许范围内设置具体的速率。实际设计时选用8个接口中的两个,作为主备SpaceWire接口使用,工作速率设定为100Mbit·s-1。由于GRM电子学系统为冷热备份,SVOM卫星平台计算机同样为冷热备份,因此SpaceWire接口采用交叉备份方式,正常工作情况下,GRM的主备机和平台计算机的主备机同一时间都只会有一台处于开机状态。通过配置组路由以及判断端口状态寄存器的状态反馈,可以使GRM和平台计算机处于工作状态的设备之间的SpaceWire链路自动接通,并进行数据的收发。

2.1 物理层SpaceWire总线的物理层包括电缆、电连接器和电路板等。

SpaceWire电缆由4对双绞线组成,每对双绞线外部都有屏蔽层,整体外部也设有屏蔽层[8]。这样使得电缆具有较好的阻抗匹配、低信号衰减、良好的电磁兼容性等性能。

SpaceWire连接器采用专为航天应用设计的9针微型D型连接器,在电路板或者单元组件上采用母头接口,在电缆中采用公头接口[9]。

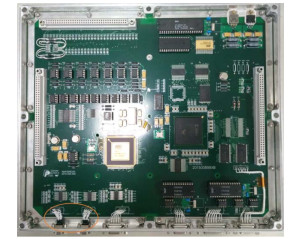

图 3是电路板实物图,其中左下圈中的两个就是SpaceWire的D型连接器。针对物理层的硬件电路,在项目下一阶段有相关的机、电、热一体化设计及环模试验,以此来保证载荷能满足环境要求。

|

图 3 电路板实物图 Figure 3 Photograph of the circuit board |

信号层主要包括LVDS技术、D/S编码技术以及总线接口。GRM的LVDS接口使用芯片SNV55LVDS31W和SNV55LVDS32W作为驱动/接收器。

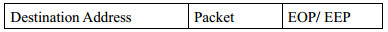

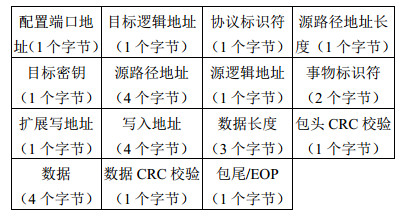

3 数据管理模块软件设计SpaceWire总线数据包层协议继承了IEEE1355-1995定义的数据包装协议,规定了总线源端到宿端的数据包装格式,其格式为:

|

其中:数据包地址(Destination Address)根据SpaceWire网络结构及传输路径情况来确定;包结束标志EOP (End of Packet)/EEP (Error End Packet),用于表示传输的数据包正确或错误。收到EOP/EEP末尾就默认数据包传输完毕,可以传输新的数据包。目标地址可以用物理寻址(Path Addressing)和逻辑寻址(Logic Addressing)两种方式[10]。GRM软件部分采用的是VHDL语言,通过FPGA控制AT7910芯片对数据进行操作。

3.1 端口基于AT7910芯片的SpaceWire总线设置有32个端口,每个端口都有对应的寄存器,通过对寄存器的控制,可以读取端口状态、对端口进行配置、查看端口反馈等。

32个端口中,端口0为配置端口,其他31个为外部并行端口。端口1~8是8个SpaceWire链路端口,9~10是两个外部FIFO端口。这10个物理端口都是双向的,可以同时经过同一个端口进行数据的接收和发送。端口11~31未使用。

芯片设置有状态寄存器,通过对寄存器地址位设置,可以将状态寄存器指向相应的10个物理端口,再通过读寄存器状态反馈得出所指向端口的具体状态。

3.2 配置配置芯片的功能是通过向配置端口0发送相应的配置数据包来实现的。配置数据包的格式及数据内容为:

|

包头地址为00h,收到EOP结尾代表数据包发送完毕。数据包中指定了被配置端口的逻辑地址、配置的数据内容、反馈的特殊识别字符等,其中含有包头循环冗余校验(Cyclic Redundancy Check, CRC)(Header CRC)和数据CRC校验(Data CRC)两段校验。

利用FPGA向外部端口(External Port)写入配置数据或者通过路由向SpaceWire端口写入配置数据,数据包都将被发送到配置端口。配置指令包采用的是CRC循环冗余校验,校验公式为x8+x2+x1+1,校验初始值00h。配置完成后,配置端口会发送状态反馈数据包,查看反馈数据包可以得到配置是否成功等状态。

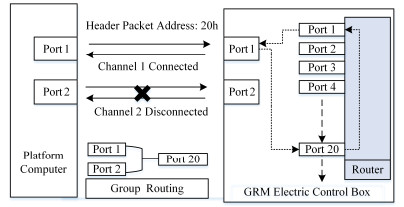

3.3 组路由AT7910构建的路由逻辑地址共有256个,其中0‒31是§3.1中所说的32个端口,地址32~255对应的是组路由的路由表地址。路由器能通过数据电缆和外部进行数据交换的端口包括8个SpaceWire端口和两个外部端口,对应着地址1~10。组路由实质上就是将这些端口中的一个或几个打包,形成一个组,给这个组赋予一个路由表中的地址,从而形成一个新的端口,如图 4所示。

|

图 4 组路由构造示意图 Figure 4 Structure diagram of group routing |

将端口1和端口2组合起来,赋予这个组合新的地址20h,就构成一个路由组。其中,配置组路由的数据包括需要打包成组路由的物理端口、路由组优先级以及包头删除等。

当向这个新的地址20h发送数据时,发送的数据会通过路由组指向的端口1或端口2发送出去。具体通过哪个端口发送,会按照以下几点规则:1)端口外部电缆断开、端口长时间不用等待超时,芯片为省功耗自动切断链接(有数据到来会尝试链接该端口,链接成功后可发送)、端口正在发送数据以及端口有数据等待发送且未等待超时这4种情况端口不可用;2)有唯一可用端口,则直接通过该端口发送;3)有多个端口可用时,编号小的端口具有高的优先级。

构造组路由对GRM的意义在于,GRM和平台计算机主备机采用互为冷备份的方式,同一时间各自只有一台设备处于开机运行状态。通过构造组路由可以在不了解双方哪台设备开机的情况下,只需要向组路由新的地址写数据,数据会自动通过组内端口发送往处于开机状态的设备。

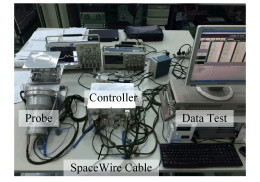

4 实验测试及结果分析 4.1 实验设备图 5是具体的实验设备,从左往右依次是探测器探头、电控箱、地检(代替卫星平台计算机功能)。电控箱中的数据管理模块通过两路SpaceWire电缆连接到地检设备。首先通过地检发送配置指令,FPGA向AT7910发送编好的配置数据包,将电缆连接的两端口配置为组路由。

|

图 5 实验设备 Figure 5 Photograph of experimental apparatus |

图 6为设计的实验方案框图。利用地检向SpaceWire链路的通道1发送事先准备好的文本数据文件,数据文件的包头地址为第一步构造的组路由的地址20h。SpaceWire芯片接收到读取的数据后根据包头地址将数据发往相应的端口,最终数据被地检接收并保存。实验发现,断开其中任意一路连接电缆,数据包会自动发往另外一个连通的通道,两个通道同时接通,数据发往端口1对应的通道1。另外,不从外面读取数据,直接通过FPGA发送一组数据同样可以成功收到发送的数据包,并且遵从上面所总结的规则。

|

图 6 数据发送与接收框图 Figure 6 Block diagram of data receiving and dispatch |

图 7所示的地检接收状态是断开通道2的电缆,通过地检向SpaceWire通道1的输入端口发送计算机上准备的数据文件,文件最终自动发往通道1,并通过输出端口被地检接收保存。通过读取配置组路由后配置端口的反馈数据,确认组路由配置成功。查看收到的数据内容也与发送内容一致。测试结果和上面总结的规律相符合。

|

图 7 地检数据接收状态 Figure 7 Data reception status |

通过本测试同时验证了上文所述的端口、配置、组路由等方面的功能设计以及总线收发数据、收发指令的功能,符合设计预期。

5 结语本文主要介绍了基于SpaceWire总线的GRM数据管理模块相关的设计,并重点讲述SpaceWire总线的物理链路构成和软件数据配置等功能。最后通过实验验证了数据管理功能,可以正常运行和符合设计要求。

| [1] |

陈湘陇, 经小川. 星载SpaceWire总线及其开发测试技术[J]. 现代测量与实验室管理, 2016(3): 30-33. CHEN Xianglong, JING Xiaochuan. Development and testing technology of Spaceborne SpaceWire bus[J]. Advanced Measurement and Laboratory Management, 2016(3): 30-33. |

| [2] |

吴中杰, 刘江澜, 宋伟. 可抢占实时星载Space-Wire总线网络研究[J]. 中国空间科学技术, 2016(6): 62-69. WU Zhongjie, LIU Jianglan, SONG Wei. A preemptible realtime SpaceWire on-board network[J]. Chinese Space Science and Technology, 2016(6): 62-69. |

| [3] |

Parkes S, McClements Cs, McLaren D. SpaceWire and SpaceFibre on the Microsemi RTG4 FPGA[C]. AERO 2016: IEEE Aerospace Conference Proceedings, 2016. http://www.researchgate.net/publication/305674198_SpaceWire_and_SpaceFibre_on_the_Microsemi_RTG4_FPGA

|

| [4] |

刘伟伟. SpaceWire路由器研制[D]. 哈尔滨: 哈尔滨工业大学, 2011. LIU Weiwei. Development of SpaceWire router[D]. Harbin: Harbin Institute of Technology, 2011. http://cdmd.cnki.com.cn/Article/CDMD-10213-1012000658.htm |

| [5] |

European cooperation for space standardization[ED/OL]. ECSS-E-ST-50-52C. [2010-02-05]. http://www.ecss.nl.

|

| [6] |

徐曙清, 王震. SpaceWire与SpaceFibre高速总线发展与研究[C]. 上海航天, 2014, 31(1): 31-36. XU Shuqing, WANG Zhen. Research and development of SpaceWire and SpaceFibre high speed bus[C]. Aerospace Shanghai, 2014, 31(1): 31-36. http://kns.cnki.net/KCMS/detail/detail.aspx?filename=shht201401006&dbname=CJFD&dbcode=CJFQ |

| [7] |

康咏岐. 面向航天应用的SpaceWire节点单元的IP核设计与实现[J]. 微电子学与计算机, 2005(9): 120-122. KANG Yongqi. The design and implementation of SpaceWire node IP core oriented space application[J]. Microelectronics and Computer, 2005(9): 120-122. |

| [8] |

王娜. SpaceWire总线节点接口的设计[D]. 哈尔滨: 哈尔滨工业大学, 2007. WANG Na. Design of SpaceWire node inter-face[D]. Harbin: Harbin Institute of Technology, 2007. http://cdmd.cnki.com.cn/article/cdmd-10213-2008193302.htm |

| [9] |

田华. SpaceWire总线在遥感卫星数传系统中的设计应用[J]. 电脑知识与技术(学术交流), 2007(14): 323-325. TIAN Hua. The design and application of SpaceWire for data transmission system of satellite[J]. Computer Knowledge and Technology (Academic Exchange), 2007(14): 323-325. |

| [10] |

McClements C, Parkes S, Kempf G. SpW-10X SpaceWire router user manual[R]. Austrian Aerospace, 2009.

|