2. 中国科学院高能物理研究所 粒子天体物理重点实验室 北京 100049;

3. 中国科学院大学 北京 100049

2. Key Laboratory of Particle Astrophysics, Institute of High Energy Physics, Chinese Academy of Sciences, Beijing 100049, China;

3. University of Chinese Academy of Sciences, Beijing 100049, China

硬X射线调制望远镜(Hard X-ray Modulation Telescope, HXMT)是我国第一个完全自主研制的空间X射线天文卫星。高能主探测器是其中的主载荷,由18个单体构成,总探测面积约为5000 cm2,探测能区20-250 keV[1]。主探测器采用NaI(Tl)/CsI(Na)复合晶体探测器,通过脉冲形状甄别(Pulse Shape Discrimination, PSD)技术来实现NaI(Tl)主信号的筛选和CsI(Na)本底信号的排除[2]。

在主探测器工程研制中,需要与之配套的测试设备,以便对其在各阶段和各试验环境中的物理性能进行测试和分析。由于探测器数量较多、且采用复合晶体技术,需要测试设备能够进行至少6路并行采集数据能力,能获取逐事例的脉冲幅度(0.2-2.5V)和脉冲宽度(1.2-3.5 μs)信息,实现能谱分析和PSD功能,并要求对59.5 keV光子的主探测器能谱分辨率的测试结果与Amptek生产的标准多道MCA8000D基本一致。

目前,国内外市场上通用的测试设备(如MCA8000D、MULTIPORT Ⅱ等)均不能满足需求。为此,从主探测器研制需求出发,采用现场可编程门阵列(Field Programmable Gate Array, FPGA)技术,并基于高速模数转换器(Analog-to-Digital Converter, ADC)采样原理,研制了一个8路高速并行采样的、可实现脉冲幅度和宽度同时测量的脉冲波形分析器。

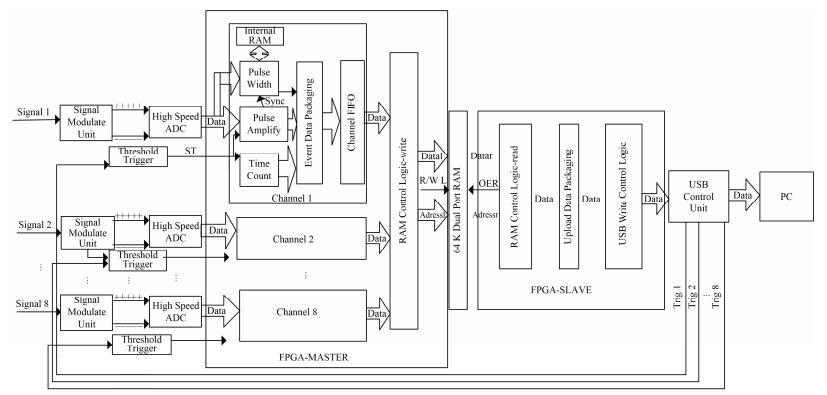

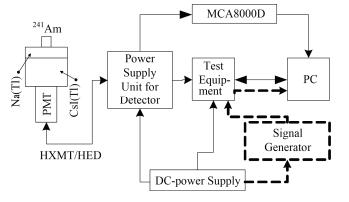

1 设备整体构架和工作原理脉冲波形分析器主要由信号调理单元(8路)、高速ADC(8路)、主FPGA芯片、双口随机存取存储器(Random-Access Memory, RAM)、从FPGA芯片和通用串行总线(Universal Serial Bus, USB)接口芯片构成,如图 1所示。ADC对信号进行高速采样,主FPGA芯片实现脉冲幅度测量、脉冲宽度测量和脉冲时间间隔统计功能,从FPGA芯片实现数据打包,并控制USB接口芯片实现数据上传和下载。

|

图 1 设备整体架构图 Figure 1 Diagram of the system. |

脉冲波形分析器的ADC采用了8组AD (Analog Devices)公司的AD转换芯片AD9215-105,该芯片采用单电源3.3 V供电,采样速率可达105MHz。FPGA采用Spartan3系列的XC3S400,208脚PQFP (Plastic Quad Flat Package)封装,可用最大输入输出(Input/Output, I/O)有141个,有40万门的逻辑资源,内部时钟频率可达320MHz。

脉冲信号采集过程为:单通道输入脉冲信号经过前端信号调理电路进行幅度变换后产生两路输出,一路至阈值触发电路,与上位机软件控制的触发阈值电平进行比较,生成触发信号;另一路经差分后送入高速ADC,并输出采样值和采样时间。过阈触发信号驱动主FPGA对ADC输出信息进行读取和存储,并在触发结束后开展信息的处理,获取脉冲幅度、脉冲宽度和脉冲到达时间,随即按照既定的格式整合成事例包,存入内部FIFO (First-In First-Out)区。主FPGA内的RAM写控制逻辑将检测到的FIFO区数据包写入外部双口RAM,作数据缓存,并由从FPGA的RAM读控制逻辑对双口RAM内数据进行读取和打包,最后通过USB端口实现数据的上传。

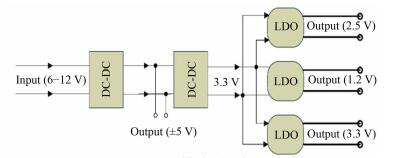

2 硬件设计 2.1 电源模块电源模块原理框图如图 2所示。采用DC-DC (Direct Current to Direct Current Converter)加LDO (Low Dropout Regulator)两级电源变换模式,其中DC-DC主要作电压变换,将输入电压变换到5 V,LDO做进一步的线性变换,稳定产生后续电路所需的各种电压。

|

图 2 电源模块原理框图 Figure 2 Diagram of the power supply module. |

该设计一方面使得脉冲波形分析器能够适应较宽电源电压环境,具有较强的抗外部电压波动能力;另一方面,通过LDO输出高稳定电压电平,保证后续数字电路稳定工作,实测LDO输出电源纹波≤10 mV。

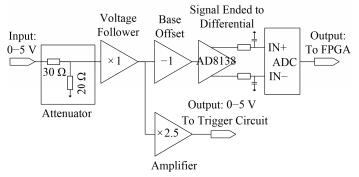

2.2 信号调理和ADC驱动信号调理模块包括衰减器、跟随器、放大器和单端转差分电路,如图 3所示。衰减器由30 Ω和20 Ω两个电阻串联构成,一方面将输入脉冲衰减至原来的2/5,作为后端电路输入;另一方面实现50 Ω的输入匹配,减小高频反射。衰减后的信号经过跟随器后分两路输出,一路经过-1 V基线偏置后在AD8138放大器内实现双极性差分输出;另一路通过放大器恢复至原初幅度大小,驱动触发电路,产生过阈使能信号。

|

图 3 信号调理模块构成 Figure 3 Diagram of signal conditioning module. |

设计中采用加法器来实现基线偏置,通过调整电路,使得输入0-5 V信号对应0-1024道,实现了ADC全通道利用,脉冲幅度测量精度约5 mV。FPGA内部DCM (Direct-Current Main)倍频产生96MHz高速时钟,利用时钟分配器CDCVF2510A将该时钟分为8路,为8个通道的ADC芯片提供了采样时钟。

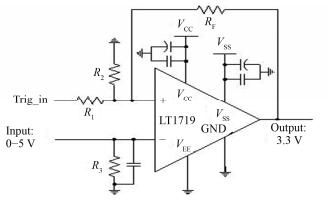

2.3 阈值触发电路用高速比较器LT1719实现阈值判选功能,该芯片采用双电源供电,输入和输出分别使用5 V和3.3 V电平,响应时间4.5 ns,输入输出上升时间和下降时间为2.5 ns,能够快速响应,产生触发信号。

图 4为阈值触发电路图,LT1719配置为滞回器,减少误触发[3],增强可靠性。其中比较器输出高电平VOH为3.3 V,低电平VOL为0,触发上阈为:

|

图 4 阈值触发电路 Figure 4 Threshold trigger circuit module. |

| $ {V_{{\rm{TH}}}} = {V_ + } + {V_{{\rm{Trig}}}}\frac{{{R_2}{R_{\rm{F}}}}}{{{R_1}\left( {{R_2} + {R_{\rm{F}}}} \right) + {R_2}{R_{\rm{F}}}}} $ | (1) |

其中:V+为高电平输出的贡献:

| $ {V_ + } = {V_{\rm OH}}\frac{{{R_1}{R_2}}}{{{R_{\rm{F}}}\left( {{R_1} + {R_2}} \right) + {R_1}{R_2}}} $ | (2) |

触发下阈为:

| $ {V_{{\rm{TL}}}} = {V_{{\rm{Trig}}}}\frac{{{R_2}{R_{\rm{F}}}}}{{{R_1}\left( {{R_2} + {R_{\rm{F}}}} \right) + {R_2}{R_{\rm{F}}}}} $ | (3) |

根据VTH和VTL表达式,并依据设计指标提出的触发上阈和下阈,可以确定各电阻的阻值。

触发阈值由上位机给出,通过USB下传至USB控制器,USB控制器按照通道及给定阈值,控制DAC (Digital-to-Analog Converter)转换为相应的阈值。这里采用的DAC为TI (Texas Instruments)公司生产的低速串行外设(Serial Peripheral Interface, SPI)接口DAC芯片TLV5638,其接口简单,无需复杂外部电路。

2.4 双端口RAM和USB 2.0接口设计数据在传输过程中,可能出现脉冲信号的堆积,特别是多通道同时产生触发时,数据量将大大增加,而USB上传过程受到USB 2.0速度限制,且上传过程可能出现上位机读取数据的延迟,因此有必要对数据进行缓冲。本系统设计了一个大容量的双端口RAM,完成主从两个FPGA间数据的交互与缓冲。

USB 2.0模块采用Cypress公司的CY7C68013A芯片,该芯片内部集成8051内核,EZ-USB内集成USB收发器、智能串行接口引擎SIE (Serial Interface Engine)和PLL (Phase Locked Loop)组成的USB 2.0物理层协议处理器,可以完成大部分USB 2.0协议处理,这使得用户不必花太多的时间在USB协议上,大大加快了开发过程。该USB芯片的设计主要外部电路为时钟、复位和PROM (Programmable Read-Only Memory)的电路。参照Cypress参考文档《EZ-USB TRM》[4]进行设计。

3 软件设计系统固件代码主要包括主、从FPGA代码和USB固件代码。主FPGA内部主要模块为:脉冲幅度分析模块、脉冲宽度分析模块、时间测量模块、数据整合模块、内部RAM、通道FIFO、外部RAM控制模块。从FPGA内部主要模块为:RAM读控制模块、数据打包模块、USB写入控制模块(图 1);USB 2.0的设计主要分为上传数据固件代码、下传数据控制代码和阈值控制的代码。

当输入的脉冲信号前沿超过比较器的高阈值时,即产生过阈使能信号start,主FPGA持续将ADC输出(96 MHz,逐点采样)的波形数据读出,并写入内部RAM,直至脉冲信号后沿低于比较器低阈值,触发电路产生stop信号,FGPA停止读取。数据读取结束后,脉冲幅度分析器读取RAM中每一个采样点的道址,并做比较,获取最大数值作为脉冲幅值;脉冲宽度分析器检测出30%脉冲幅值所对应的脉冲上升沿、下降沿时间,取后者与前者的差值作为脉冲宽度值。脉冲过阈触发时间即为脉冲到达时间。主FPGA模块提取脉冲信号后传输给从FPGA模块,后者将对数据进行打包处理,并控制USB实现数据上传。

在CY7C68013中,数据上传支持两种模式:Slave FIFO模式和GPIF (General Programmable Interface)模式[5]。本文采用Slave FIFO模式,FPGA只需对USB端点当作FIFO写入数据即可,芯片自动将数据上传至PC。而阈值的下传则由控制传输完成,主机给出通道与需设置的阈值信息,由微控制器解码并控制相应的DAC完成转换输出,控制信号过阈值。

4 性能标定及能谱测量图 5为基于FPGA的脉冲波形分析器的电路设计实物图,图 5中简要标识了各区域的功能。在完成电路设计和调试之后,利用信号发生器(图 6中虚线连接部分)产生幅度0.05-5 V、宽度0.1-9.5 μs的脉冲信号,分别测试了波形分析器的信号宽度、幅度、时间响应特性,拟合得到脉冲幅度响应函数(1通道)为:Vout=0.9997Vin+0.00007,其中,Vout为脉冲波形分析器响应的信号幅度,V;Vin为输入脉冲信号幅度,V。积分非线性 < 0.07%。宽度(峰值30%处的宽度)响应函数(1通道)为:Wout=1.008Win+0.008,其中,Wout为脉冲波形分析器响应的信号宽度值,ns;Win为输入脉冲信号宽度,ns。积分非线性 < 0.57%。图形结果见文献[6]。测试结果表明,脉冲幅度波形分析器具有良好的脉冲幅度和脉冲宽度线性响应关系。综合标定后的脉冲波形分析器的主要性能参数见表 1。

|

图 5 脉冲波形分析器实物图 Figure 5 Pulse shape analyzer. |

|

图 6 MCA标定测试系统和HXMT/HED性能测试系统 Figure 6 Diagram of energy spectrum measurement system. |

| 表 1 脉冲波形分析器的主要性能参数 Table 1 Performance parameters of the pulse shape analyzer. |

可见脉冲幅度波形分析器具有采样精度高、分析波形幅度和宽度范围广、通道数多、系统供电范围宽、具备PSD功能等特点。

按照图 6实线部分所示的测试方法,用脉冲波形分析器对实际的主探测器性能进行测量。241Am为放射源,主探测器(High-Energy Detector, HED)(由NaI(Tl)/CsI(Na)复合晶体、光电倍增管(Photomultiplier Tube, PMT)和电子学构成[1])做X/γ探测及光电转换(图 6中HXMT/HED为主探测器结构简图),测试设备(即脉冲波形分析器)实现数据分析及存储。

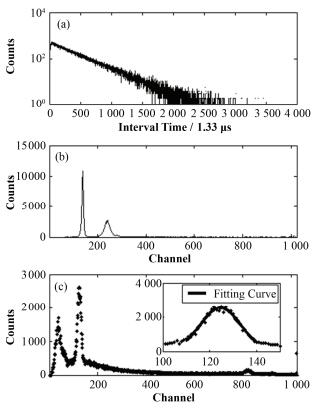

通过上位机软件读出数据并显示,得到如图 7所示结果。其中图 7(a)为脉冲信号到达时间间隔谱,符合指数分布,表明系统中对事例的定时功能正常;图 7(b)为脉冲信号宽度谱,左峰为NaI(Tl)信号,右峰为CsI(Na)信号,两峰分离显著,通过设定脉冲宽度阈值即可实现PSD甄别功能;图 7(c)为脉冲信号幅度谱,最高峰为241Am衰变产生的59.5 keV的γ射线光子形成的全能峰。

|

图 7 实测主探测器对241Am放射源的能谱(a)时间间隔谱,(b)宽度谱,(c)幅度谱 Figure 7 Energy spectrum of 241Am. (a) Pulse interval spectrum, (b) Pulse width spectrum, (c) Pulse amplitude spectrum |

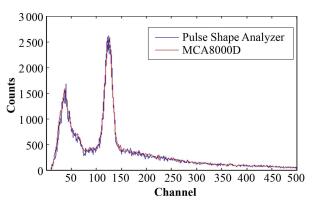

利用PSD甄别技术剔除CsI(Na)成分,对NaI(Tl)成分做统计,并做拟合得到其能量分辨率为(14.0±0.3)%@59.5 keV,与标准测试设备MCA8000D所得的(14.2±0.3)%@59.5 keV一致(图 8),表明脉冲波形分析器性能良好,达到HXMT/HED性能测试要求。

|

图 8 脉冲波形分析器与MCA8000D对241Am放射源所测能谱比较 Figure 8 Energy spectrum of 241Am by pulse wave analyzer and MCA8000D. |

基于FPGA和高速ADC技术,设计了一个8通道脉冲波形分析器,它具有8路高速并行采样、幅度分析、宽度分析、时间测量等功能,能够对幅度0-5 V、宽度0.1-9.5 μs (30% Vpp)的单极性正脉冲信号进行准确的测量,满足HXMT卫星高能主探测器的电性测试要求,并已运用于HXMT卫星项目研制中。

本测试设备具备小型、便携特点,具有多通道、PSD功能,在辐射探测领域具有广泛的应用前景。

| [1] |

张翼飞. HXMT硬X射线探测器性能研究[D]. 北京: 中国科学院高能物理研究所, 2011.

ZHANG Yifei. Study of performance of HXMT hard X-ray detector[D]. Beijing:Institute of High Energy Physics, Chinese Academy of Sciences, 2011. http://www.irgrid.ac.cn/handle/1471x/376716?mode=full&submit_simple=Show+full+item+record |

| [2] |

李延国, 李惕碚. 新型脉冲形状甄别器[J].

核电子学与探测技术, 2003, 23(5): 391–396.

LI Yanguo, LI Xipei. New type of pulse-shape analyzer[J]. Nuclear Electronics & Detection Technology, 2003, 23(5): 391–396. DOI: 10.3969/j.issn.0258-0934.2003.05.002 |

| [3] |

刘黎辉. 高速迟滞比较电路研究及实验[J].

电子测量技术, 2007, 30(2): 46–49.

LIU Lihui. Research and experiment of high-speed comparing circuit with hysteresis[J]. Electronic Measurement Technology, 2007, 30(2): 46–49. DOI: 10.3969/j.issn.1002-7300.2007.02.015 |

| [4] | EZ-USB FX2 technical reference manual[R]. Version 2.2. San Jose, CA, USA:Cypress Semiconductor Corporation, 2000. |

| [5] |

蒋金涛, 杨鸣. USB 2.0控制器EZ-USB-FX2的性能特点及其数据传输实现[J].

计算机工程与应用, 2005, 41(11): 94–96.

JIANG Jintao, YANG Ming. The features of EZ-USB-FX2 and the implementation of data transfer[J]. Computer Engineering and Applications, 2005, 41(11): 94–96. DOI: 10.3321/j.issn:1002-8331.2005.11.030 |

| [6] |

李继承. HXMT高能主探测器探头地面测试设备研制[D]. 云南: 云南大学, 2016.

LI Jicheng. Design and performance of the on-ground measurement system for the HED on board HXMT[D]. Yunnan:Yunnan University, 2016. http://cdmd.cnki.com.cn/Article/CDMD-10673-1016201009.htm |