2. 西北核技术研究所 西安 710024

2. Northwest Institute of Nuclear Technology, Xi'an 710024, China

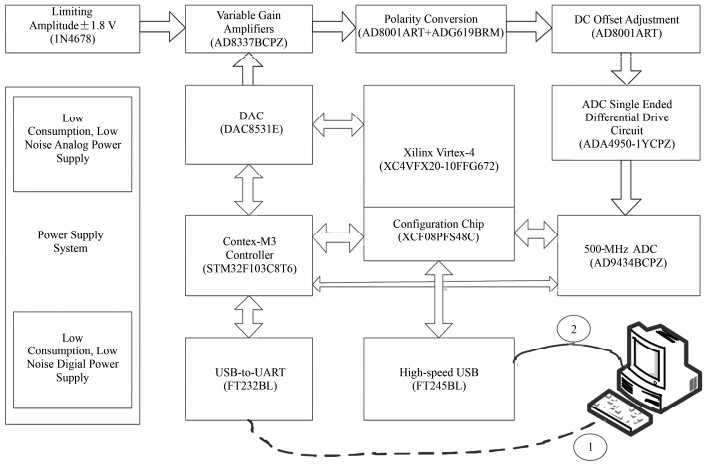

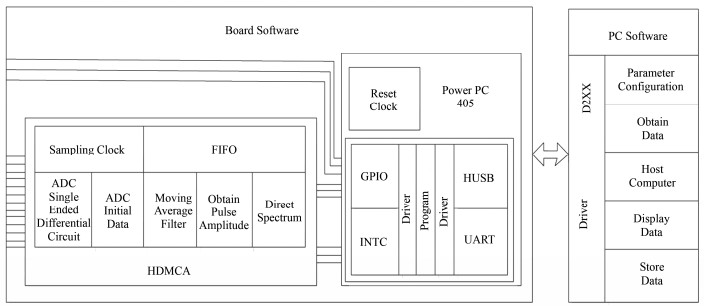

在粒子物理领域,通常需要采用高速数字化方法对探测器输出的电流脉冲信号进行实时波形分析,从而实现粒子的甄别;在核退役设施及高能物理实验中,通常需要进行高通量的粒子能量的测量,为此常规的模拟多道脉冲幅度分析器、百兆赫兹以下的数字多道脉冲幅度分析器都无法满足使用要求。电流脉冲信号通常宽度仅为几十纳秒甚至更短,为此需要设计直接耦合方式的高速模拟前端电路,否则电流脉冲波形会发生畸变,严重时发生信号反弹,因此会影响脉冲波形甄别效果,也就使粒子甄别效果大幅度下降。实现高计数率的数字化多道,要求多道系统具有更高的采样率,从而能对比较窄的脉冲信号较为准确地提取脉冲的幅度,并保证有高的脉冲计数通过率。为此采用了如图 1所示的硬件设计,通过最少的必要硬件配合各种数字信号处理方法,实现不同的测量功能和任务,大大提高了整个系统的灵活性、适应性、抗干扰性,获得优异的能量分辨率和数据传输速率。

|

图 1 手持单板高速数字多道的硬件系统框图 Figure 1 Block diagram of hardware system of high speed digital multi-channel with single board |

在能谱仪系统中模拟前端电路通常采用直接耦合方式设计,这样可减小因交流耦合带来的噪声增加、极零点增加、脉冲过冲、幅度亏损等问题。一般的高速模数转换都采用交流耦合方式设计,降低了对模拟带宽的要求,单端差分转换的设计也更加容易,但却无法满足能谱仪系统的要求。本文设计的直接耦合电路带宽为DC-100 MHz,具备自动极性转换、压控增益调节、直流漂移调节等功能。

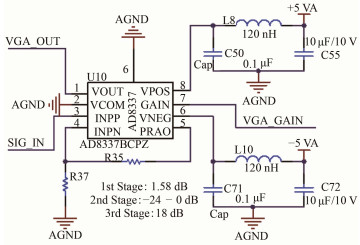

1.1 压控增益调节本系统采用数字模拟转换器 (Digital-to-Analog Converter, DAC)+可变增益放大器 (Variable Gain Amplifier, VGA) 的拓扑结构,并选择了可进行视频信号放大的AD8337压控增益放大器,其小信号的-3 dB带宽达到280 MHz,大信号的带宽也达到了100 MHz,超低电压噪声2.2 nV/

|

图 2 AD8337压控增益调节电路 Figure 2 AD8337 voltage controlled gain control circuit |

| $G = 19.7{V_{\text{G}}} + {I_{\text{c}}}$ | (1) |

式中:VG为增益调节电压,一般在-0.6-+0.6 V;Ic为增益直线在Y轴上的截距,一般为12.65 dB,可以通过前级放大设定。为了实现增益调节,采用16bit分辨率的DAC8531输出-0.6-+0.6 V电压,实现-4.5-19.5 dB的增益调节。

1.2 极性转换与直流漂移调节本文采用AD8001高速电流型运算放大器为核心构成极性转换与直流漂移调节电路。选用AD619BRM高速模拟开关实现对模拟信号的切换。在直接耦合方式下,如果不对核脉冲信号施加直流偏移量,则实际高速模数转换器 (Analog-to-Digital Converter, ADC) 的有效电压范围则会缩减一半,显然不利于能谱采集,为此需要将单极性的核脉冲信号施加接近-1 V的直流偏移,从而有效利用ADC输入电压动态范围。

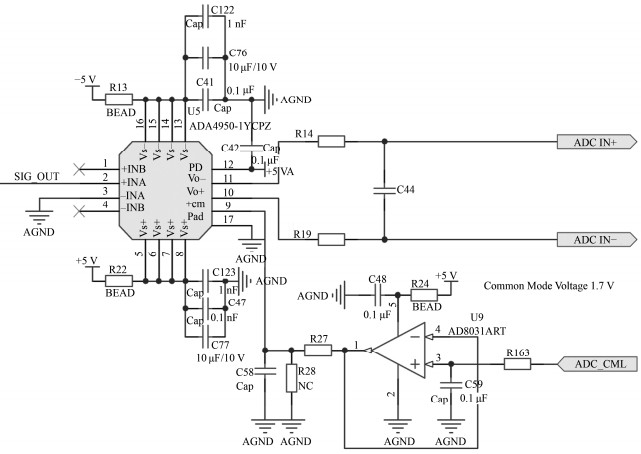

2 高速ADC电路设计高速ADC电路设计主要包括ADC差分驱动电路设计、低抖动时钟设计、ADC外围电路设计。在高速ADC设计中,差分输入方式相比于单端输入方式具有更高的共模抑制比,且对运算放大器的压摆率要求降低一倍,更容易实现对高速模拟信号的采样。系统中前端输入的为单端信号,故选用ADA4950单端转差分芯片实现差分驱动,该芯片功耗低,内部自带一致性优异的增益电阻,可提高共模抑制比,-3 dB带宽可达750 MHz,压摆率达2900V·μs-1。单端转差分的设计难点在于匹配电阻的设计,故采用美国Analog Devices Incorporation (ADI) 公司官网的专用软件Diff-Amp Calculator设计,最终设计完成的ADC差分驱动电路如图 3所示。

|

图 3 ADA4950单端转差分驱动电路设计 Figure 3 Design of ADA4950 single ended differential drive circuit |

ADC的选择需要综合考虑多种因素,譬如现场可编程逻辑门阵列 (Field-Programmable Gate Array, FPGA) 的最快时序速度、分辨率、噪声、数据接口、功耗、非线性、价格与采购等[2-3]。为此本文选择了ADI公司的AD9434-500高速ADC,该ADC具有12 bit分辨率,500 MHz采样率,非线性积分 (Integral Non-Linearity, INL) 与非线性微分 (Differential Non-Linearity, DNL) 低,全带宽功耗仅为0.68 W,采用低电压差分信号 (Low-Voltage Differential Signaling, LVDS) 的单倍数据速率 (Single Data Rate, SDR) 方式传输数据,具体的ADC外围电路设计限于篇幅可参考芯片的数据手册。

在高速ADC采样电路设计中,低抖动时钟的设计至关重要,直接影响了采样精度,甚至影响FPGA中的数字滤波成形的效果[4]。本文采用美国CRYSTEK公司的CVS575S-500.000有源晶振,其输出的500 MHz频率信号经过ADT1-1WT变压器转差分后,通过交流耦合方式进入ADC的差分时钟端,差分端口使用HSMS2812双向肖特基二极管保护。为了保证时钟的低抖动,设计如下:设ADC为n位,有效时钟信号幅度为V,频率为f,则ADC时钟等效信号公式为:

| ${{V}_{t}}=V\sin (2\text{ }\!\!\pi\!\!\text{ }ft)$ | (2) |

晶振最快有效斜率公式为:

| $\frac{\text{d}V}{\text{d}t}{{|}_{\max }}=2\text{ }\!\!\pi\!\!\text{ }fXV$ | (3) |

最大孔径误差公式为:

| ${{E}_{\text{A}}}={{T}_{\text{A}}}\frac{\text{d}V}{\text{d}t}{{|}_{\text{max}}}=2\text{ }\!\!\pi\!\!\text{ }fXV{{T}_{\text{A}}}\le 0.5\text{LSB}=\frac{2V}{{{2}^{n+1}}}$ | (4) |

故:

| ${{T}_{\text{A}}}\le \frac{X}{\text{ }\!\!\pi\!\!\text{ }f{{2}^{n+1}}}$ | (5) |

本系统采用12位500 MHz采样率ADC,式中:X为晶振输出幅度与ADC有效时钟幅度之比,因晶振输出幅度为3.3 Vpp,ADC有效时钟幅度为0.2 Vpp,所以TA≤2.2 ps即可,CVS575S-500.000手册提供其抖动频率≤1 ps,可以满足需求。

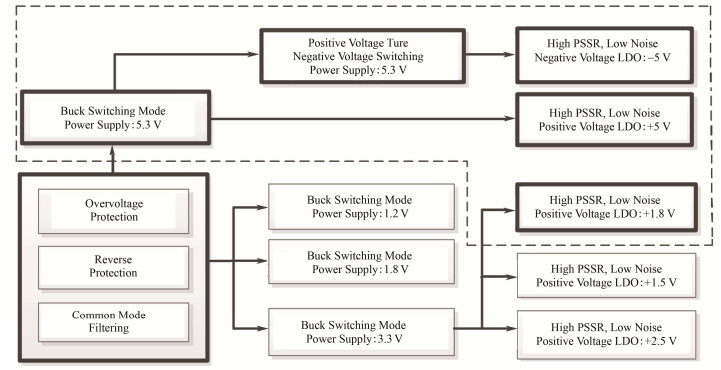

3 FPGA与供电电源设计单板设计的数字化多道通常采用多供电设计,而多道中的放大器、高速ADC、FPGA等需要不同电压、不同功率、不同噪声要求的电源设计,为此电源设计好坏直接决定了脉冲信号幅度提取的效果[5]。本文采用了高频开关电源与线性低压差电源相结合的方式设计,如图 4所示。所选择的高频开关电源芯片的开关频率都大于兆赫兹,原因在于更高频率的开关噪声,经过FPGA内部的数字滤波后,更容易给滤除,反而低频率的开关电源芯片,其开关噪声难以通过数字滤波方法滤除[6]。但更高转换频率会牺牲一部分的转换效率。为了进一步降低模拟电路部分供电噪声,设计了高电源抑制比 (Power Supply Rejection Ratio, PSRR) 的低压差线性稳压器 (Low dropout regulator, LDO) 串联在开关电源之后,用以消除更高频率段的噪声,减小对敏感、微弱信号放大的模拟电路的影响。

|

图 4 系统电源设计框图 Figure 4 Design of system power supply |

高速信号转换与采集系统中,系统完整性设计是保证采样信号质量的关键,包括了信号完整性与电源完整性。信号完整性需要考虑反射、振荡、地弹、串扰、阻抗匹配、印制电路板 (Printed Circuit Board, PCB) 走线;电源完整性需要考虑模拟地与数字地分割设计、不同电流走线分开设计、采用滤波技术减小噪声等。在PCB布局布线时要考虑3W原则、20H原则、5-5原则,信号线与高频线尽量走直线,布线时的过孔尽量减少,差分时钟线与信号线应等长布线。

5 系统软件设计系统软件设计包括板级软件与PC机端软件,如图 5所示。板级软件采用FPGA内部自带的PowerPC硬核与高速数字脉冲幅度提取模块 (High Digital Multi-Channel Analyzer, HDMCA)[7]。PowerPC硬核设计运行速度为300 MHz,可实现高速通用串行总线 (Universal Serial Bus, USB)、异步串行通信接口、数据存储发送以及与幅度提取模块之间的数据交互。

|

图 5 系统软件设计框图 Figure 5 Design of system software |

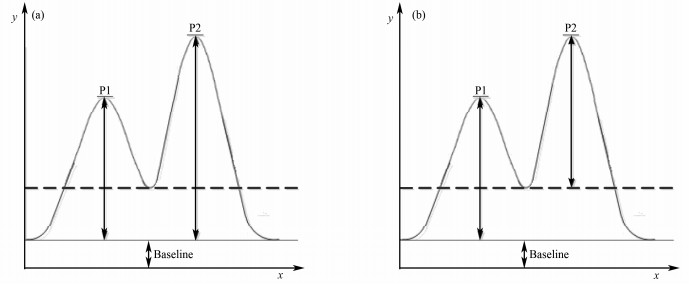

由于本文设计的采样速率达500 MHz,故数字梯形成形、数字高斯成形等数字滤波算法难以如此高的频率实时运行,故采用如图 6所示的两种直接成谱方式获取谱线[8]。其中:方式a为不考虑峰堆积的情况,每次获取P1峰的最大值;方式b为考虑峰堆积的情况,提取P1和P2峰值,P1为对应基线的峰值,P2为对应峰谷的峰值。实际应用时当计数率高时可选用方式b,反之选用方式a。方式a与b都可以自动提取基线值。本文采用信号上升沿斜率的大小作为信号触发的判断条件,在不满足触发条件时则持续采样获取基线值,当信号触发时,以触发前采样得到的数值作为基线,并加以扣除,从而实现基线扣除功能。

|

图 6 两种直接成谱方法 Figure 6 Two direct spectral methods |

本文设计的单板式500 MHz采样率的数字化多道实物图如图 7所示。

|

图 7 单板500 MHz数字化多道实物图 Figure 7 Physical picture of single board 500-MHz digital multi-channel |

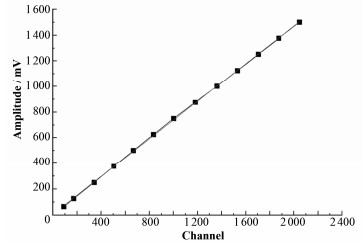

表 1为脉冲通过率测试。由于高计数率的随机脉冲信号发生器较难获得,本文采用通用函数信号发生器产生周期性方波信号,经过CR微分后得到指数信号,输入到多道,测试其脉冲通过率。从表 1可知,当输入信号频率达到11 MHz时,获取谱线的有效计数为1.033571×107 s-1。造成谱线下降的主要原因在于PowerPC405硬核与幅度提取模块之间的数据通信吞吐量设计瓶颈,而触发信号计数则会出现堵塞情况。因此改进硬核的设计可以大幅度提升系统的脉冲计数通过率。图 8为脉冲信号幅度值测量线性度的测试结果,由图 8可知,线性度可高达0.99982,基本符合多道的使用要求。

| 表 1 脉冲通过率测试 Table 1 Test of pulse pass rate |

|

图 8 脉冲信号幅度测量线性度测试 Figure 8 Linearity test of pulse signal amplitude measurement |

采用研制的500 MHz采样率的直接成谱方式的数字多道分别对NaI+光电倍增管 (Photomultiplier tube, PMT)、LaBr3+光电二极管 (Avalanche Photo Diode, APD) 和掺硼塑料闪烁体+PMT三种探测器进行谱线采集。

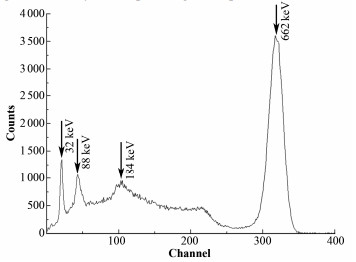

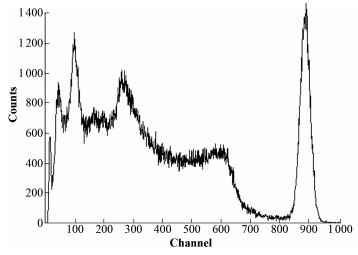

图 9为NaI闪烁探测器在137Cs源正对探测器方向照射实测得的谱线,由于NaI晶体体积较大、PMT光电转换速度快、放大倍数高、灵敏度高,所以从图 9可以看出,能谱的峰均能较为清楚地分辨出:最左边为Ba的特征X射线,能量为32 keV;左二为Pb的特征X射线,能量为88 keV;左三为反散射峰,能量为184 keV;最右边为137Cs的全能峰能量为662 keV,其峰康比、峰谷比相对较好,能量分辨率为6.8%。显然相比于常规的基于数字梯形成形数字多道方式,能量分辨率虽然偏差,但其脉冲通过率则要高的多。

|

图 9 NaI+PMT探测器的测量谱线 Figure 9 Measurement spectral line of NaI+PMT detector |

图 10为Ø15 mm×15 mm的LaBr3与10 mm× 10mm的APD光电转换芯片耦合成探头,并采用137Cs源照射实测出能谱,与PMT的能谱图相比其峰康比、峰谷比偏小,其能量分辨率为4.05%。

|

图 10 LaBr3+APD探测器的测量谱线 Figure 10 Measurement spectral line of LaBr3+APD detector |

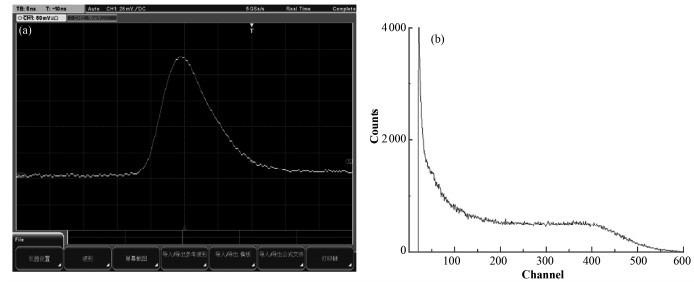

图 11(a)为掺硼塑料闪烁体配合滨松R1704光电倍增管实测的阳极电流脉冲信号,脉冲宽度约为30 ns;图 11(b)为137Cs实测能谱曲线,由于塑料闪烁体的平均原子序数小,γ射线穿过探测器时,光电效应截面小,无明显光电峰,因此谱线中主要为康普顿散射本底。

|

图 11 掺硼塑料闪烁体+PMT探测器的电流脉冲信号 (a) 与实测能谱 (b) Figure 11 Current pulse signal (a) and measurement spectrum (b) of boron plastic scintillator+PMT detector |

基于500 MHz采样率的嵌入式单板数字化脉冲处理器针对107s-1计数率的能谱获取具有一定的优势;针对中低计数率场合的能谱获取优势并不明显,因其分析速度快难以实现梯形成形、尖顶成形等数字滤波成形算法,只能采用直接幅度提取方法,故幅度提取效果劣于数字成形的脉冲处理器。针对塑料闪烁体的中子、伽马粒子波形甄别,目前的实验效果不尽如人意,还需进一步提高采样率到GHz。

| [1] | Brandenburg D.Current vs.voltage feedback amplifiers[Z].National Application Note OA-30, 1998:1-4. |

| [2] | Furuta F, Saitoh K, Yoshida A, et al. Characterization of sigma-delta modulator with LR-type integrator for superconducting analog-to-digital converter[J]. Physica C, 2007, s463-s465(1-2): 1092–1095. |

| [3] | Yang L J, Zhu X F, Liu S M. Measurement techniques for spurious free dynamic range of analog to digital converter[J]. IERI Procedia, 2013, 4: 195–200. DOI: 10.1016/j.ieri.2013.11.028 |

| [4] |

李艳平.高速时钟信号抖动的ADC测量技术研究[D].成都:电子科技大学, 2009.

LI Yanping.Research on ADC measurement technology of high speed clock signal jitter[D].Chengdu:University of Electronic Science and Technology of China, 2009. |

| [5] |

曾国强, 葛良全, 倪师军, 等. 数字化X荧光仪电源的最优化设计[J].

核电子学与探测技术, 2012, 6(20): 719–723.

ZENG Guoqiang, GE Liangquan, NI Shijun, et al. Optimized design of digital X-ray fluorimeter power supply[J]. Nuclear Electronics and Detection Technology, 2012, 6(20): 719–723. |

| [6] | Bolic M, Drndarevic V. Digital gamma-ray spectroscopy based on FPGA technology[J]. Nuclear Instruments & Methods in Physics Research, 2002, 482(3): 761–766. |

| [7] |

熊明霞.基于PowerPC的SOPC平台构建[D].北京:中国科学院电子研究所, 2007.

XIONG Mingxia.Construction of SOPC platform based on PowerPC[D].Beijing:Institute of Electrics, Chinese Academy of Sciences, 2007. |

| [8] |

王敏, 方方, 曹建宇, 等. 基于FPGA的数字脉冲成形技术的研究[J].

测控技术与仪器仪表, 2013, 39(7): 87–92.

WANG Min, FANG Fang, CAO Jianyu, et al. Study of digital pulse forming technology based on FPGA[J]. Measurement Control Technology and Instruments, 2013, 39(7): 87–92. |