对核信号信息的获取与处理可揭示辐射探测实验背后的物理规律[1]。随着电子技术的发展以及大规模、高精度实验的兴起,对核信号信息获取与处理的要求也越来越高。

在对宽量程、高精度的辐射探测实验进行数据获取时,国外研究人员更多采用商用数字化仪。国外商用数字化仪的特点是性能稳定,并能够对电子学噪声很好进行控制。截止到现在,国外数字化仪噪声水平最好的是美国GaGe公司生产的CS16X1,在输入信号满量程为2 V的情况下,其噪声水平为122.7 μV[2]。但是国外数字化仪价格昂贵,并且对国内很多单位禁运。所以,国内很多单位更多采用自主研制的波形数字化电路。到目前为止,国内公开文献报道采样率在100 MSPS以上的波形数字化电路中,最低噪声水平为527 μV[3]。

而对核信号信息的精确获取需要降低电子学的噪声水平。在核电子学中,噪声来源有电子器件本身和外部噪声[4]。电子器件的噪声通常由载流子的随机运动和载流子数量的涨落引起,如导体或电阻中的自由电子作不规则的热运动;电子管阴极的热电子发射;半导体内载流子的产生和复合过程,都会引起电流和电压的波动而产生噪声[5]。外部噪声包含供电电源噪声、数字电路噪声干扰和外界电磁干扰。本文从减小模拟电路噪声、降低数字电路和电源干扰方面对低噪声波形数字化电路的设计进行了研究。

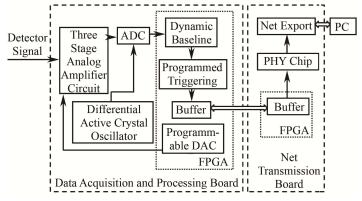

1 电路总体结构该电路系统设计由两个电路板组成:数据采集及处理板和网络传输板。而在数据采集及处理板上又可分为模拟电路部分和数字电路部分。图 1为该电路系统的结构示意图;图 2为电路实物图。

|

图 1 电路结构示意图 Figure 1 Schematic diagram of circuit structure. |

|

图 2 电路实物图 Figure 2 Circuit physical diagram. |

在模拟电路部分,由三个放大器构成[6]。第一个放大器接入探测器信号,对信号进行缓冲和匹配;第二个放大器接入第一级输出和数字模拟转换器(Digital-to-Analog Converter, DAC),用来设置不同的基线以适应模拟数字转换器(Analog-to-Digital Converter, ADC)的动态范围;第三个放大器接第二级输出,将单端信号转为差分信号以适应ADC差分模式的要求。

在数字电路部分,主要由现场可编程门阵列(Field Programmable Gate Array, FPGA)和ADC组成。ADC实时地将模拟信号转换成数字信号,以低电压差分信号(Low-Voltage Differential Signaling, LVDS)模式传向FPGA。在FPGA上,实现了动态的数字化基线的计算,采用了平均值法求基线[7];同时采用了过阈触发的方式,将触发后的有效数据放到缓存器中。在模拟电路第二级接入的DAC的输出也是通过这块FPGA进行控制。

数据采集板与网络传输板的通信是通过mini-dp连接线进行双向传输,实际上是两个FPGA之间的通信,采用了一种同步传输协议的方式,速度为50 Mbit∙s−1。网络传输板主要由FPGA和物理层芯片组成,将数字信号通过网口传输到电脑上,平均传输速度为200 Mbit∙s−1,再对传输到电脑上的数据进行离线处理。

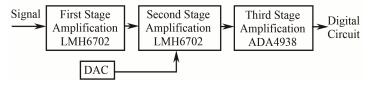

2 低噪声设计 2.1 电子器件选型的设计数字信号利用数字电平来进行信息的传递,由于其幅度大,抗干扰能力强,一般情况下,电路的噪声不会影响数字信号的传递。所以电路噪声主要由模拟电路噪声和ADC噪声组成。如图 3所示,在模拟电路上,第一个和第二个放大器选用了LMH6702,这个放大器有超低失真、宽带、低噪声等特点;第三个放大器选择了低噪声、超低失真度、高速差分放大器ADA4938。

|

图 3 模拟电路三级放大框图 Figure 3 Three magnified of block diagram in analog circuit. |

ADC种类主要有Integral ADC、Σ-ΔADC、SAR (Successive Approximation) ADC、Flash ADC和Pipelined ADC等。本系统目标设计采样率在100MSPS以上,输入信号满量程为2 V时,有效分辨大于11 bit的低噪声电路。通过比较不同种类ADC的转换速率和转换精度,Pipelined ADC是采样率在100 MSPS,具有最高分辨精度的ADC[8]。本系统选取了Pipelined ADC、AD9268作为模数转化器件。此ADC为双通道、16位、125 MSPS,具有高分辨特点。芯片手册上给出芯片接地时噪声均方根值为2.27 LSB(最低有效位,Least Significant Bit)[9],换算成电压为0.069 mV。该芯片是目前商业上可获得100 MSPS、具有最高分辨位数的芯片。

2.2 降低外部噪声的设计外部干扰源主要由供电电源、数字电路的干扰和电磁干扰组成。

对于电源噪声滤波,在模拟电路部分,选择了ADP7142、ADP7183和ADP7156线性稳压器,它们均具有高电源抑制比和低噪声的特性;在数字电路部分,选用了高品质电源滤波模块,有低噪声和功耗低的特点[10]。

电路中模拟部分与数字部分有三部分的交互:ADC输出信号到FPGA;FPGA通过Serial Peripheral Interface (SPI)协议控制ADC内部寄存器;FPGA通过SPI协议控制DAC输出电压。ADC输出信号采用了LVDS模式,降低数字电路对模拟电路的干扰。FPGA控制ADC和DAC时,均在两个芯片交互之间又加了一个电平转化芯片。当FPGA传输指令完毕时,电平转化芯片关闭,使得FPGA和ADC、DAC之间信号线断开,降低数字电路对模拟电路的干扰。

而对于外部的电磁干扰,在电路中设计了一个屏蔽盒,将模拟电路设计在屏蔽盒内,阻挡外部的电磁干扰。

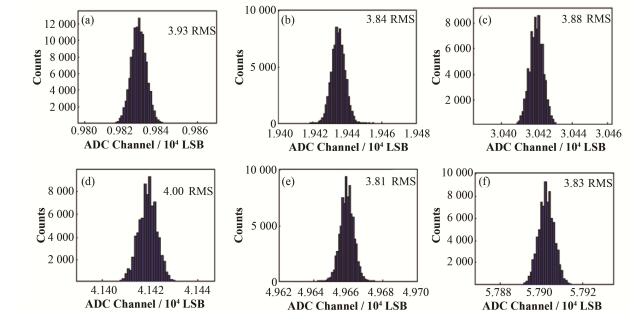

3 性能指标与测试能谱结果 3.1 基线噪声水平测试基线的噪声最直观反映出此电路噪声的抖动,如图 4所示,通过调节DAC的输出,将基线控制在不同的范围。在电路空载的情况下,测试电路自身基线的统计涨落。对6组数据的标准偏差求平均值,得到标准偏差的平均值,为3.92 LSB,换算成电压为2000/65535×3.92 mV,即0.120 mV。

|

图 4 系统基线噪声测试 (a) 9830道,(b) 19430道,(c) 30420道,(d) 41420道,(e) 49660道,(f) 57910道 Figure 4 System baseline noise test. (a) 9830 LSB, (b) 19430 LSB, (c) 30420 LSB, (d) 41420 LSB, (e) 49660 LSB, (f) 57910 LSB |

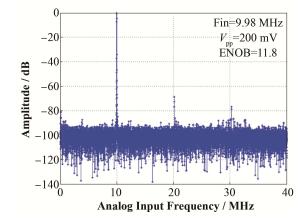

有效位数(Effective number of bits, ENOB)是反映ADC精度的一个指标。有效位数越高,表明ADC电路测量越精确。测试采用ENOB的IEEE Standard 1241-2010[11],为:

| $ E=0.5\log_2 (S)-0.5\log_2 (1.5)-\log_2 (\frac{A}{V}) $ | (1) |

式中:E是ADC的有效位数;V是电路的量程;A是输入正弦波的峰峰值;S是信号对噪声和谐波分量的比值,其计算方法是:

| $ S=\frac{P_\rm{S}}{P_\rm{NAD}} $ | (2) |

式中:PS是傅里叶变换后输入信号频率对应的功率;PNAD是其它频率分量的总和。

测试输入频率在9.98 MHz条件下低噪声电路的有效位数,结果如图 5所示。

|

图 5 有效位数测试 Figure 5 Test of significant digits. |

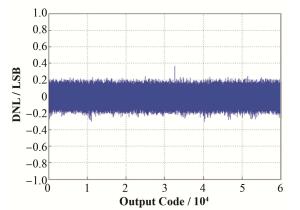

电路的微分非线性表征了ADC道宽的非均匀性,其定义为:ADC每一道道宽的测量值和理想值之差。测试时采用“背对背静态锯齿波测试法”[12],产生周期性的锯齿波,使输入到电路的电压幅度在ADC每道上均匀分布。微分非线性(Differential Nonlinearity, DNL)计算公式为:

| $ D=\frac{h(n)_\rm{actual}}{h(n)_\rm{ideal}}-1 $ | (3) |

式中:D为微分非线性;h(n)actual为实际测得每道的计数;h(n)ideal为理论上每道的计数。测试结果如图 6所示。

|

图 6 DNL统计图 Figure 6 Statistical chart of DNL. |

从图 6可以看出,电路的DNL小于0.4 LSB,表明没有丢失道(DNL绝对值大于1 LSB)。

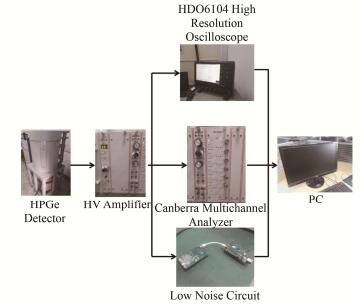

3.4 基于HPGe探测器的系统测试如图 7所示,用高纯锗探测器和这套电子学组成一个系统,测试152EU放射源。做出其能谱,并计算了各个能峰的能量分辨率。HPGe探测器使用的是BE3830型号,高压电源选取的是Model3106D型号,放大器选用的是Model2026型号。同时为了进行对比,在相同条件下测试了HDO6104示波器和Canberra的NIM插件MultiPort Ⅱ采集出的能谱数据。HDO6104示波器采用Teledyne力科的HD4096,具有12-bit高分辨率技术,结合长存储深度、紧凑轻巧的结构设计。HDO6104是市面上可以购买、高速、具有最高分辨的示波器。

|

图 7 HPGe系统测试平台 Figure 7 System test platform of HPGe. |

测试时,先用137Cs、60Co和22Na对这三种仪器进行能量刻度,线性拟合得到ADC道数和能量的关系:

| $ y=kx+b $ | (4) |

能量分辨率计算公式为:

| $ R=\frac{\rm{FWHM}}{E} $ | (5) |

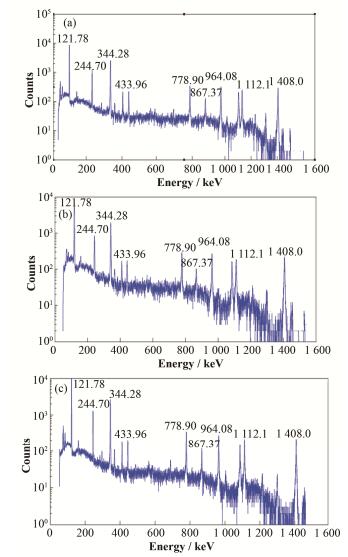

式中:FWHM为峰的半高宽;E为峰的能量。分别用这三种仪器测量152EU,将采集到的脉冲进行存储,用MATLAB对采集到的脉冲进行处理并作能谱图。分别对每个峰进行高斯拟合求出其半高宽FWHM。测试出的能谱图和能量分辨率如图 8所示。

|

图 8 低噪声电路(a)、HDO6104示波器(b)和Canberra多道分析器(c)测试152EU能谱 Figure 8 The spectrum of testing 152EU based on low noise circuit (a), HDO6104 oscilloscope (b) and Canberra multichannel analyzer (c). |

对低噪声电路、HDO6104示波器和Canberra多道分析器测得各个峰位的能量分辨率进行了计算,得到如表 1所示的结果。实验结果表明本电路在各个能区都要优于HDO6104示波器系统。与Canberra多道分析器相比,达到了与其相近的性能指标。

| 表 1 HDO6104示波器、Canberra多道分析器和低噪声电路测试152EU不同峰位的能量分辨率 Table 1 Energy resolution of testing 152EU based on HDO6104 oscilloscope, Canberra multichannel analyzer and low noise circuit. |

本电路从电路设计上减小电子学噪声,选取了低噪声、高分辨的电子器件,并降低了外部的噪声干扰。将电路的噪声减小到很低的水平,噪声水平为0.120 mV,并进行了能谱测量。与高分辨的示波器相比,低噪声波形数字化电路能够得到更好的性能。低噪声波形数字化电路是核信号信息高精度获取的重要硬件基础,该电路还可广泛地应用于数字化高分辨能谱测量、宽量程宇宙射线能谱测量、TOF高精度时间测量以及高空间分辨的辐射成像系统。

| [1] |

Cherenkov E P. The discovery of the Cherenkov radiation[J]. Nuclear Instruments and Methods in Physics Research A, 2008, 595: 8-11. DOI:10.1016/j.nima.2008.07.006 |

| [2] |

Razor CompuScope 16XX-16-bit family of multichannel digitizers for the PCI express and PCI bus[EB/OL]. 2013-4-5[2017-5-20]. http://www.gageapplied.com/digitizers/GaGe-Digitizer-RazorCS16XX-PC I-PCIe-Data-Sheet.pdf.

|

| [3] |

杜中伟. 中子探测的波形数字化技术的研究[D]. 合肥: 中国科学技术大学, 2013. DOI: 10.7666/d.Y2512862. DU Zhongwei. Research of waveform digitizing technology for neutron detection[D]. Hefei:University of Science and Technology of China, 2013. DOI:10.7666/d.Y2512862. |

| [4] |

左广霞. 核辐射信号分析基础[M]. 西安: 西北工业大学出版社, 2015, 133-149. ZUO Guangxia. Fundamentals of nuclear radiation signal analysis[M]. Xi'an: Northwestern Polytechnical University Press, 2015, 133-149. |

| [5] |

王经瑾. 核电子学[M]. 北京: 原子能出版社, 1978, 73-76. WANG Jingjin. Nuclear electronics[M]. Beijing: Atomic Energy Press, 1978, 73-76. |

| [6] |

曾国强, 魏世龙, 夏源, 等. 碲锌镉探测器的数字核信号处理系统设计[J]. 核技术, 2015, 38(11): 110401. ZENG Guoqiang, WEI Shilong, XIA Yuan, et al. Design of digital nuclear signal processing system for CdZnTe detector[J]. Nuclear Techniques, 2015, 38(11): 110401. DOI:10.11889/j.0253-3219.2015.hjs.38.110401 |

| [7] |

李伟男, 杨朝文, 周荣. 基于FPGA脉冲幅度分析器的数字化基线估计方法[J]. 核技术, 2015, 38(6): 060403. LI Weinan, YANG Chaowen, ZHOU Rong. Baseline estimation method of digital multi-channel pulse height analyzer based on FPGA[J]. Nuclear Techniques, 2015, 38(6): 060403. DOI:10.11889/j.0253-3219.2015.hjs.38.060403 |

| [8] |

韩继国. 模/数转换器ADC技术分析(上)[J]. 集成电路应用, 2014(5): 18-22. HAN Jiguo. ADC technical analysis of analog/digital converter (Vol.1)[J]. Integrated Circuit Application, 2014(5): 18-22. |

| [9] |

16-bit, 80 MSPS/105 MSPS/125 MSPS, 1.8 V dual analog-to-digital converter (ADC)[EB/OL]. 2017-3-5[2017-5-20]. http://www.analog.com/media/en/technicaldocumentation/data-sheets/AD9268.pdf.

|

| [10] |

张进文, 周荣, 张京隆, 等. LHAASO-WFCTA数字电路电源模块设计[J]. 核电子学与探测技术, 2015, 35(9): 909-912. ZHANG Jinwen, ZHOU Rong, ZHANG Jinglong, et al. The design of the power module in digital circuit for LHAASO-WFCTA[J]. Nuclear Electronics & Detection Technology, 2015, 35(9): 909-912. |

| [11] |

IEEE standard for terminology and test methods for analog-to-digital converters[C]. IEEE Standard 1241-2010.

|

| [12] |

Testing data converter[EB/OL]. 2017-2-15[2017-5-20]. http://www.analog.com/media/en/training-seminars/design-handbooks/Data-Conversion-Handbook/Chapter5.pdf.

|