2. 中国科学院高能物理研究所 北京 100049;

3. 核探测与核电子学国家重点实验室 北京 100049

2. Institute of High Energy Physics, Chinese Academy of Sciences, Beijing 100049, China;

3. State Key Laboratory of Particle Detection and Electronics, Beijing 100049, China

光电倍增管(Photomultiplier Tube, PMT)是一种具有极高灵敏度和超快时间响应的光探测器件,被广泛应用于物理实验、工业生产、环境监测和医疗器械等领域[1]。作为一种弱光探测器,其性能的好坏直接影响探测结果的可靠性,因此使用之前需要对其进行性能刻度。

光电倍增管的性能参数较多,如收集效率、渡越时间分散、上升时间、下降时间、线性等都是在单光电子谱的基础上进行测试的,因此单光子光源必不可少[2]。目前的性能刻度实验中都用信号发生器输出脉冲信号驱动发光二极管(Light-Emitting Diode, LED)作为光源,当频率较高、占空比较小时认为每次只有一个光子入射到光阴极面产生单光电子[3]。目前常用信号发生器通常只能输出2通道或者4通道脉冲信号,每次最多只能进行两个样管的测试,实际测量时耗较长,不能进行批量测试,所以急需有多路脉冲输出的信号源。目前有很多文献利用可编程门阵列(Field Programmable Gate Array, FPGA)配合高速数模转换器(Digital to analog converter, DAC)和直接数字频率合成器(Direct Digital Frequency Synthesis, DDS)实现信号源[4-8],但是存在设计复杂、扩展性差、成本较高等缺点,不适合多通道并行输出。本文从实际测试需求(多路可调脉冲信号)出发,基于FPGA和以太网设计多通道脉冲信号发生器,最多可达64路通道,能用于光电倍增管批量测试。

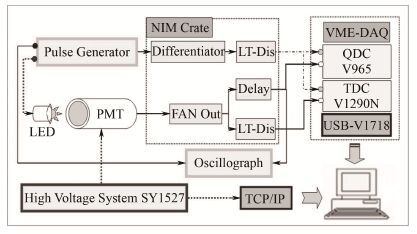

1 PMT性能测试系统简介在PMT校准实验过程中,为了获知PMT的时间性能以及绝对增益(Gain)、能量分辨率(σ)随高压(HV)的变化,以VME测试系统为核心,搭建了PMT性能测试系统,系统原理图[9]如图 1所示。

|

图 1 PMT性能测试系统原理图 Figure 1 Electronic schematic of PMT test system. |

光电倍增管单光电子谱测量过程如图 1所示,脉冲发生器(Pulser)输出频率较高,脉冲宽度较小的脉冲信号驱动发光二极管;取Pulser的同步输出经过微分后,送入低阈甄别器(LT-Dis)得到标准核仪器电平(NuclearInstrument Module, NIM),作为电荷数字转换器(Charge-to-digital Converter, QDC)计数的开门信号;LED发光照亮PMT的光阴极,光阴极逸出电子经倍增极倍增后由阳极输出,QDC (V965) 对其进行计数。

通常情况下,光子入射到光阴极产生的光电子经打拿极倍增后符合泊松分布,其中μ是被第一打拿极收集到的平均光电子数[10]。

| $P\left( n \right) = {\mu ^n}e - \mu /n!$ | (1) |

实验室光电倍增管单光电子测试一般方法是:调节Pulser的输出电压,进而改变LED的强度,使得QDC在约90%的时间里测得的是电子学的台阶(LED不发光,n=0),即单光电子谱中PMT信号所占比例为10%,台阶所占比例为90%,此时出现单光电子的几率约为9.5%,单光电子和多光电子出现的概率比为19:1。从式(1) 可以看出,当光强继续降低,PMT信号所占比例低于10%,单光电子和多光电子出现的概率比增大。

当PMT输出信号为单光子信号时,通过QDC计数得到单光电子谱,利用该电子谱计算其峰谷比、能量分辨率、高压增益性能参数;通过TDC测量渡越时间分散;通过示波器读取信号上升时间和下降时间。

单光子测试需要在微弱光下测试,为保证该条件,需要脉冲信号发生器能输出频率较高、占空比很低的脉冲信号;由于不同的LED发光效率不一致,需要的电压幅值不一样,且LED发光强度和驱动电压不呈线性关系,存在光强从多光子降到单光子时,电压幅值变化量为几毫伏,所以需要输出电压可调,且精度至少达到1 mV;LED驱动脉冲信号的上升时间和下降时间较大会导致PMT信号的上升时间、下降时间、渡越时间分散变大,影响测试精度。

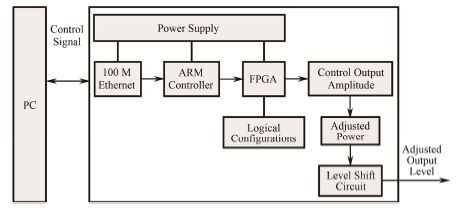

2 脉冲发生器的硬件设计本系统的硬件部分结构如图 2所示。

|

图 2 脉冲发生器原理框图 Figure 2 Functional block diagram of pulse generator. |

ARM (Acorn RISC Machine)控制器通过百兆以太网芯片与PC进行连接,实现PC命令解析及对系统进行相应的控制;FPGA配合可调锁相环控制输出时钟脉冲频率、占空比;输出幅度控制模块进行输出电平调节;电平转换以及信号输出模块实现输出电平转换、输出幅度变换、输出驱动能提升等功能。

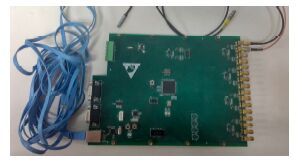

已完成单光子脉冲信号发生器控制板如图 3所示。采用美国Altera公司最新的MAX10 FPGA(型号:10M08SAE144C8G)作为系统的核心,负责脉冲信号的产生以及脉冲信号的控制,该FPGA采用28 nm工艺,具有工作频率高、功耗低等特点。ARM控制器采用意大利ST公司的STM32F107,该芯片以Cortex-M3为核心,最大工作频率为72 MHz,具有非常丰富的外设接口,可以通过MII/GMII物理层接口连接百兆以太网物理层芯片。DP83848为美国TI公司的以太网物理层驱动芯片,支持100 M/ 10 M自适应,通过GMII/MII接口和微控制器(Micro Controller Unit, MCU)进行连接。电平转换芯片作为输出端的控制器,可以在不引起信号畸变的情况下对信号电平进行变化。该电平转换芯片支持的最大数字频率为500 M以上,电平转换芯片的输出端电压由可编程高精度电压源提供。通过电位器和低压差稳压器(Low-Drop-Out, LDO)可以形成一个可编程控制的高精度输出电压源。通过FPGA控制,改变电位器的值可以改变接入反馈电路中的R1和R2的值,最终形成可调电压源,该电压源的输出能力为200 mA,可以驱动两路电平转换芯片。可编程电位器为10位可编程,所以输出电平的分辨率为3.6×102,电阻误差为1%,电阻值为0-20 kW,可以得出输出电压的调节范围为1.2-3.6 V。

|

图 3 单光子脉冲信号发生器实物图 Figure 3 Single-photon pulse generator designed. |

系统的整体工作流程:MCU通过以太网接收到PC端发送的命令之后,接收数据,并进行转发。接收数据包含以下信息:电平幅度、占空比、周期。

在MCU中进行运算,转换成为以下参数,电压源反馈电阻值R1、R2,高电平时间T1,低电平时间T2。其中R1和R2为16 bit数据,T1和T2为4 bytes。所有数据一共为12 bytes,每次发送数据之前,MCU会同步拉低输出管脚(Input/Output, IO),作为写数据帧标识,当IO为低时表示一个数据帧开始,IO为高时表示数据帧结束。FPGA收到数据帧之后,会对数据帧进行解析,分别把R1、R2、T1、T2送入相应的寄存器。同时启动转发部分逻辑,将R1、R2通过串行外设接口(Serial Peripheral Interface, SPI) 1写入可调电位器,将T1、T2写入FPGA内部寄存器。

3 脉冲发生器的软件设计软件程序包含上位机软件、嵌入式程序和FPGA逻辑。

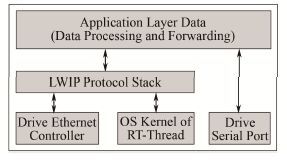

3.1 嵌入式程序设计嵌入式程序主要为ARM控制器STM32F107上的控制部分程序,该部分程序主要实现了TCP/IP协议,通过TCP/IP协议接收上位机发送过来的以太网数据,并在应用层对该数据进行处理转发等。嵌入式程序代码结构如图 4所示。

|

图 4 软件框架图 Figure 4 Software frame diagram. |

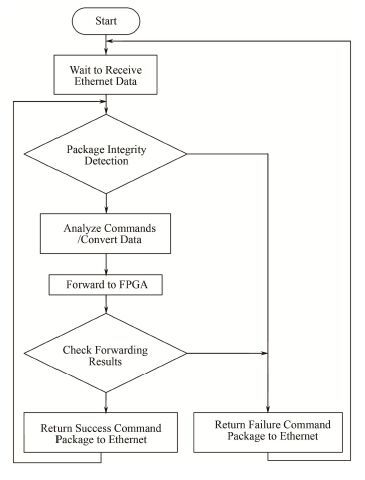

在基于RT-Thread操作系统框架下实现了以太网芯片驱动的移植和应用层程序的编写。对应的MCU程序代码主要数据流程如图 5所示。

|

图 5 软件控制流程图 Figure 5 Flow chart of the embedded control software. |

数据通过以太网输入之后,首先对包的完整性进行检测,再对输入的占空比、电平等数据进行转换,转换成为FPGA里对应寄存器的值。相应的寄存器包括有:1) 高电平时间;2) 低电平时间;3) 可调电阻阻值;4) 通道间延迟。CPU通过通用串行接口写入相应寄存器值,实现对FPGA的控制。

3.2 FPGA逻辑设计FPGA逻辑主要包括数据包接收、数据包分发等。FPGA通过USART收取MCU传过来的数据值,并对其完整性进行校验,而后写入寄存器。其中高电平时间和低电平时间寄存器在FPGA内部经过处理,对FPGA内部锁相环输出时钟相位进行调整,根据不同相位产生的脉冲信号通过与逻辑之后形成输出波形。可调电阻阻值通过SPI接口送至可调电阻中,用来控制低压差稳压器的反馈端电压,进而控制低压差稳压器的输出端电平。通道延时寄存器中的值放入计数器中,用来控制通道之间的延时。这样在FPGA中就完成了对各个通道信号的周期、占空比、通道延时、输出电平的配置。

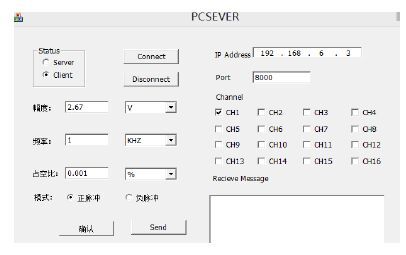

3.3 上位机程序简述上位机软件用C++编写,实现PC和信号发生器的链接、下位机状态查询、通道选通、输出脉冲信号控制。固定信号发生器的IP,将其作为服务器,在同一网段内PC作为客户端。

上位机软件运行截图如图 6所示。

|

图 6 上位机软件用户界面 Figure 6 User interface in PC software. |

对于本系统来说,比较关心的脉冲发生器输出信号参数有:上升时间、下降时间、频率、占空比、输出电平等参数。

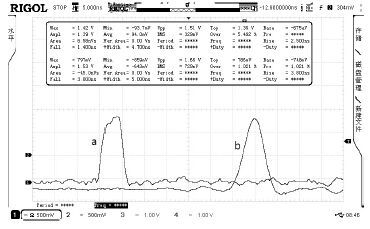

4.1 输出脉冲信号参数测试图 7为利用国产普源RIGOO DS6104示波器(带宽为1GHz,采样率为5 GSPS,配合使用1.5GHz模拟带宽探头)测试本系统输出信号与实验用RIGOO DG5352信号源(最大输出模拟带宽为350MHz,输出采样率为1 GSPS)输出信号波形对比图。图 7中a波形(示波器通道2)为信号源输出波形,b波形(示波器通道1)为该系统输出波形。

|

图 7 输出脉冲性能测试结果 Figure 7 Test results of output pulse performance. |

输出波形特性结果如表 1所示。

| 表 1 测试结果对比 Table 1 Contrast of test results. |

结合图 6和表 1可以看出,本文所述信号源的上升时间、下降时间均优于RIGOO DG5352信号源,更适合PMT单光电子测试,脉冲幅值范围为1.2-3.3 V,满足不同波段LED的发光阈值电压。

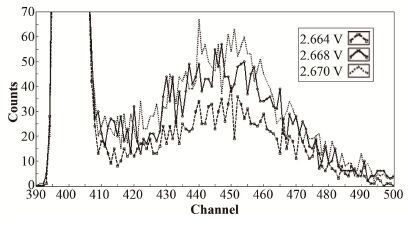

4.2 单光电子测试在中国科学院高能物理研究所光电倍增管性能测试实验室,以20.32 cm R5912为测试样管,在高压不变的情况下(1 560 V),利用本文所示系统输出不同幅值的脉冲信号驱动同一只LED作光源,进行了3次单光电子谱测试,得到单光电子谱图如图 8所示,测试结果都采用1 kHz频率,占空比为0.001%的脉冲信号在幅度为2.664 V、2.668 V、2.670 V情况下进行测试。测试结果中PMT的信号比例分别为3.8%、5.7%、6.6%。

|

图 8 单光子测试对比图 Figure 8 Single photon test diagram. |

从图 8可以看出,当电压幅值在小数点后第三位变化时,信号峰的波峰值和对应道址均有变化,说明该单光子脉冲发生器能精确到1 mV,且在电压值下,PMT均有信号,信号所占的比例均小于10%,即单光子概率与多光子概率远大于20,说明本文设计的信号源都能进行单光电子谱测试。

5 结语本文设计的单光子脉冲信号发生器能同时输出16路脉冲信号,信号频率在0.01-3×108 Hz范围内可调,占空比在100%-0.001%范围内可调,电压幅值精确到1 mV,能满足光电倍增管单光子测试对微弱光的要求,且电压幅值1.2-3.6 V范围内可调,能满足不同波段LED的发光阈值。相比常用商业信号源最多只有4通道左右的脉冲输出,本系统的通道数有了较大的提高,并且输出脉冲的性能比商用信号源(RIGOO DG5352) 更加出色,在能进行单光子测试的条件下更节约成本。另外,本文设计电源系统扩展到64路输出,能满足PMT批量测试需求。

| [1] |

Bruno J G, Richarte A M, Phillips T, et al. Development of a fluorescent enzyme-linked DNA aptamer-magnetic bead sandwich assay and portable fluorometer for sensitive and rapid Leishmania detection in sandflies[J].

Journal of Fluorescence, 2014, 24 (1) : 267 –277.

DOI: 10.1007/s10895-013-1315-6 ( 0) 0)

|

| [2] |

吴金杰, 衡月昆, 刘树彬, 等. BESⅢ飞行时间探测器电子学中的光电倍增管测试[J].

核技术, 2008, 31 (1) : 5 –9.

WU Jinjie, HENG Yuekun, LIU Shubin, et al. Performance test of BESIII TOF electronics by PMT signal[J]. Nuclear Techniques, 2008, 31 (1) : 5 –9. (  0) 0)

|

| [3] |

祁宾祥, 刘树彬, 封常青, 等. 基于USB 接口的多通道准高斯型脉冲信号发生器设计[J].

核电子学与探测技术, 2014, 34 (10) : 1182 –1186.

DOI: 10.3969/j.issn.0258-0934.2014.10.007 QI Binxiang, LIU Shubin, FENG Changqing, et al. Design of a USB-based multi-channel quasi-Gaussian pulse generator[J]. Nuclear Electronics & Detection Technology, 2014, 34 (10) : 1182 –1186. DOI: 10.3969/j.issn.0258-0934.2014.10.007 (  0) 0)

|

| [4] |

刘建梁, 沈三民, 关咏梅, 等. 基于FPGA和AD768的精密程控直流信号源设计[J].

计算机测量与控制, 2015, 23 (3) : 1055 –1057.

DOI: 10.3969/j.issn.1671-4598.2015.03.111 LIU Jianliang, SHEN Sanmin, GUAN Yongmei, et al. Design of precise and programmable DC signal source based on FPGA and AD768[J]. Computer Measurement & Control, 2015, 23 (3) : 1055 –1057. DOI: 10.3969/j.issn.1671-4598.2015.03.111 (  0) 0)

|

| [5] |

王红亮, 黄洋文. 基于FPGA的可程控多路信号源设 计[J].

火力与指挥控制, 2010, 35 (6) : 97 –99.

DOI: 10.3969/j.issn.1002-0640.2010.06.027 WANG Hongliang, HUANG Yangwen. Design of programmable multi-signal generator based on FPGA[J]. Fire Control and Command Control, 2010, 35 (6) : 97 –99. DOI: 10.3969/j.issn.1002-0640.2010.06.027 (  0) 0)

|

| [6] |

Khan S, Manwaring P, Borsic A, et al. FPGA-based voltage and current dual drive system for high frame rate electrical impedance tomography[J].

IEEE Transactions on Medical Imaging, 2015, 34 (4) : 888 –901.

DOI: 10.1109/TMI.2014.2367315 ( 0) 0)

|

| [7] |

Breyer F, Lee S C, Cárdenas D, et al.Real-time gigabit Ethernet transmission over up to 25 m step-index polymer optical fibre using LEDs and FPGA-based signal processing[C].European Conference on Optical Communications, 2009

( 0) 0)

|

| [8] |

Yu Y, Zheng X. Design and implementation of direct digital frequency synthesis sine wave generator based on FPGA[J].

Journal of Electron Devices, 2005, 3 (28) : 596 –599.

DOI: 10.4028/www.scientific.net/AMM.543-547.838 ( 0) 0)

|

| [9] |

宁哲, 钱森, 付在伟, 等. WinXP环境中通用VME系统数据获取研究[J].

核技术, 2010, 33 (10) : 740 –744.

NING Zhe, QIAN Sen, FU Zaiwei, et al. A data acquisition system based on general VME system in WinXP[J]. Nuclear Techniques, 2010, 33 (10) : 740 –744. (  0) 0)

|

| [10] |

付在伟, 钱森, 宁哲, 等. 时间触发系统用PMT性能测试研究[J].

核技术, 2011, 34 (3) : 227 –231.

FU Zaiwei, QIAN Sen, NING Zhe, et al. Performance tests of the PMT for a T0 system of high time resolution[J]. Nuclear Techniques, 2011, 34 (3) : 227 –231. (  0) 0)

|