2. 中国电建集团北京勘测设计研究院有限公司, 北京 100024

3. 北京中科联衡科技有限公司, 北京 100029

2. Power China Beijing Engineering Corporation Limited, Beijing 100024, China

3. Sino-Lionheart Technology Co., Ltd, Beijing 100029, China

随着国民经济的快速发展,对矿产资源的需求日益扩大,矿产资源的短缺已经成为国民经济持续发展的瓶颈,部分矿产的对外依存度已经到了危险的边缘.目前,国内外开发的大部分是1000 m以内非金属矿矿产资源(Zhang et al., 2013),采用非地震勘探方法进行勘探,如:电法、电磁法,在油气和煤炭勘探中发挥着重要作用,其中油气勘探大约占了勘探总量的90%左右.用地震勘探技术探测金属矿有一些成功的案例,但还有很多难题需要克服,主要是金属矿大部分成矿于山区等复杂地表条件,非常不利于野外数据的采集和处理.金属矿地震技术在国内外均处于起步阶段,国际上如加拿大、澳大利亚等国在金属矿勘探中尝试采用石油地震技术,国内中科院、地科院等在金属矿勘探分别尝试石油勘探技术和工程地震技术,但均没有取得良好效果.究其原因,由于金属矿地表地质和地下条件的特殊性,勘探具有勘探深度大、分辨率高(吴增海等,2013;王肃静等,2015)等特点,常规地震勘探技术不适用于金属矿勘探.针对金属矿的特殊地表地质和地下地质条件,必须研制轻便、超多道的高精度地震仪器.

国内外目前还没有专门针对金属矿探测的地震勘探综合系统,大多使用石油和煤炭勘探上使用的仪器,但这些仪器存在体积大、笨重等特点,不适用于复杂山地的地震勘探.相比石油、天然气和煤炭,金属矿的探测经费一般较小,所以研制低成本的高精度地震金属矿勘探仪器系统具有重要意义.

在地震勘探领域,地震勘探系统主要由主控计算机、数据采集站、检波器、电缆、电源等(常宗杰,2012)构成.勘探仪器的采集精度主要由数据采集站(即地震数据采集单元)决定,而地震数据采集的质量,绝大部分取决于数据采集单元模数转换的选取,因此,在地震勘探中,数据采集站的技术指标和稳定性对野外勘探的质量至关重要.目前,随着地震勘探仪器的迅速发展,对地震数据的采集性能也提出了越来越高的要求,为了获得高分辨率的数据信号,也就是要求采集系统的动态范围足够大,这对地震采集系统提出了较高要求.地震数据采集站系统的设计,为整个地震数据探测系统的最终好坏打下了坚实的基础,因此地震数据的采集单元的成功设计是地震勘探的关键技术(王春田等, 2010).

本文提出一种低成本、高精度的地震数据采集系统(郭建和刘光鼎, 2009),该系统集成了可编程放大器、多分辨率的24位Σ-Δ型ADC及数字抽取滤波器的数据采集系统,并与单片机8051同步完成系统的采集;再利用CPLD的核心数字设计对数字进行处理,进而提高数据处理的速度和精度.采用高精度的24位Σ-Δ型ADC进行数据的采集,在分辨率和动态范围上都有了突破,然后采用基于CPLD的数字逻辑设计方式对地震数据进行处理,在硬件方面成功的降低了该采集站电路设计的硬件规模,降低了成本和功耗.因此,该系统具有高精度、低功耗、自检测、低成本的特点,为金属矿勘探提供了许多便利,节约了很多人力物力.

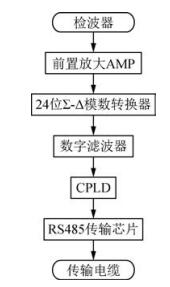

1 数据采集站的系统设计采集站系统用来实现模拟地震信号的采集、数据处理及传输.采集站系统总体构架(易碧金等, 2010)如图 1所示,其中前置放大AMP、24位Σ-Δ模数转换器和数字滤波器作为数据采集部分,CPLD和RS485传输芯片作为数据处理及传输部分.地震数据采集系统(彭卓等, 2013;赵金龙,2016)中采集单元(Data Acquisition Unit, 简称DAU)主要实现数据的采集(王肃静等,2015)、存储和通信功能;主控计算机主要完成地震数据的处理、波形显示以及存储;检波器主要用来传感地震波信号.地震波信息是由采集站进行采集、放大、滤波,然后将数字化的地震信号送入中央记录系统中记录下来.

|

图 1 采集站总体设计流程 Figure 1 The overall design process of Collection station |

系统工作时,主电源站向采集单元发送包含控制命令和同步信息的数据帧包,采集单元将采集到的数据按顺序填充入数据帧包中并向后继续传送,从电源站在接收到数据帧包后,进行数据处理和压缩后继续传送给后面地震数据采集单元或以异步方式转发回主电源站.主控计算机对数据进行译码解码等记录.由于考虑到地震采集站内部空间十分有限,因此在硬件电路结构上采用层叠式设计,地震采集站整体由数据采集电路板和FPGA主控电路板组合组成,它们之间的I/O接口通过2个2.54 mm间距的26脚双排针进行垂直对接.

2 各电路模块设计 2.1 地震检波器地震检波器是一种将地面震动信号转变为电信号的传感器(裴彦良等,2010),是地震数据采集系统的重要组成部分.本文采用的是动圈式检波器.一般情况下,每个检波器自称为一道,每个电源站能够支持检波器数量的多少则为电源站的带道量.电源站带道量越多,即带道能力越强(孙娴和罗桂娥, 2008),说明整个系统功耗越低,电源效率使用越高.

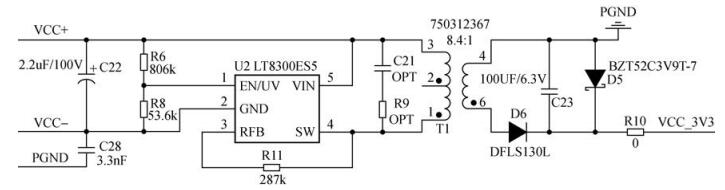

2.2 电源模块电源电路的设计是实现地震采集站低功耗化的关键(刘军等,2009;杨军,2011).采集站的电源电路嵌入到数据采集板和FPGA主控板中,实现了类似于PoE的供电方式,从四芯408UL传输大线上取电(48V电源系统是我国和大部分国家采用的通信电源标准)并进行一系列电压转换,为数据采集电路板和FPGA主控电路板提供稳定的直流电源.根据FPGA主控电路和数据采集电路上各芯片的供电要求,设计了一系列微功耗电压转换电路.48V转3.3V的转换电路图如图 2所示.

|

图 2 48 V转3.3 V隔离电路图 Figure 2 48 V to 3.3 V isolation circuit diagram |

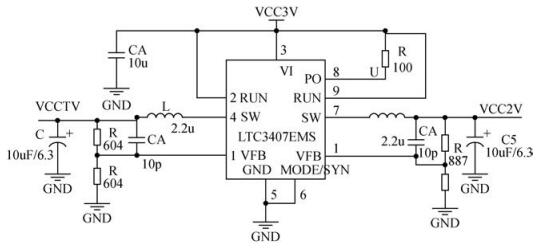

供给FPGA芯片的1.2 V(或1.1 V)内核电压和2.5 V配置电压由LTC3407EMSE芯片产生.如图 3所示.

|

图 3 3.3 V转2.5 V和1.2 V电路图 Figure 3 3.3 V to 2.5 V and 1.2 V circuit diagram |

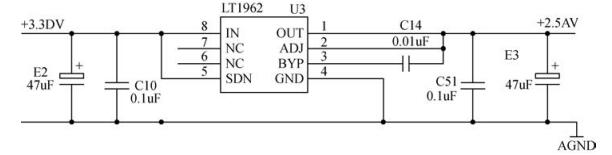

+2.5 VA的模拟电源是由3.3 V电源经过LT1962芯片转换得到.如图 4所示.

|

图 4 3.3 V转+2.5 VA电路图 Figure 4 3.3 V to +2.5 V circuit diagram |

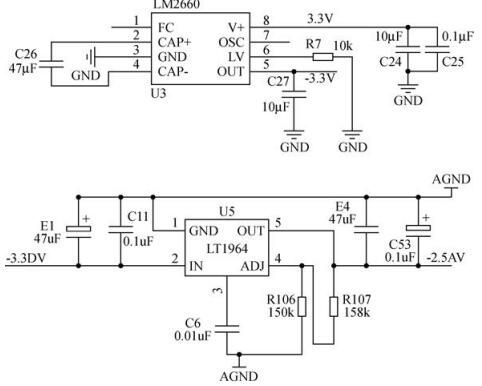

-2.5 VA的模拟电源需经过两次电压变换.首先用LM2660将3.3V的电源转换为-3.3 V输出,接着-3.3 V输入到LT1964转换为-2.5 VA.转换电路图如图 5所示.

|

图 5 3.3 V转-2.5 VA电路图 Figure 5 3.3 V to -2.5 V circuit diagram |

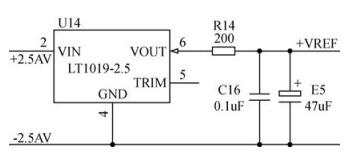

CS5373芯片的2.5 V参考电压由LT1019-2.5芯片产生,其电路原理如图 6所示.

|

图 6 2.5 V参考电压电路图 Figure 6 2.5 V reference voltage circuit diagram |

此外,电路中对于电源地线也进行了分割,分成公共参考地GND、数字电源地DGND和模拟电源地AGND,三者最后通过磁珠连接起来实现单点共地.

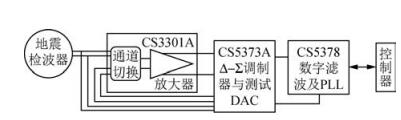

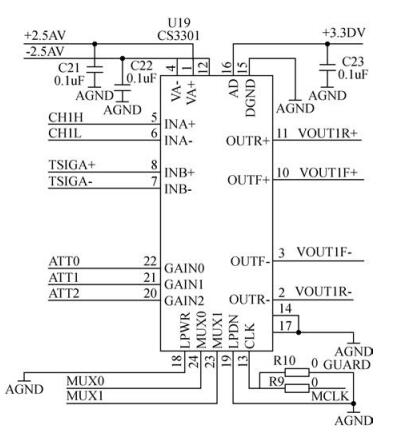

2.3 地震数据采集模块数据采集电路由Cirrus Logic公司研制的CS3301A、CS5373A和CS5378构成(杨军,2011;黄建宇,2014),单通道地震信号采集系统的结构框图如图 7所示.主要功能是接收FPGA主控电路的I/O控制逻辑和采集命令,对检波器响应的电信号进行模数转换,得到的数字信号传送给FPGA主控制器进行运算和处理.

|

图 7 Cirrus单通道地震信号采集系统结构框图 Figure 7 Cirrus structure block diagram of single channel seismic signal acquisition system |

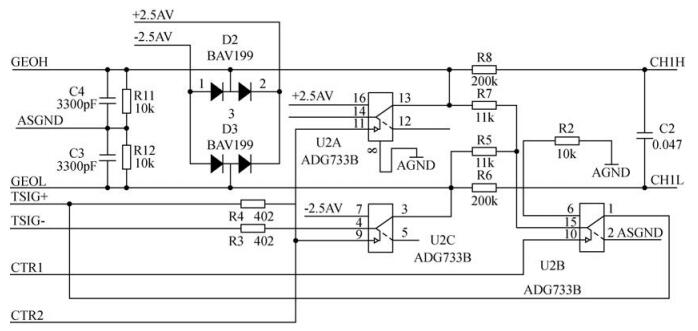

为了达到良好的采集效果,设计了前置滤波电路对模拟信号进行前端处理,为了便于对数据采集电路各项性能指标的测试,设计了实际采集通道与DAC测试通道的激励源切换电路.如图 8所示,共同实现信号的采集和转换,该采集电路具有低功耗、低噪声、高精度并带有自检功能.

|

图 8 前置滤波与通道切换电路原理图 Figure 8 Pre-filtering and channel switching circuit principle diagram |

|

图 9 CS3301A的电路设计 Figure 9 Circuit design of CS3301A |

由于模数转换器处理的信号为无限带宽信号,所以在采样之前需先进行假频滤波(程建远等. 2009;Cirrus Logic, 2004),以滤除高于二分之一采样频率的信号.假频滤波器由共模和差模两级滤波电路组成,共同实现低通滤波功能,如下图 8所示.

通道切换功能是通过一片ADG733模拟电子开关芯片实现,它内置三个独立可选的单刀双掷开关,具有导通电阻小(2.5 Ω·m)、开关速度快、功耗低等特点.

2.3.2 CS3301A差分放大器CS3301A是一款适用于检波器的低噪声、可编程增益的双通道差分放大器.具有1-64的可编程增益配置,采用双极电源供电,模拟供电电压为+2.5 V和-2.5 V,数字供电电压为+3.3 V,电源电路由上文图 3转换获得.它有两个外部差分信号输入,INA是检波器的信号输入,INB是输入CS5373A产生的测试信号,可以通过配置管脚选择具体的输入信号.放大器的增益通过FPGA的ATT0、ATT1、ATT2引脚输出逻辑电平控制.芯片上的LPWR(低功耗模式)引脚接地,PWDN引脚接FPGA输出口,因此控制PWDN引脚的逻辑电平实现芯片在正常模式或断电模式之间切换.CS3301A的差分输出口有两个:OUTR+/-和OUTF+/-,其中OUTR+/-为预放大输出(Rough charge),OUTF+/-为精确放大输出(Fine charge),它们输出的差分信号均传送给CS5373A以进行模数转换.

FPGA可通过MUX0、MUX1引脚控制CS3301输入模式的切换,具体如表 1所示.

|

|

表 1 CS3301输入模式控制 Table 1 The input mode control of CS3301 |

芯片的功耗非常低,芯片的工作电压采用±2.5 V和+3.3 V,正常工作时的工作电流只有5.5 mA,功率约为40 mW(交流)、20 mW(直流),电源中断时能达到10 μA的极小工作电流.

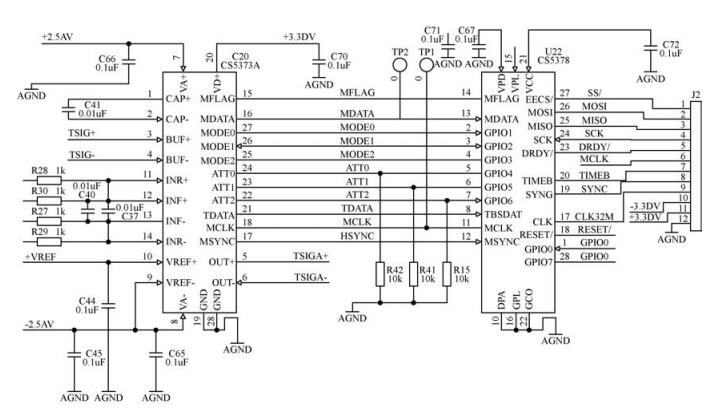

2.3.3 Δ-Σ调制器与数模转换器CS5373ACS5373A是一款高性能、低功耗的芯片,具有24位的Δ-Σ调制器和Δ-Σ数模转换器(DAC)(武东生和张齐,2001;Cirrus Logic Inc,2005).该调制器具有高动态范围、低总谐波失真和超低功耗等特性,它将来自CS3301A放大器的差分模拟信号转换为512kbits/s速率的过采样串行比特流信号,并送给CS5378数字滤波器进行抽取滤波.

CS5373A调制器工作时,接收来自于CS5378的主时钟MCLK和同步信号MSYNC,同时向CS5378返回所产生的一位Δ-Σ转换数据MDATA和信号过幅标志MFLAG.DAC模块产生测试信号的数字位流TDATA来自CS5378的测试位流(TBS)产生器.这样构成了CS5373A内部的自检功能.在交直流两种工作模式下均可工作,交流模式(功耗40 mW)下用来测试系统的动态性能;直流模式(功耗20 mW)下进行脉冲测试和增益校准等,其功耗性能也非常优秀,休眠模式或者中断模式下功耗更低.

2.3.4 数字抽取滤波器CS5378CS5378是进行数字滤波的芯片,可根据需求进行滤波器的配置,还可以任意选择1~4000 sample/s采样率,正常工作时功耗为16 mW.内嵌的PLL产生的标准时钟,同时它内部的自测试DAC可以产生正弦波及脉冲测试信号,用以提供采集系统的自检测信号.采集站的工作电路原理图(李静, 2008),如图 10所示.

|

图 10 CS5373A与CS5378模数转换电路 Figure 10 Analog to digital conversion circuit of CS5373A and CS5378 |

CS5378是一款低功耗、单通道抽取滤波器,内部集成了SINC、FIR和IIR三级滤波器、可配置PLL时钟产生模块、SPI接口控制器、偏置和增益调节器、TBS位流发生器、时间戳控制器和八个GPIO.本设计中为了充分降低功耗,不使用芯片内部PLL时钟源,同时不使用芯片提供的八个GPIO,因此不必供给VDDPAD、VDDPLL电压, 此外,由于CS5378直接使用外部时钟源,因此配置PLL工作方式的电阻R15、R16、R17不需焊接.图 10是CS5373A与CS5378组成的模数转换电路原理图.

CS5378的TBSDA引脚为测试数字位流输出口,MCLK引脚为数字位流输出时钟.FPGA芯片可以通过SPI总线接口进行控制CS5378,接口引脚包括:数据输出准备好信号(DRDY)、串行时钟输入(SCK)、串行数据输出(MISO).

2.4 单片机控制模块本采集站采用美国Cygnl公司推出的C8051F320单片机(司书甲等,2010; 彭卓等,2013)实现电路的控制,C8051F320主要具有如下一些功能特点:满足USB2.0协议;可在全速(12 Mbps)或低速(1.5 Mbps)下运行;集成有一个时钟源,对于全速或低速传输均可不用外部晶振;支持8个灵活通用的USB端点;内置一个1 K的USB专用缓冲存储器;集成了一个USB接收器,不需要外部电阻.其产生的上电复位信号为整个采集电路实现同步、时钟、数据、使能等.主要功能是配合CPLD芯片进行采集数据的处理,在该采集站中是很重要的一部分.

2.5 CPLD芯片介绍及接口模块CPLD(Complex Programmable Logic Device)复杂可编程路基器件(程建远等, 2009; 王东旅等,2011),属于大规模集成电路,具有集成度高,编程灵活,开发周期短等特点.FPGA是在GAL、PAL、CPLD等可编程器件的基础上发展的,两者的区别在于结构上的差异,FPGA是以查找表结构的方式构成逻辑行为的器件,而CPLD是以乘积项结构方式构成逻辑行为的,一般情况下,CPLD的memory较少,适用于小规模集成电路,FPGA的memory较丰富,适用的场合比较广.本文主要综合考虑到该设计需要完成的逻辑功能及所需的管脚量、内存大小等,选择了CPLD位主芯片.CPLD将众多功能的数字设计功能在芯片内实现,从而降低了PCB制板的设计难度,这样对整个系统设计大大降低了成本,简化了硬件电路的设计,缩短设计的周期.

CPLD芯片作为数据处理及传输的核心构件,本文采用Altera公司的EPM570T100C5N芯片最为CPLD芯片(Grout,2009).其价格便宜(约RMB 40元),管脚丰富(可使用近80个),尺寸大小也能够降低PCB板卡设计面积,从而降低成本,并且其内部压控晶体(32.768 MHz)可以提供时钟芯片内部电压为1.8 V,I/O脚的电压为3.3 V,这样既降低了功耗,还提高了系统的性能.

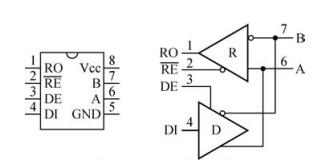

2.6 数据传输模块数据采集站采集的地震数据,先经过CPLD的处理,在芯片内部进行Manchester编码,经过RS485的ADM3485的接口芯片转换为差分信号,再通过电缆传输到下一个采集站.ADM3485的引脚图如图 11所示.

|

图 11 ADM3485的引脚图(R:接收器;D:驱动器) Figure 11 Pin figure ofADM3485 (R: RECEIVER; D: DRIVER) |

图 12为主控板实物图,图 13为Cirrus套片数据采集电路板实物图,图 14为单个采集站连接实物图.

|

图 12 主控板实物图 Figure 12 The picture of real products of main control board |

|

图 13 Cirrus套片数据采集电路板实物图 Figure 13 The picture of Cirrus data acquisition circuit board |

|

图 14 单个采集站连接实物图 Figure 14 The picture of data acquisition unit |

1) A/D转换精度:24位;

2) A/D转换动态范围:≥120 dB;

3) 采集站间传输距离:25 m;

4) 信号带宽:DC到2 kHz;

5) 可选择增益:×1, ×2, ×4, ×8, ×16, ×32, ×64;

6) 采样率:0.25 ms, 0.5 ms, 1.0 ms, 2.0 ms;

7) 频率响应:0~1600 Hz;

8) 总谐波畸变:0.0005%.

4 采集站性能测试 4.1 测试平台介绍采集站性能测试平台由直流电源、待测地震采集站和安装有测试软件(Quartus Ⅱ及Matlab)的PC机等组成.测试流程如下:首先,用48V直流电源给地震采集站供电;其次,通过USB-Blaster下载器从Quartus Ⅱ软件下载sof文件到FPGA主控板,将地震采集站配置成测试状态;接着,打开SignalTap Ⅱ Logic Analyzer软件,启动观察时序波形并提取测试数据,导出为CSV格式的文件;最后,通过Matlab软件程序编写数据处理和分析代码,获得最终测试结果.

采集站性能测试主要包括等内部电路测试、等效输入噪声测试、谐波畸变测试,动态范围测试、功耗测试等.

4.2 内部电路测试 4.2.1 电气特性测试首先,先对采集系统的电气特性进行测试,确保采集站的内部电路的正确性,然后再进行多道采集站之间的连接.站与站之间通过25 m四芯电缆线连接,作为数据和电压的传输通道.

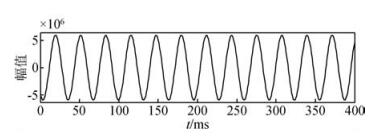

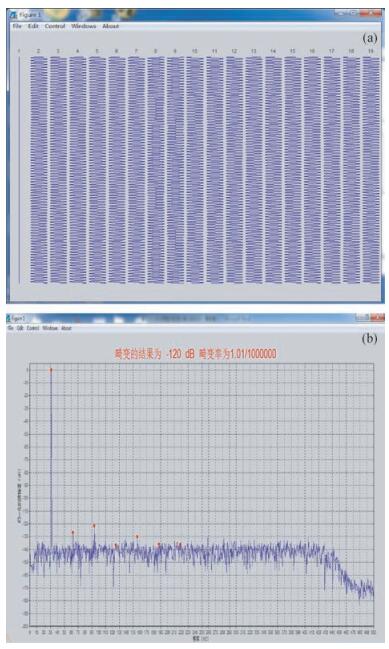

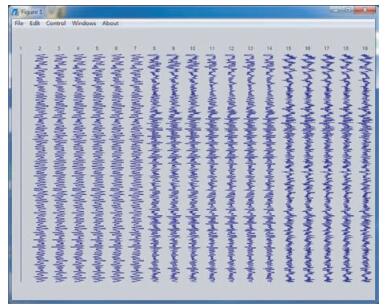

系统采用1 ms采样,对2048个采样点进行测试,从采集数据中读取一道信号的部分数据,如图 15所示,从波形来看,是较为正规的正弦波信号.

|

图 15 单道信号的正弦波波形 Figure 15 The sine waveform of single channel |

对系统进行自检,在确保采集站的内部电路的正确性之后,然后再进行多道采集站之间的连接.站与站之间通过25 m四芯电缆线连接,作为数据和电压的传输通道.其中,为了方便分析测试结果,将第一道设为固定数值,其他道则为正弦波信号,检测结果以及其对应的指标分析如图 16所示.

|

图 16 系统自检测 (a)19道采集站正弦波数据; (b)数据归一化指标分析. Figure 16 System testing (a)Sine wave data of 19 acquisition stations; (b)Data normalization index analysis. |

从图 16b中可以看出,采集到的正弦波的主频信号为31.25 Hz,及相对应的几个倍频频率值.同时,在主频的2倍和3倍频率上虽然有明显的倍频幅值,但是幅值不是很大,即采集站在对正弦波采样过程中没有明显的畸变,达到初期设计的目标.

4.2.3 系统对外测试外部环境测试中,地震检波器插在泡沫板上,并确保与各采集站连接无误,将采集电路的模式从自检模式改为地震波采集数据,其中,第一道仍然设为仍为固定数值,其他道则为地震检波器数据,采集到的检波器信号如图 17所示.

|

图 17 多道采集站对外测试 Figure 17 External testing of multi-channel collection station |

其中,第2-7、8-14、15-19个采集站分别连接同一个检波器.通过对对测试结果的分析,初步验证了系统设计的正确性.

4.3 等效输入噪声测试等效输入噪声测试需在模拟信号输入端接一个400 Ω终端电阻,采样率为1000SPS,采样时间为2 s,分别采集前放增益为×1、×4、×8、×16、×64时的转换数据进行处理和分析,计算时采用多次测量取平均值的方法.

通道噪声测试计算方法如下:首先,按照公式(1) 取N个采样点幅度Xi的平均值,得到噪声信号的直流漂移dc,公式为

|

(1) |

接着,根据公式(2) 计算模拟信号的总有效值RMS,公式为

|

(2) |

最后,根据公式(3) 计算去掉漂移的模拟信号的总有效值AC,公式为

|

(3) |

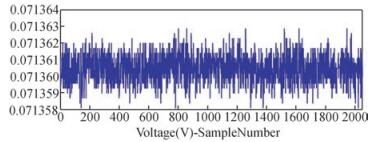

通过对2048个输入噪声采样点数据(前放增益为×1) 进行处理,绘制出图 18所示的输入噪声波形曲线图.

|

图 18 Cirrus采集板输入噪声曲线 Figure 18 Cirrus acquisition board input noise curve |

Cirrus采集板的等效输入噪声测试结果如表 2所示.通常,等效输入噪声越小,A/D转换器的信噪比就越大,动态范围也越大.通过与SY/T 5391—2007标准作比较,Cirrus采集板的等效输入噪声均优于A级标准,满足地震数据采集的要求,达到预期设定的目标.

|

|

表 2 等效输入噪声测试结果及对比表 Table 2 The test results and comparison table of the equivalent input noise |

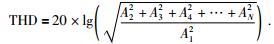

测试时,配置DAC输出频率为31.25 Hz的满幅度正弦波信号,前放增益×1,A/D转换器采样率为1000SPS,采样时间为2 s.转换数据以CSV格式文件导出,由Matlab软件进行数据处理和分析.

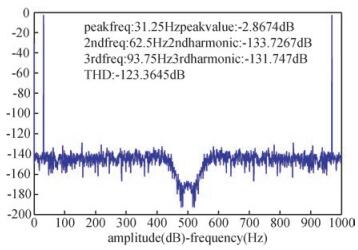

谐波畸变(SEG,1988)结果THD可按公式(4) 计算得到,其中Ai(i≥2) 为高次谐波分量幅度,A1为基波分量幅度.公式(4) 为

|

(4) |

Matlab程序首先对2048个采样点进行FFT变换并取模,得到采样点的频域幅值,对每个采样点的幅值取对数并乘以20,绘出图 19所示Cirrus套片采集板的幅频曲线图.从所有采样点中取最大频域幅值,该值即为基波的幅值,对应的频率点就是基波频率,在该基波频率正整数倍的频率点处取幅值,依次得到各高次谐波分量的幅值,程序只计算到六次谐波分量,通过公式4计算得到Cirrus套片采集板谐波畸变值为-123.3 dB,达到SY/T 5391—2007中的A级标准(小于-106 dB),满足地震数据采集的要求.

|

图 19 Cirrus套片采集板幅频曲线图 Figure 19 Cirrus acquisition board amplitude frequency curve |

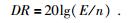

动态范围(SEG,1988)可按照公式(5) 计算得到.其中,E为通道最大输出信号的RMS值,n为通道无驱动信号的噪声RMS值,按照分贝计算最大输出信号与噪声比值得到通道的动态范围DR.E和n的计算方法相同,可参照公式(1)~(3) 计算得到.公式(5) 为

|

(5) |

测试时,配置A/D转换器的采样率为1000SPS,前放增益×1,采样时间2 s.配置测试DAC首先产生最大可接受输出电平的正弦波信号,即满幅正弦波信号,并输出给A/D转换器进行转换,获取通道最大输出信号的模数转换值,通过Matlab软件将2048个采样点数据减去其直流偏量,并计算其RMS值,即可得到E.接着,禁用测试DAC,切换到等效输入噪声测试模式,获取通道无驱动信号时的模数转换值,同样通过Matlab软件将2048个采样点数据减去其直流偏量,并计算其RMS值得到n.最后按照公式5计算得到Cirrus采集板的动态范围为126.9 dB,达到SY/T 5391—2007中的A级标准.

|

|

表 3 动态范围测试结果 Table 3 Dynamic range test results |

分布式地震采集站低功耗化是设计的主要目标之一,为了获得分布式地震采集站的功耗特性,对采集站的进行功耗测试,如表 4所示.

|

|

表 4 采集板与主控板单板和整体功耗测试结果 Table 4 Test results of single board and overall power consumption of acquisition board and main control board |

同时,在野外也进行了测试实验,系统工作正常,对震源的振幅明显,并且其采样精度、动态范围等各项指标都达到或接近世界上同类先进地震勘探仪器的标准.

5 结论本文以金属矿地震勘探为背景,提出了一种低成本、高精度的地震勘探数据采集站的系统设计.采用Cirrus Logic公司24位高精度的Σ-Δ型芯片作为采集站的核心,提高了采集数据的分辨率和动态范围;基于CPLD的数字逻辑设计方式,降低了电路设计的硬件规模并通过实验验证其正确性,通过软件设计对噪声、增益、采样率等一系列参数进行了测试,从采集测试结果可以看出,Cirrus采集板在等效输入噪声、谐波畸变,动态范围等方面性能优异,均达到了SY/T 5391—2007中的A级标准及本文所设定的技术指标;系统中电源模块的低功耗设计及CPLD芯片较少的IC设计,其功耗较低,不仅降低了蓄电池的使用数量,而且降低人力、物力和财力,对野外工作也有极大好处,此外,从采集站传输测试结果可以看出,采集站与电源站之间数据传输正常、电路工作稳定,各个采集站采集到的数据完整、同步,达到了设计的要求.

致谢 感谢中国科学院地质与地球物理研究所郭建研究员在课题研究和论文撰写过程中给予的建议与帮助.此外,还要感谢审稿专家和编辑部老师的支持和帮助.| [] | Chang Z J. 2012. Technology and realization on multiple sensors data acquisition and transmission controlling for marine seismic streamer system (in Chinese)[Master's thesis]. Tianjin:Tianjin University. |

| [] | Cheng J Y, Wang S Q, Song G L. 2009. The new development and foreground expectation of seismic exploration[J]. Coal Geology & Exploration, 37(2): 55–58. |

| [] | Cirrus Logic. 2004. Low-power, multi-channel decimation filter[DB/OL]. Cirrus Logic, Inc. |

| [] | Cirrus Logic Inc. 2005. CS5373 Low-power, high-performance modulator and test DAC[EB/OL]. |

| [] | Grout Ⅰ. 2009. Design system design with FPGAs and CPLDs (in Chinese)[M]. Huang Y H Trans. Beijing:Publishing House of Electronics Industry. |

| [] | Guo J, Liu G D. 2009. Current situation and expectation of cable-less seismic acquisition system[J]. Progress in Geophysics, 24(5): 1540–1549. DOI:10.3969/j.issn.1004-2903.2009.05.001 |

| [] | Huang J Y. 2014. Development of high-precision low-power distributed seismic acquisition station (in Chinese)[Master's thesis]. Beijing:China University of Geosciences (Beijing). |

| [] | Li J. 2008. The high-precision data acquisition system of geophysical prospecting equipment——the MWD data acquisition system of directional drilling (in Chinese)[Master's thesis]. Wuhan:China University of Geosciences (Wuhan). |

| [] | Liu J, Zhou D H, Zhou Y N. 2009. A deepwater long-term observation data acquisition device with low power consumption[J]. Microcomputer Information, 25(4-1): 81–83. |

| [] | Pei Y L, Zhao Y X, Liu B H, et al. 2010. Research on the offshore high-resolution multi-channel seismic streamer and its application to the ocean engineering[J]. Progress in Geophysics, 25(1): 331–336. DOI:10.3969/j.issn.1004-2903.2010.01.044 |

| [] | Peng Z, Deng Y, Ma C, et al. 2013. Improvement and implementation of FPGA based seismic data acquisition unit[J]. Computer Measurement & Control, 21(1): 282–284. |

| [] | Si S J, Bi Y G, Fu Z B. 2010. Optimized strategy for the RSU'S control based on MCU[J]. Control & Automation, 26(5-2): 34–36. |

| [] | Society of Exploration Geophysicists (SEG). 1988. Digital Seismic Recorder Specification Standards, 1988. Subcommittee of the technical standards committee on digital seismic recorder specifications[S]. |

| [] | Sun X, Luo G E. 2008. Design and implementation of a high precision seismic data acquisition system[J]. Computer Measurement & Control, 16(6): 881–883. |

| [] | Wang C T, Yan Z W, Zhao Z. 2010. Features and prospects of the cableless seismic acquisition system[J]. Petroleum Instruments, 24(5): 1–3. |

| [] | Wang D L, Yang Y F, Cheng H C, et al. 2011. Data transmission system design in marine seismic data acquisition system[J]. Journal of Data Acquisition & Processing, 26(4): 494–498. |

| [] | Wang S J, Lu C, You Q Y, et al. 2015. Design of a low cost Non-cable seismic acquisition station[J]. Chinese J. Geophys., 58(4): 1425–1433. DOI:10.6038/cjg20150428 |

| [] | Wu D S, Zhang Q. 2001. Main point in designing data collector of automatic monitoring ocean station[J]. Ocean Technology, 20(1): 59–61. |

| [] | Wu Z H, Song K Z, Cao P. 2013. Design and realization of digitizer for marine seismic exploration[J]. Journal of Data Acquisition & Processing, 28(2): 250–256. |

| [] | Yang J. 2011. The design of seismic data acquisition unit system based on CPLD (in Chinese)[Master's thesis]. Chengdu:Chengdu University of Technology. |

| [] | Yi B J, Jiang G, Gao H. 2010. Development and reflection on seismic data acquisition system[J]. Oil Forum, 29(2): 29–34. |

| [] | Zhang Q S, Deng M, Guo J, et al. 2013. Development of a new seismic-data acquisition station based on system-on-a-programmable-chip technology[J]. Annals of Geophysics, 56(3): 1861–1867. |

| [] | Zhao J L. 2016. Design and implementation of single-channel storage type wireless seismograph based on STM32 (in Chinese)[Master's thesis]. Changchun:Jilin University. |

| [] | 常宗杰. 2012. 海洋勘探拖缆多传感器数据采集传输控制技术及实现[硕士论文]. 天津: 天津大学. http://cdmd.cnki.com.cn/Article/CDMD-10056-1013039908.htm |

| [] | 程建远, 王寿全, 宋国龙. 2009. 地震勘探技术的新进展与前景展望[J]. 煤田地质与勘探, 37(2): 55–58. |

| [] | Grout Ⅰ. 2009. 基于FPGA和CPLD的数字系统设计[M]. 黄以华译. 北京: 电子工业出版社. |

| [] | 郭建, 刘光鼎. 2009. 无缆存储式数字地震仪的现状及展望[J]. 地球物理学进展, 24(5): 1540–1549. DOI:10.3969/j.issn.1004-2903.2009.05.001 |

| [] | 黄建宇. 2014. 高精度低功耗分布式地震采集站的研制[硕士论文]. 北京: 中国地质大学(北京). http://cdmd.cnki.com.cn/Article/CDMD-11415-1014238110.htm |

| [] | 李静. 2008. 地球物理勘探设备的高精度数据采集系统——定向钻进轨迹测量数据采集系统[硕士论文]. 武汉: 中国地质大学(武汉). http://d.wanfangdata.com.cn/Thesis/Y1279097 |

| [] | 刘军, 周东辉, 周亚楠. 2009. 一种深海长期观测低功耗数据采集装置[J]. 微计算机信息, 25(4-1): 81–83. |

| [] | 裴彦良, 赵月霞, 刘保华, 等. 2010. 近海高分辨率多道地震拖缆系统及其在海洋工程中的应用[J]. 地球物理学进展, 25(1): 331–336. DOI:10.3969/j.issn.1004-2903.2010.01.044 |

| [] | 彭卓, 邓焱, 马骋, 等. 2013. 基于FPGA的地震数据采集单元改进与实现[J]. 计算机测量与控制, 21(1): 282–284. |

| [] | 司书甲, 毕研刚, 傅志斌. 2010. 基于单片机的地震仪器采集站控制优化[J]. 微计算机信息, 26(5-2): 34–36. |

| [] | 孙娴, 罗桂娥. 2008. 一种高精度地震勘探数据采集系统的设计与实现[J]. 计算机测量与控制, 16(6): 881–883. |

| [] | 王春田, 闫志武, 赵忠. 2010. 新型无缆采集系统功能特点及发展前景[J]. 石油仪器, 24(5): 1–3. |

| [] | 王东旅, 杨俊峰, 程宏才, 等. 2011. 地震数据采集系统中的数据传输系统设计[J]. 数据采集与处理, 26(4): 494–498. |

| [] | 王肃静, 卢川, 游庆瑜, 等. 2015. 一种低成本无缆地震仪采集站的研制[J]. 地球物理学报, 58(4): 1425–1433. DOI:10.6038/cjg20150428 |

| [] | 武东生, 张齐. 2001. 海洋站数据采集器的设计要点[J]. 海洋技术, 20(1): 59–61. |

| [] | 吴增海, 宋克柱, 曹平. 2013. 用于海洋地震勘探的数字包设计与实现[J]. 数据采集与处理, 28(2): 250–256. |

| [] | 杨军. 2011. 基于CPLD的地震勘探数据采集站系统设计[硕士论文]. 成都: 成都理工大学. http://cdmd.cnki.com.cn/Article/CDMD-10616-1011235970.htm |

| [] | 易碧金, 姜耕, 高华. 2010. 地震数据采集记录系统的发展与思考[J]. 石油科技论坛, 29(2): 29–34. |

| [] | 赵金龙. 2016. 基于STM32的单通道无缆存储式地震仪设计与实现[硕士论文]. 长春: 吉林大学. http://cdmd.cnki.com.cn/Article/CDMD-10183-1016079607.htm |

2017, Vol. 32

2017, Vol. 32