2. 广东工业大学 集成电路学院, 广东 广州 510006

2. School of Integrated Circuits, Guangdong University of Technology, Guangzhou 510006, China

随着高数据速率无线通信系统和高分辨率雷达需求的快速增长,毫米波收发器引起了工业界和学术界的广泛关注[1]。此外,第五代移动通信技术(5G) 因其高速率、大容量和低延迟的特性而备受瞩目[2]。在此背景下,毫米波通信作为5G技术的重要组成部分,为更高的数据传输速度和更大的网络容量提供了关键支持。在接收机中,低噪声放大器(Low Noise Amplifier, LNA) 作为第一个有源模块,在无线系统性能方面发挥着至关重要的作用。

在5G毫米波通信接收系统中,低噪声放大器扮演着至关重要的角色。低噪声放大器在无线电接收机性能中起着关键作用。接收机设计的成功体现在多个方面,例如接收机的灵敏度、噪声、增益等等[3]。低噪声放大器作为接收机的前端器件,其主要作用是在噪声尽可能小的情况下对接收机所接收到的小信号进行足够高的增益放大。因此,对于低噪声放大器而言,噪声及增益是首要考虑的两大关键指标。此外,由于在信号失真的情形下,接收机将不能正常接收有用信号,因此,作为整个接收机的核心模块,低噪声放大器需要具有较高的线性度以避免非线性影响导致信号失真。并且,本文中的低噪声放大器应用在毫米波频段,由于毫米波信号的频率较高,其受到噪声的影响更为显著,因此设计出一款能够应用在毫米波频段的低噪声放大器十分关键。

近年来,硅基的毫米波低噪声放大器得到了广泛的研究。受硅基工艺发展的影响,硅基器件的集成度得到提高,制造含有硅基工艺的高频集成电路器件所需生产成本大大降低,硅基工艺的研究越来越受到重视,因此,在许多方面都有很大的应用前景。与其他I至V半导体工艺相比,硅基工艺由于其低成本的优势,在无线电通信应用中具有广泛的应用范围[4]。随着基于硅的工艺的不断进步,低噪声放大器无论是采用SiGe工艺还是CMOS工艺,其晶体管的能力都发生了显著变化,从最初的低噪声无法满足毫米波频段的设计要求,到现在它们有能力覆盖5G的所有频段,甚至所能够满足设计的频段还在不断拓展。其低制造成本、易于集成、小面积、良好的工艺兼容性和其他优点,极大地促进了单片集成尤其是低噪声放大器的应用及发展。目前,硅基毫米波的超宽带低噪声放大器在芯片市场占据主导地位,因此,在5G时代,硅基毫米波超宽带低噪音放大器具有重要的学术研究价值和商业应用潜力[5]。

不仅基于硅基的工艺改进为毫米波低噪声放大器设计奠定了制造基础,一些基于电路结构设计而被众多国内外学者所提出的技术也在不断地将低噪声放大器的性能发挥到极致。为了改善毫米波LNA的性能,几种常见的技术已经被国内外众多学者提出:包括用于共源(Common Source, CS) 放大器的源极电感负反馈技术[6-7]、采用共栅(Common Gate, CG) 放大器的跨导增强技术[8-9],以及基于变压器的降噪技术[10]。

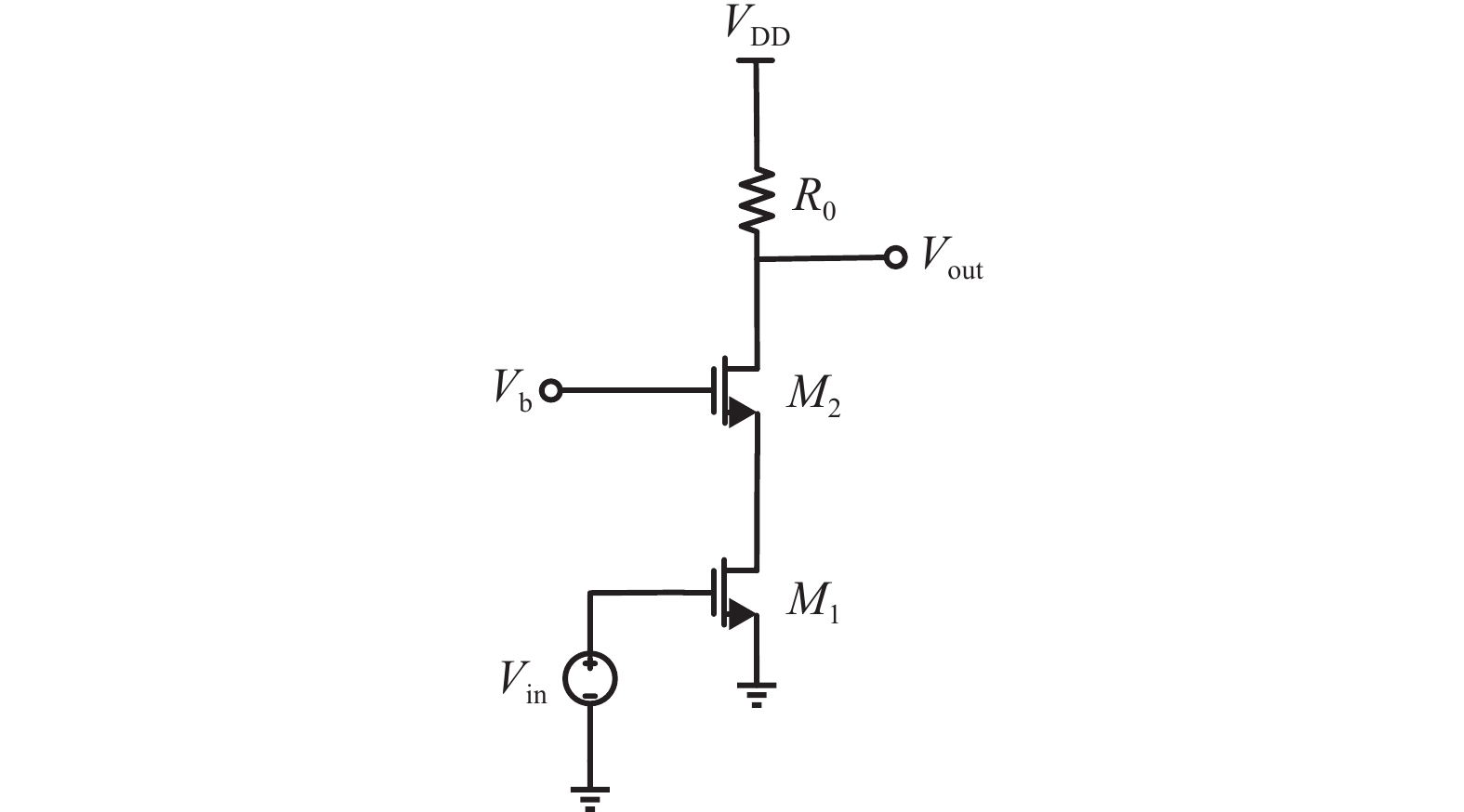

1 理论解析 1.1 改进型共源共栅低噪放共源共栅结构(Cascode) 是一种由共源级和共栅级堆叠而成的电路结构,它常被用于低噪声放大器的设计中[11],如图1所示。该结构具有以下几个优点:首先,它能够提供良好的反向隔离度,降低输入输出端口之间的相互影响。这意味着在进行输入输出匹配网络设计时,不需要考虑与其他部分的干扰。其次,共源共栅结构还能够提供较好的电路稳定性,进一步增强了整个系统的可靠性。

|

图 1 共源共栅结构 Figure 1 Cascode |

在常见的低噪声放大器设计中,为了有效隔离射频信号对偏置电路的影响,通常会在偏置电路中引入去耦电容[12],该去耦电容会被纳入匹配网络中,其主要作用是防止射频信号流入偏置电路,并提供射频等效的效果。

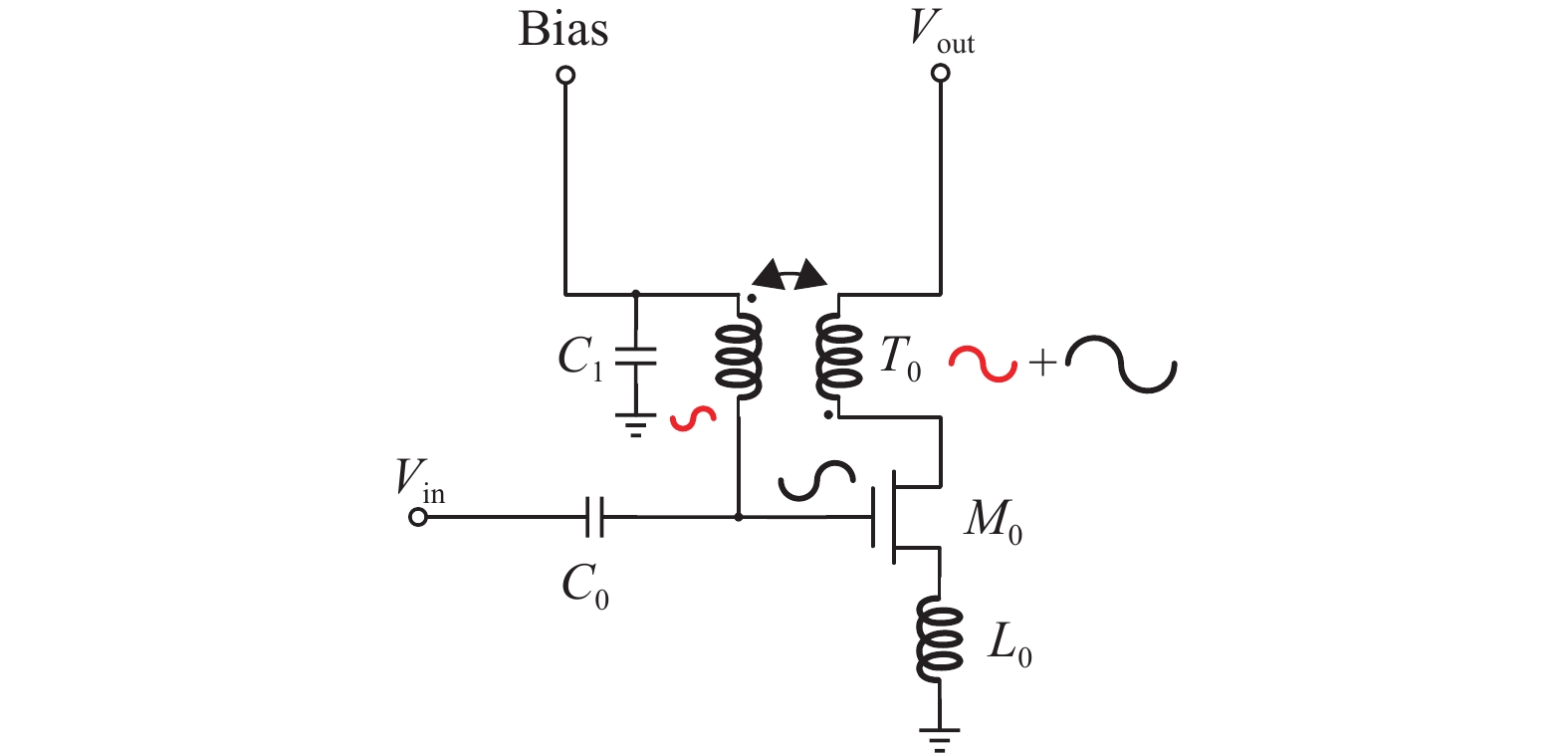

本文的设计巧妙利用了可能影响偏置电路的射频信号。通过同相变压器的放大特性,将这些信号同相放大至第一级共源共栅级的信号传输处,从而实现信号的再次放大,如图2所示。

|

图 2 同相放大原理 Figure 2 Principle of in-phase amplification |

不同于以往让这部分信号直接流入射频端,造成部分射频信号的损失,该改进型的共源共栅级能够很好地利用了这部分损耗的信号,让其被放大并继续进行传输,实现信号的正反馈输入。即本文的创新之处主要在于,如本文中的图2所阐述的原理,在输入端引入了变压器,不仅能够极大地拓宽低噪声放大器输入回波损耗的应用频带范围,还能够对其进行同相放大,将射频信号通过输入端分别流入放大链路和射频端进行信号叠加,类似于同相放大的原理,因此能够对低噪声放大器在增益方面有所提升。而已有的研究工作并没有如此使用过变压来进行信号叠加及放大,并且大多数文献也只是使用了变压器来进行芯片面积的节省或是采用引入变压器做输入输出端的匹配,并未在增益提升方面有所考量。通过该手段改进后的共源共栅结构如图3所示。

|

图 3 改进型共源共栅结构 Figure 3 Improved cascode |

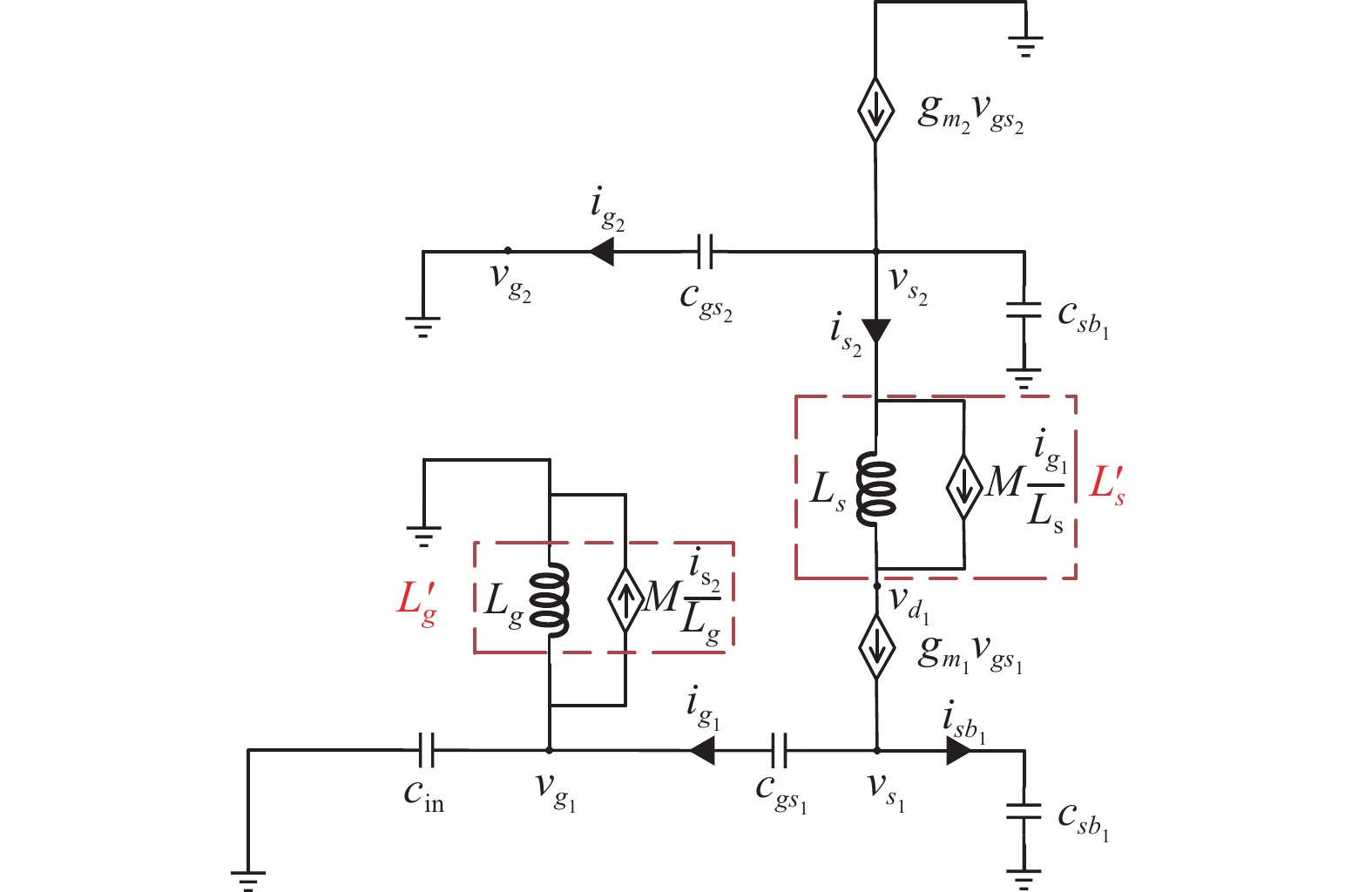

为了更直观地了解采用该方法进行改进后的性能参数与改进前的对比,下文将对该结构进行小信号分析,并进行相应的增益分析,图4为改进型共源共栅结构小信号等效电路。

|

图 4 改进型共源共栅结构小信号等效电路 Figure 4 Improved cascode small signal equivalent circuit |

对于M1、M2晶体管,参照文献[13]所提出的计算方法,类似的将小信号等效电路画出,并根据基尔霍夫电流定律(Kirchhoff's Current Law, KCL),写出如下公式:

| $i_{{g}_{1}}=\frac{{v}_{{g}_{1}}}{s{L}_{g}}+\frac{M\cdot {i}_{{s}_{2}}}{{L}_{g}}+{{v}_{{g}_{1}}}\bigg/\left({\dfrac{1}{s{c}_{{\mathrm{in}}}}}\right) $ | (1) |

| $ {i}_{{g}_{1}}=\frac{{v}_{{s}_{1}}-{v}_{{g}_{1}}}{\dfrac{1}{s{c}_{{gs}_{1}}}} $ | (2) |

| ${i}_{{g}_{1}}+{i}_{{sb}_{1}}={i}_{{s}_{2}}$ | (3) |

| $ {i}_{{sb}_{1}}={{v}_{{s}_{1}}}\bigg/\left({\frac{1}{s{c}_{{sb}_{1}}}}\right) $ | (4) |

| ${i}_{{s}_{2}}=\frac{{v}_{{s}_{2}}-{v}_{{d}_{1}}}{s{L}_{s}}+\frac{M\cdot {i}_{{g}_{1}}}{{L}_{s}}+{g}_{{m}_{1}}{v}_{{gs}_{1}} $ | (5) |

式中:b为共栅极的栅级电压,d为共栅极的漏端电感。另有,互感M为

| $M=k\sqrt{{L}_{g}{L}_{s}} $ | (6) |

以及:

| $s={\mathrm{j}}\omega $ | (7) |

根据式(1)~(7),可解得变压器等效电感

| ${L}'_{g}=\frac{{v}_{{g}_{1}}}{s{i}_{{g}_{1}}}=\frac{{L}_{g}-k\sqrt{{L}_{g}{L}_{s}}\left(1+\dfrac{{c}_{{sb}_{1}}}{{c}_{{gs}_{1}}}\right) }{{1-(\omega }^{2}k\sqrt{{L}_{g}{L}_{s}}{c}_{{sb}_{1}}+{\omega }^{2}{L}_{g}{c}_{\mathrm{in}}) } $ | (8) |

| ${L}'_{s}=\frac{{V}_{{s}_{2}}-{V}_{{d}_{1}}}{s{i}_{{s}_{2}}}{=L}_{s}-\frac{k\sqrt{{L}_{g}{L}_{s}}\left(k\sqrt{{L}_{g}{L}_{s}}-\dfrac{{L}_{s}{g}_{{m}_{1}}}{{\mathrm{j}}\omega {c}_{{gs}_{1}}}\right) }{{L}_{g}\left(1-\dfrac{{L}'_{g}}{{L}_{g}}+{\omega }^{2}{L}'_{g}{c}_{{\mathrm{in}}}\right) } $ | (9) |

通过式(8)~(9)可知,经过调整两电感叠加耦合形成的变压器中的耦合系数k以及构成变压器的初级线圈和次级线圈电感值

根据计算得出的等效电感

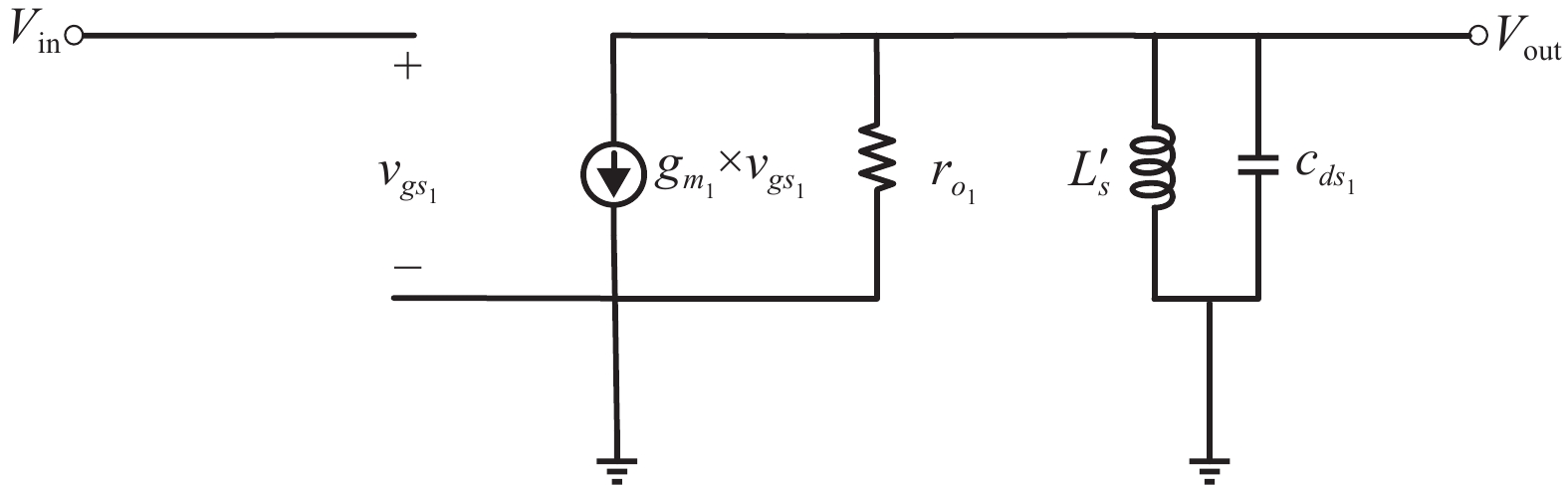

|

图 5 共源级小信号等效模型 Figure 5 Equivalent model of common source level small signal |

共源级增益

| ${A}_{\mathrm{v},\mathrm{c}\mathrm{s}}=-{g}_{{m}_{1}}{r}_{{o}_{1}}\frac{s\left(\dfrac{1}{{c}_{{ds}_{1}}}\right) }{{s}^{2}+s\left(\dfrac{1}{{r}_{{o}_{1}}{c}_{{ds}_{1}}}\right) +\dfrac{1}{{{L}}'_{{s}}{c}_{{ds}_{1}}}} $ | (10) |

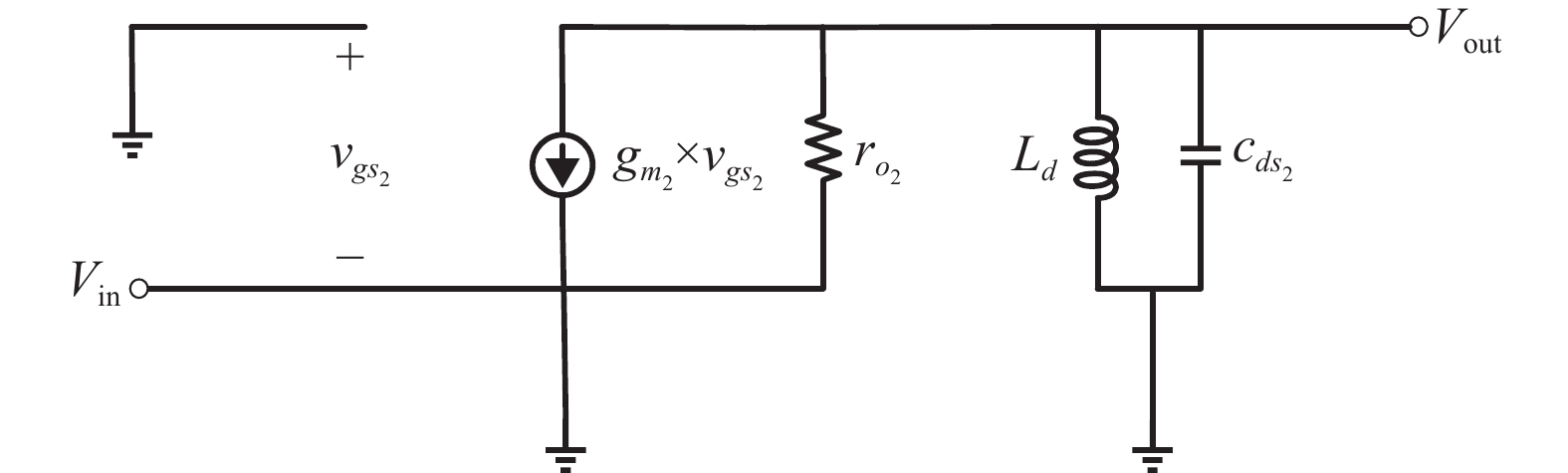

图6为共栅级小信号等效电路。

|

图 6 共栅级小信号等效模型 Figure 6 Equivalent model of common gate level small signal |

共栅级增益

| ${A}_{\mathrm{v},\mathrm{c}\mathrm{g}}=({g}_{{m}_{2}}{r}_{{o}_{2}}+1) \frac{\dfrac{s}{{r}_{{o}_{2}}{c}_{{ds}_{2}}}}{{s}^{2}+\dfrac{s}{{r}_{{o}_{2}}{c}_{{ds}_{2}}}+\dfrac{1}{{c}_{{ds}_{2}}{L}_{d}}}$ | (11) |

总增益

| ${A}_{\mathrm{v},\mathrm{T}}={A}_{\mathrm{v},\mathrm{c}\mathrm{s}}{A}_{\mathrm{v},\mathrm{c}\mathrm{g}} $ | (12) |

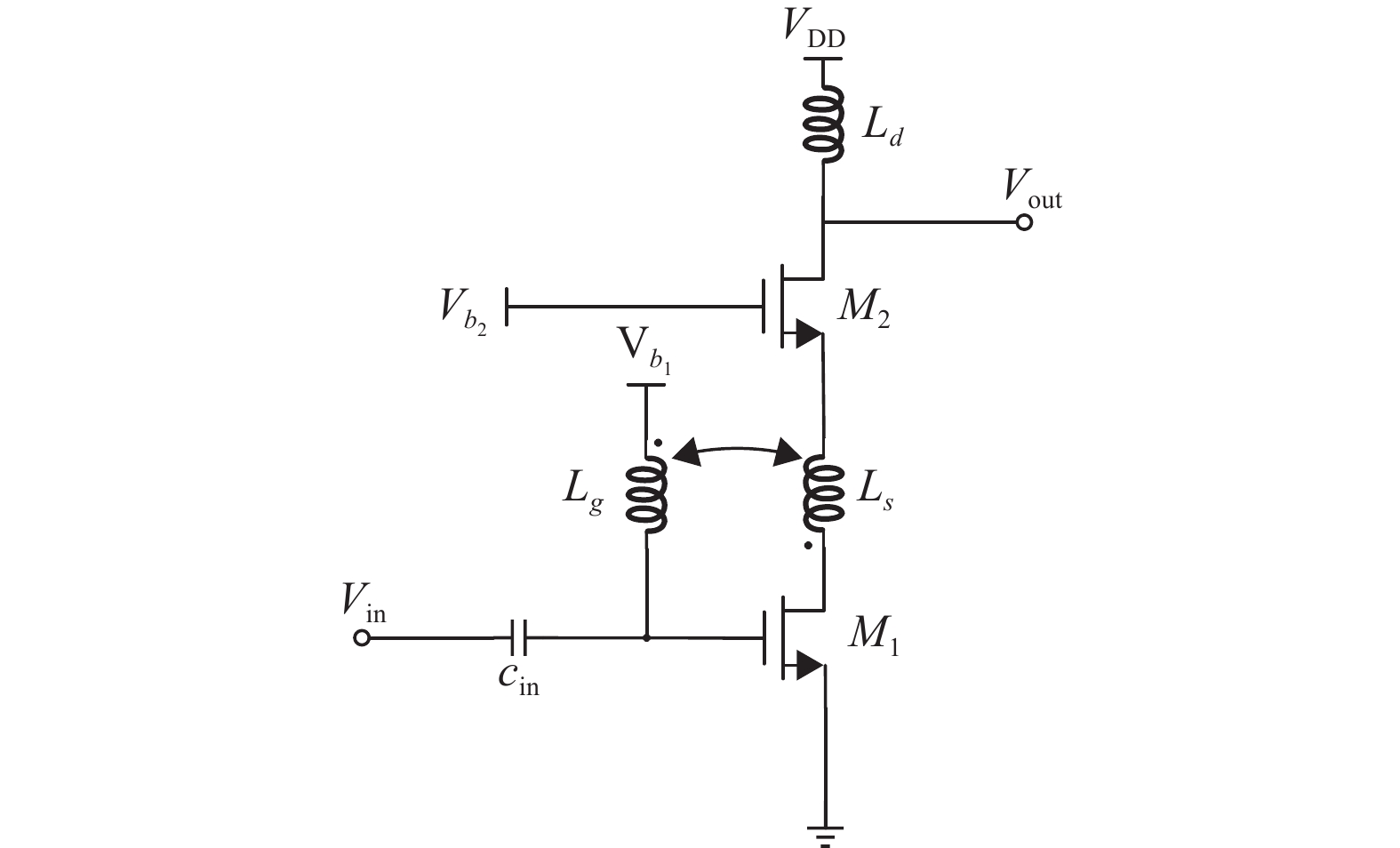

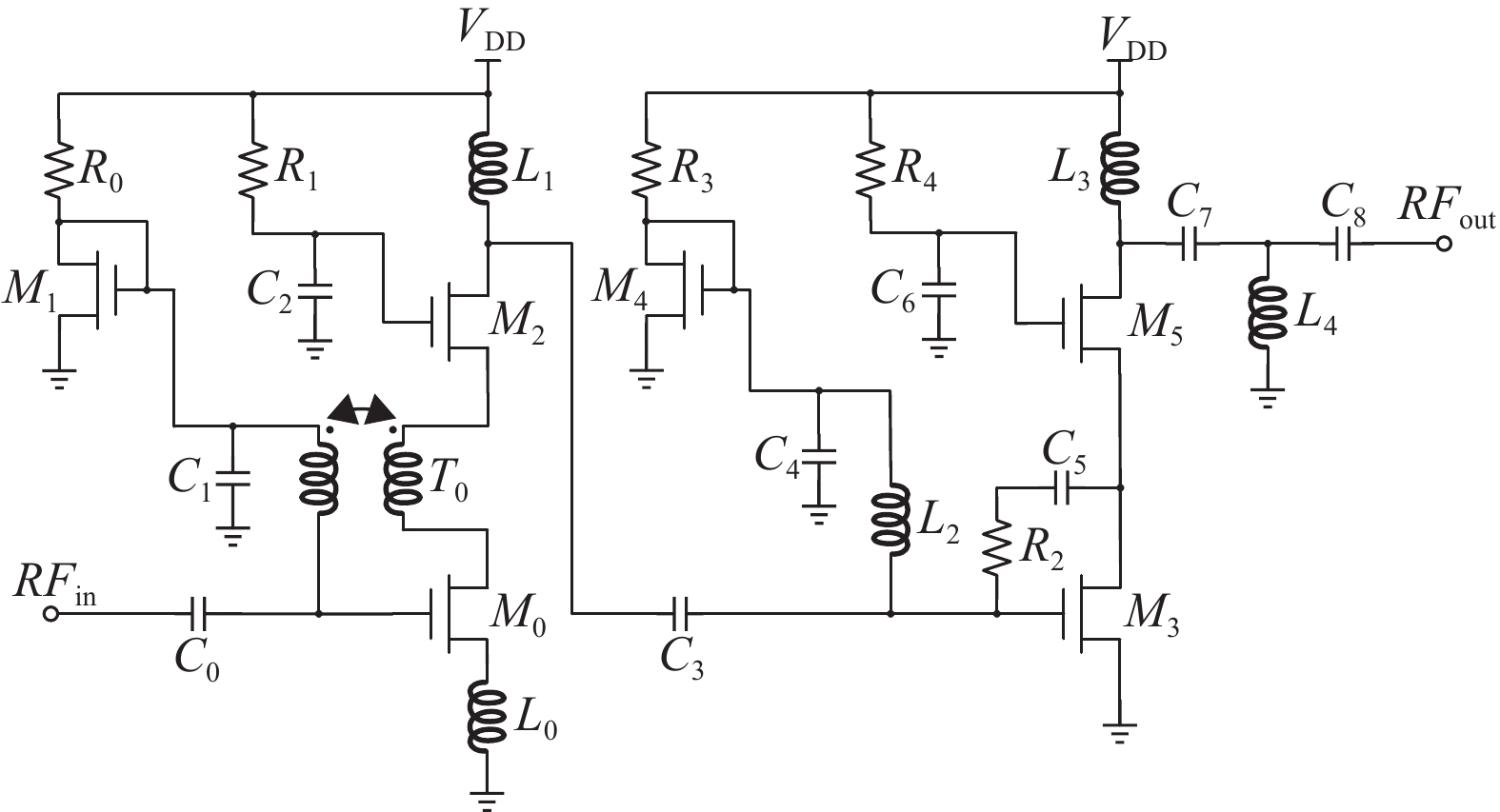

基于上述理论推导以及结论,本文设计一种应用于24~27 GHz频段的低噪声放大器,具体拓扑结构如图7所示。

|

图 7 两级共源共栅拓扑 Figure 7 Two level cascode topology |

本文设计的两级共源共栅低噪声放大器中,C0、T0分别构成了关键匹配网络——基于变压器的输入匹配网络,C0也用于进行隔离直流作用,M0、M2共同组成低噪声放大器的第一级共源共栅放大器,偏置电路采用了有源偏置电路结构。M0、M1、M2共同构成了电流镜的结构,其中电流镜结构可以产生稳定的偏置电流,并且产生的偏置电流可以通过M0、M1、M2两晶体管的宽长控制。L0为输入级共源共栅放大器的源极负反馈电感,C0为输入级的隔直电容,防止偏置电流分流到射频输入端口。R1、R4为分压电阻,通过调节阻值大小可以对M2、M5的栅压进行调节,R0、R3可以实现温度补偿作用,使得偏置电路提供的偏置电流更加稳定。C1、C2、C4、C6具有滤波作用,防止射频信号流入,L1是扼流电感,用以防止射频信号流到电源电压VDD,其值为1.1 V,并且L1也会参与级间匹配。L1、C3、L2构成Π型极间匹配网络,其中L2还起到了扼流的作用,防止射频信号流到偏置路。M3、M5共同组成低噪声放大器的第二级共源共栅放大器,偏置电路采用了有源偏置电路结构。M3、M4、M5共同构成了电流镜的结构。R2、C5构成RC串联回路,作为反馈回路链接M3栅极和漏极,提升低噪声放大器的稳定性,使低噪声放大器获得一个优异的增益平坦度。L3是扼流电感,用以防止射频信号流到电源电压VDD,并且L3也会参与输出匹配。L3、C7、L4、C8构成了输出级的两节LC输出匹配网络,其中C8也用于输出级的隔直电容,用来隔离直流分量对电路的影响。

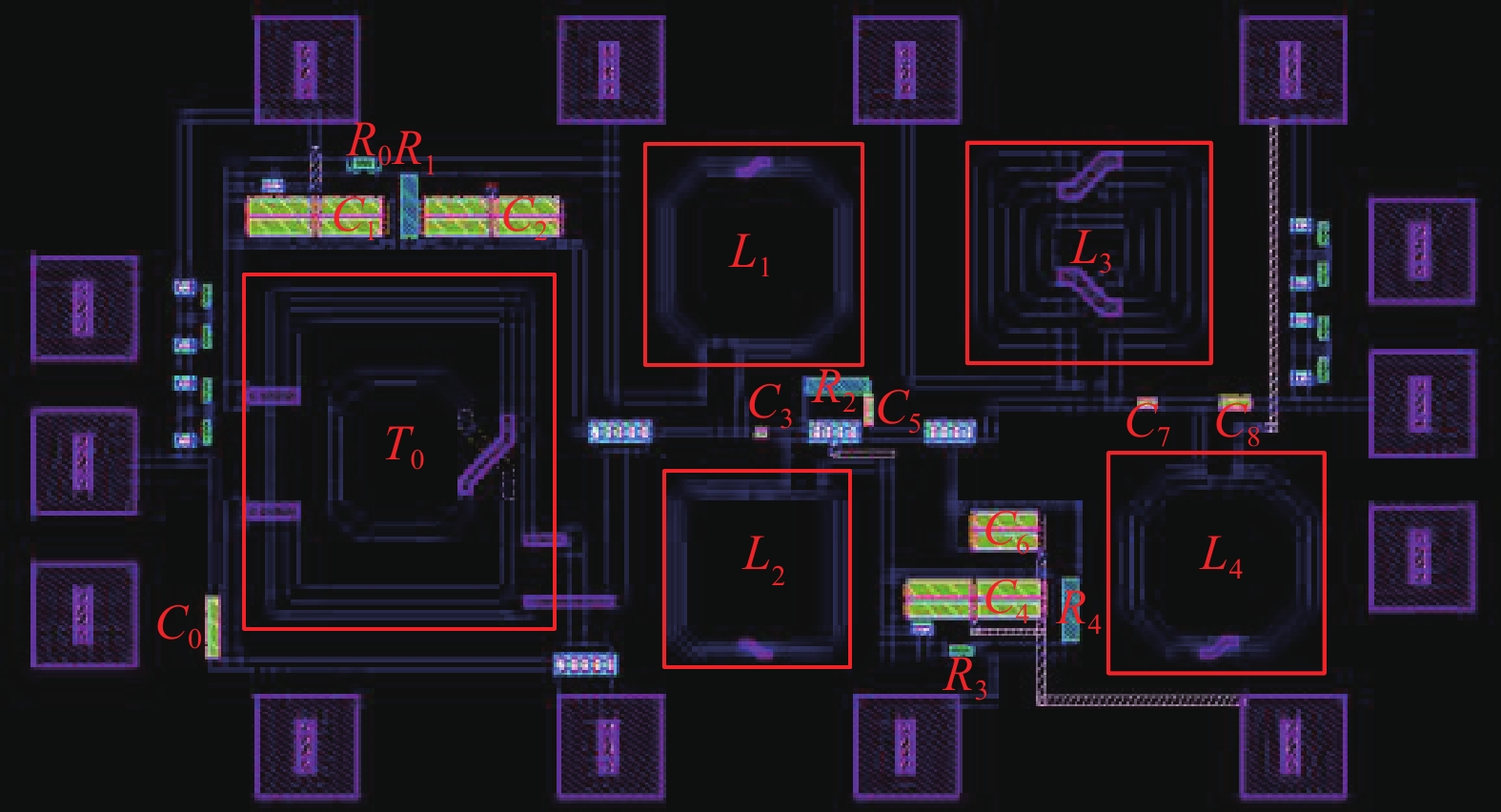

2 版图仿真及讨论 2.1 版图仿真及结果基于该变压器正反馈结构及有源偏置两级共源共栅低噪声放大器拓扑设计进行版图绘制,其中,源极负反馈电感拟采用键合线电感。

版图设计基于面积最小的原则,需要尽可能避免器件(尤其是电感)发生耦合而导致阻抗发生的改变[15-16]。基于此,在每个电感之间,本文设计中留有25 μm的距离,尽可能地将有限的面积进行利用。

采用40 nm CMOS工艺进行版图绘制,版图面积为383 μm×694 μm,即

|

图 8 版图 Figure 8 Layout |

图9给出了上述版图在慢工艺角SS(Slow-Slow)、典型工艺角TT(Typical-Typical)、快工艺角FF(Fast-Fast) 3种工艺角下的噪声系数(Noise Figure,NF)、增益(S(2,1) )、输入回波损耗(S(1,1) )、输出回波损耗(S(2,2) )、线性度(P1dB)、稳定性系数(kf)、稳定性因子(b)的仿真曲线。

|

图 9 版图后仿真曲线 Figure 9 Post-layout Simulation |

由图9可见,在工作温度−40~125 ℃范围内,本文设计的低噪声放大器在24~27 GHz频段内,噪声系数NF小于6.00 dB,增益S(2,1) 大于14.69 dB,最大增益(Max Gain)为19.46 dB,输入回波损耗S(1,1) 小于−15.59 dB,输出回波损耗S(2,2) 小于−10.01 dB,P1dB为−22.15 dBm,稳定性系数kf在频带内外均大于1,稳定性因子b在频带内外均大于0。在常温27 ℃下的性能指标已在表1中展示。

| 表 1 低噪声放大器性能对比 Table 1 Performance comparison with other LNAs |

表1为本文所设计的低噪声放大器与其他文献低噪声放大器常温下的性能对比,由表中数据可以看出,本文设计的低噪声放大器在噪声和线性度方面具有明显优势。此外,考虑到不同架构下的设计方案,本文采用叠加电感形成变压器的方法,有效节省了版图面积,展现了一定的面积优势。

3 结论本文采用40 nm CMOS工艺,设计了一种高增益低噪声放大器。将变压器匹配特性应用在两级共源共栅放大器中,使低噪声放大器的输入回波损耗更加优良。同时,采用了一种同相放大的电路结构,提高了低噪声放大器在前级的增益,进而提升整体低噪声放大器的增益。

本文设计的低噪声放大器在24~27 GHz 频段内常温27 ℃下的噪声低于4.96 dB,增益优于16.84 dB,输入回波损耗小于−16.08 dB,输出回波损耗小于−11.54 dB,直流功耗Pdiss为12.8 mW。该设计可为满足高增益低噪声的射频系统提供架构参考。

| [1] |

FU J, BARDEH M G, PARAMESH J, et al. A millimeter-wave concurrent LNA in 22-nm CMOS FDSOI for 5G applications[J].

IEEE Transactions on Microwave Theory and Techniques, 2022, 71(3): 1031-1043.

|

| [2] |

QIAN Y, SHEN Y, HU S. Millimeter-wave CMOS low-noise amplifier with high gain and compact footprint[J].

IEEE Microwave and Wireless Technology Letters, 2023, 33(6): 699-702.

DOI: 10.1109/LMWT.2023.3246166. |

| [3] |

DAS T. Practical considerations for low noise amplifier design[J].

Freescale Semiconductor, 2013, 10: 1-10.

|

| [4] |

XING Z, LIANG Q, XU R. A Design on silicon-based millimeter-wave low noise amplifier circuits[C]//2024 IEEE 7th International Conference on Electronic Information and Communication Technology (ICEICT). Xi’an: IEEE, 2024: 757-759.

|

| [5] |

XU H, WEN K. Design of a 20-to-40 GHz millimetre-wave ultra-wideband low noise amplifier in 55-nm CMOS[C]//2024 20th International Conference on Natural Computation, Fuzzy Systems and Knowledge Discovery (ICNC-FSKD). Guangzhou: IEEE, 2024: 1-6.

|

| [6] |

ARIAS-PURDUE A, GUIDRY M, LAM E, et al. Inductive source degeneration in 40-nm GaN HEMTs for operation above 100 GHz[J].

IEEE Transactions on Microwave Theory and Techniques, 2023, 72(1): 26-35.

|

| [7] |

HU Y, CHI T. A systematic approach to designing broadband millimeter-wave cascode common-source with inductive degeneration low noise amplifiers[J].

IEEE Transactions on Circuits and Systems I: Regular Papers, 2023, 70(4): 1489-1502.

DOI: 10.1109/TCSI.2023.3239396. |

| [8] |

KHYALIA S K, ZELE R H, CHIONG C C, et al. A 22-33-GHz Gm-boosting low-power noise-canceling LNA in 40-nm CMOS process[J].

IEEE Transactions on Microwave Theory and Techniques, 2024, 72(7): 4017-4027.

DOI: 10.1109/TMTT.2024.3349605. |

| [9] |

FENG G, ZHENG L, WANG Y, et al. A 0.5-V 0.88-mW low noise amplifier with active and passive Gm enhancements in sub-6 GHz band[J].

IEEE Microwave and Wireless Technology Letters, 2023, 33(8): 1159-1162.

DOI: 10.1109/LMWT.2023.3276915. |

| [10] |

KE J, LIN Z, FENG G, et al. A 52–73-GHz LNA with tri-coupled transformer for Gm-boosting and enhanced noise canceling[J].

IEEE Journal of Solid-State Circuits, 2024, 59(3): 668-676.

DOI: 10.1109/JSSC.2023.3340300. |

| [11] |

HAN A, LUO X. A 60-GHz current-reused cascode noise-canceling low noise amplifier[J]. IEEE Transactions on Circuits and Systems II: Express Briefs, 2024, 1-1.

|

| [12] |

KOBAL E, SIRIBURANON T, STASZEWSKI R B, et al. A compact, low-power, low-NF, millimeter-wave cascode LNA with magnetic coupling feedback in 22-nm FD-SOI CMOS for 5G applications[J].

IEEE Transactions on Circuits and Systems II: Express Briefs, 2022, 70(4): 1331-1335.

|

| [13] |

GUO S, XI T, GUI P, et al. A transformer feedback Gm-boosting technique for gain improvement and noise reduction in mm-wave cascode LNAs[J].

IEEE Transactions on Microwave Theory and Techniques, 2016, 64(7): 2080-2090.

DOI: 10.1109/TMTT.2016.2564398. |

| [14] |

WALLING J S, SHEKHAR S, ALLSTOT D J. A G m-boosted current-reuse LNA in 0.18 μm CMOS[C]//2007 IEEE Radio Frequency Integrated Circuits (RFIC) Symposium. Honolulu: IEEE, 2007: 613-616.

|

| [15] |

URAIN A, DEL RIO D, GURUTZEAZA I, et al. Design and layout considerations of a D-Band SiGe LNA for radiometric applications[C]//2021 XXXVI Conference on Design of Circuits and Integrated Systems (DCIS). Vila do Conde, Portugal: IEEE, 2021: 1-5.

|

| [16] |

STEFANOVSKA A, WANG Z G. Ka-Band LNA design using systematic circuit design methodology and design applicable equations[C]//2022 7th International Conference on Integrated Circuits and Microsystems (ICICM). Xi'an: IEEE, 2022: 86-91.

|

| [17] |

KONG S, LEE H D, JANG S, et al. A 28-GHz CMOS LNA with stability-enhanced G m-boosting technique using transformers[C]//2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC). Boston: IEEE, 2019: 7-10.

|

| [18] |

QIN P, XUE Q. Compact wideband LNA with gain and input matching bandwidth extensions by transformer[J].

IEEE Microwave and Wireless Components Letters, 2017, 27(7): 657-659.

DOI: 10.1109/LMWC.2017.2711524. |

| [19] |

HEDAYATI M K, ABDIPOUR A, SHIRAZI R S, et al. A 33-GHz LNA for 5G wireless systems in 28-nm bulk CMOS[J].

IEEE Transactions on Circuits and Systems II: Express Briefs, 2018, 65(10): 1460-1464.

|

| [20] |

LEE S, HONG S. Frequency-reconfigurable dual-band low-noise amplifier with interstage Gm-boosting for millimeter-wave 5G communication[J].

IEEE Microwave and Wireless Technology Letters, 2023, 33(4): 463-466.

DOI: 10.1109/LMWT.2022.3220975. |

| [21] |

TAERQ M M H, JAHAN N, HOSSAIN Q D. Design of a millimeter-wave band LNA using SIW resonator in 180-nm CMOS technology[C]//2023 6th International Conference on Electrical Information and Communication Technology (EICT). Boston: IEEE, 2023: 1-5.

|

| [22] |

RADPOUR M, BELOSTOTSKI L. Wideband LNA employing intrinsic feedback and back-gate resistance for noise and input power matching[J].

IEEE Transactions on Microwave Theory and Techniques, 2023, 72(6): 3373-3386.

|

2024, Vol. 41

2024, Vol. 41