2. 广东工业大学 集成电路学院, 广东 广州 510006

2. School of Integrated Circuit, Guangdong University of Technology, Guangzhou 510006, China

Pipelined-SAR ADC同时拥有流水线型ADC (pipeline ADC) 和逐次逼近型ADC (SAR ADC) 的优点,是近年来ADC领域的研究热点[1-2]。由于采用SAR ADC作为子ADC,pipelined-SAR ADC在相同分辨率下可以比pipeline ADC使用更少的高精度比较器和参考电压源,减小了ADC的芯片面积和电路复杂度[3]。此外,采用中等分辨率的SAR ADC作为子ADC可以减少级间残差放大器的数量,有效地降低ADC的功耗[4]。

在pipelined-SAR ADC中,级间残差放大器(Residue Amplifier, RA) 的作用是将前级子ADC的信号残差放大并传到下一级子ADC。传统级间残差放大器采用开关电容电路和运算放大器实现,级间增益为

目前应用在先进CMOS工艺和低电源电压工作条件下的运算放大器结构主要有两种,分别是动态放大器和环形放大器。动态放大器[7-8]可以实现开环残差放大,无需开关电容电路和反馈环路,可以实现较低的功耗和较小的芯片面积,但其增益精度容易受到工艺、电源电压和温度(Process, Voltage and Temperature, PVT) 的影响,需要额外的电路或校准算法进行补偿。环形放大器[9-11]得益于其多级反相器链的结构,可以在低电源电压下工作,同时具有轨对轨的输出摆幅。但是在先进工艺中,环形放大器也难以实现较高的开环增益,如文献[11]中的环形放大器开环增益仅为80 dB。

为了减小级间增益误差,本文提出了一种增益增强型全差分环形放大器,并将其应用于16位25 MS/s的pipelined-SAR ADC中。与传统的环形放大器相比,本文提出的环形放大器采用增益增强型输出级可以实现更大的开环增益,开环增益超过90 dB,可以有效减小级间残差增益误差。此外,该环形放大器采用开关电容实现全局动态共模反馈保证环形放大器的稳定性,同时降低静态功耗。

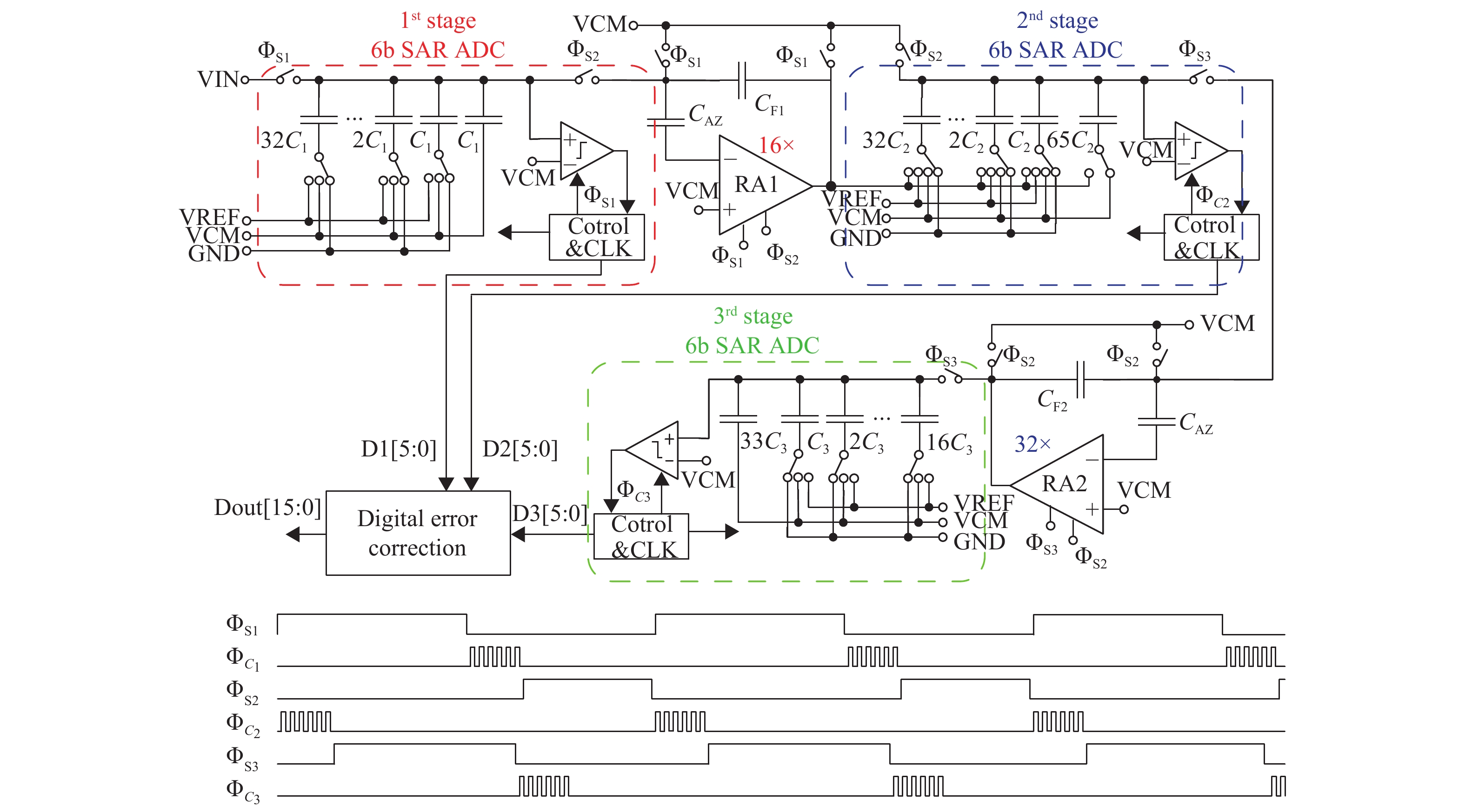

1 ADC整体结构图1展示了基于增益增强型环形放大器的16位25 MS/s的pipelined-SAR ADC的结构图。本文提出的pipelined-SAR ADC包括三个6位SAR ADC作为子ADC以及两个级间残差放大器。其中,第一级残差放大器和第二级残差放大器的级间增益分别为16倍和32倍。每一级SAR ADC之间存在1位冗余位用于校正级间失调。第一级残差放大器采用增益减半技术,通过降低级间残差增益从而降低对运算放大器开环增益以及输出摆幅的要求[3]。第二级和第三级子ADC中采用参考电压减半技术,减少ADC所需的参考电压源数量[3]。每一级SAR ADC电路均采用异步SAR逻辑以实现较高的转换速度,并采用基于共模电压的开关时序方案降低功耗。对ADC的性能和所需的芯片面积进行折中考虑,第一级SAR ADC的采样电容为3.2 pF,第二级SAR ADC的采样电容为640 fF,第三级SAR ADC的采样电容为320 fF。

|

图 1 Pipelined-SAR ADC的结构图和时序图 Figure 1 Block and timing diagrams of the pipelined-SAR ADC |

Pipelined-SAR ADC的时序图如图1所示,其中,

级间残差放大器的级间增益精度决定了ADC可实现的分辨率。环形放大器的开环增益

| $\frac{{A}_{\mathrm{i}\mathrm{d}\mathrm{e}\mathrm{a}\mathrm{l}}}{\left(1+{A}_{\mathrm{R}\mathrm{A}}\beta \right) } < \frac{1}{2}{2}^{F-B}$ | (1) |

式中,

|

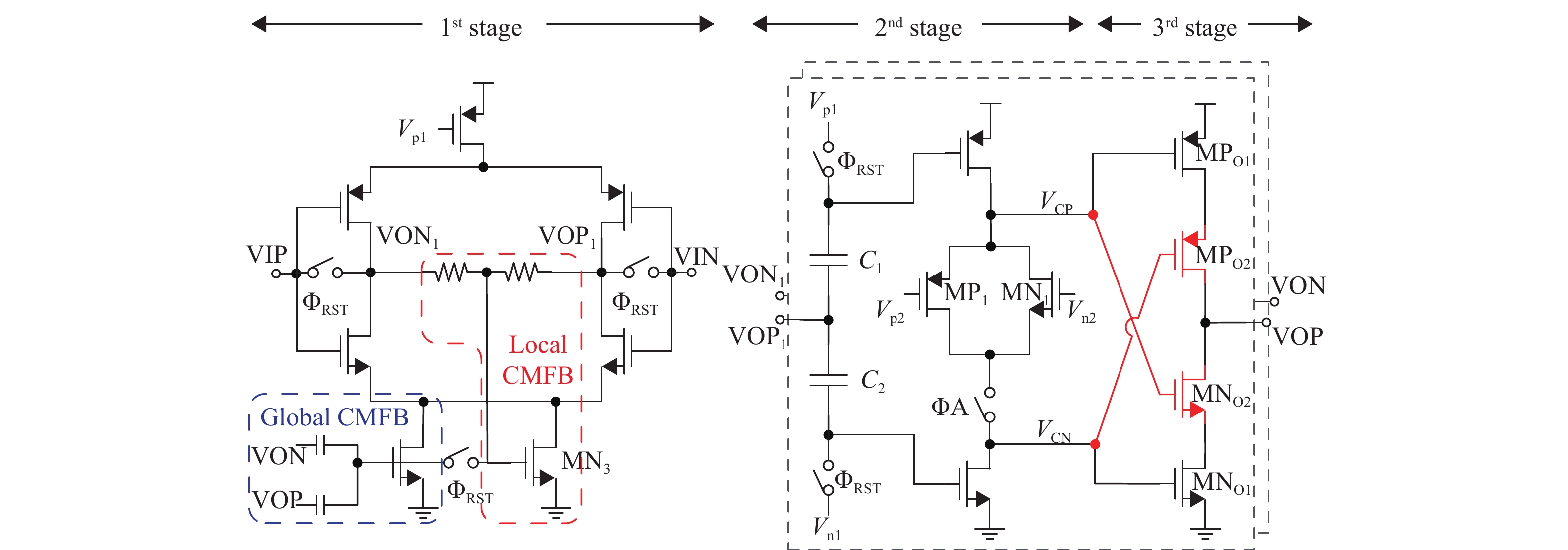

图 2 本文提出的增益增强型全差分环形放大器 Figure 2 Proposed gain-enhanced fully differential ring amplifier |

环形放大器第一级采用电流复用技术提高输入跨导

环形放大器第二级和第一级通过电容

| $ {V}_{\mathrm{N},\mathrm{R}\mathrm{A}}^{2}=\frac{4kT\gamma }{{g}_{\mathrm{m}1}}+\frac{4kT\gamma }{{A}_{1}^{2}{g}_{\mathrm{m}2}}+\frac{4kT\gamma }{{{A}_{1}^{2}{A}_{2}^{2}g}_{\mathrm{m}3}}+\frac{kT}{{{A}_{1}^{2}C}_{\mathrm{1,2}}} $ | (2) |

式中,

为了提高稳定性和输出阻抗,环形放大器输出级偏置需要引入死区电压。本文环形放大器的死区电压

环形放大器第三级为增益增强型输出级,堆叠晶体管

| $ {R}_{\mathrm{o}\mathrm{u}\mathrm{t}}\approx \left({r}_{\mathrm{O}2,\mathrm{N}}+{g}_{\mathrm{m}2,\mathrm{N}}{r}_{\mathrm{O}2,\mathrm{N}}{r}_{\mathrm{O}1,\mathrm{N}}\right) \parallel \left({r}_{\mathrm{O}2,\mathrm{P}}+{g}_{\mathrm{m}2,\mathrm{P}}{r}_{\mathrm{O}2,\mathrm{P}}{r}_{\mathrm{O}1,\mathrm{P}}\right) $ | (3) |

相比于传统环形放大器的输出阻抗

|

图 3 本文的环形放大器和传统环形放大器的频率响应 Figure 3 Frequency response of the proposed ring amplifier and conventional ring amplifier |

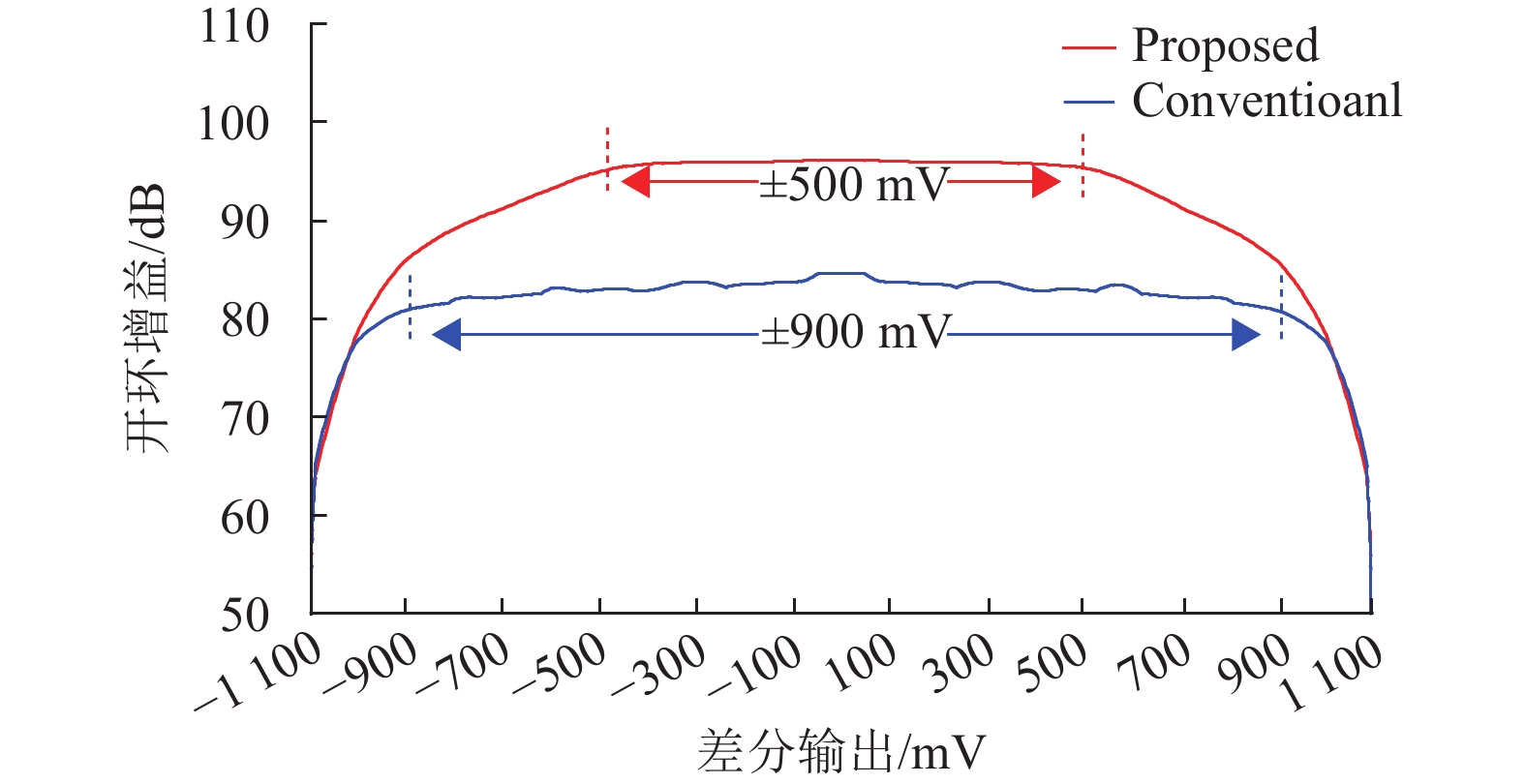

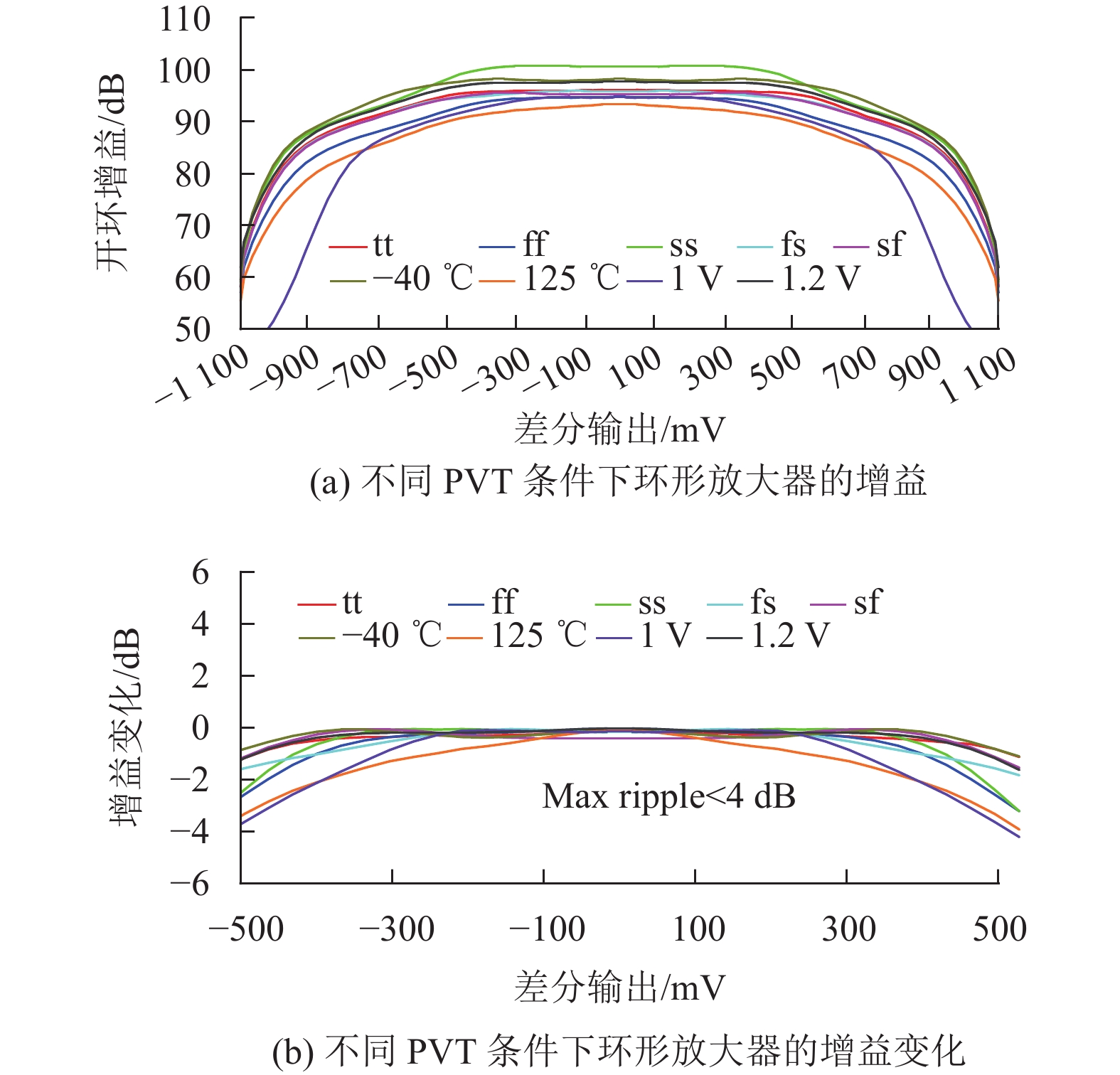

图4展示了本文提出的环形放大器和传统环形放大器的开环增益与差分输出电压的关系。增益增强型环形放大器在整个输出范围内都比传统环形放大器具有更大的开环增益。由于输出级采用了堆叠结构,当差分输出范围超过500 mV时,增益增强型环形放大器开环增益有所下降。为了验证增益增强型环形放大器的稳定性,在不同PVT条件下对环形放大器进行仿真,仿真结果如图5所示。在不同PVT条件下,所提出的环形放大器仍可以实现大于90 dB的开环增益。在500 mV的差分输出范围内,本文提出的环形放大器的开环增益的变化小于4 dB,这表明该环形放大器具有很好的线性度。

|

图 4 本文提出的环形放大器和传统环形放大器的开环增益与差分输出电压的关系 Figure 4 Proposed ring amplifier open-loop gain versus differential output voltage compared with that of conventional ring amplifier |

|

图 5 本文提出的环形放大器在不同PVT条件下的开环增益与差分输出电压的关系 Figure 5 Proposed ring amplifier open-loop gain versus differential output voltage considering PVT variation |

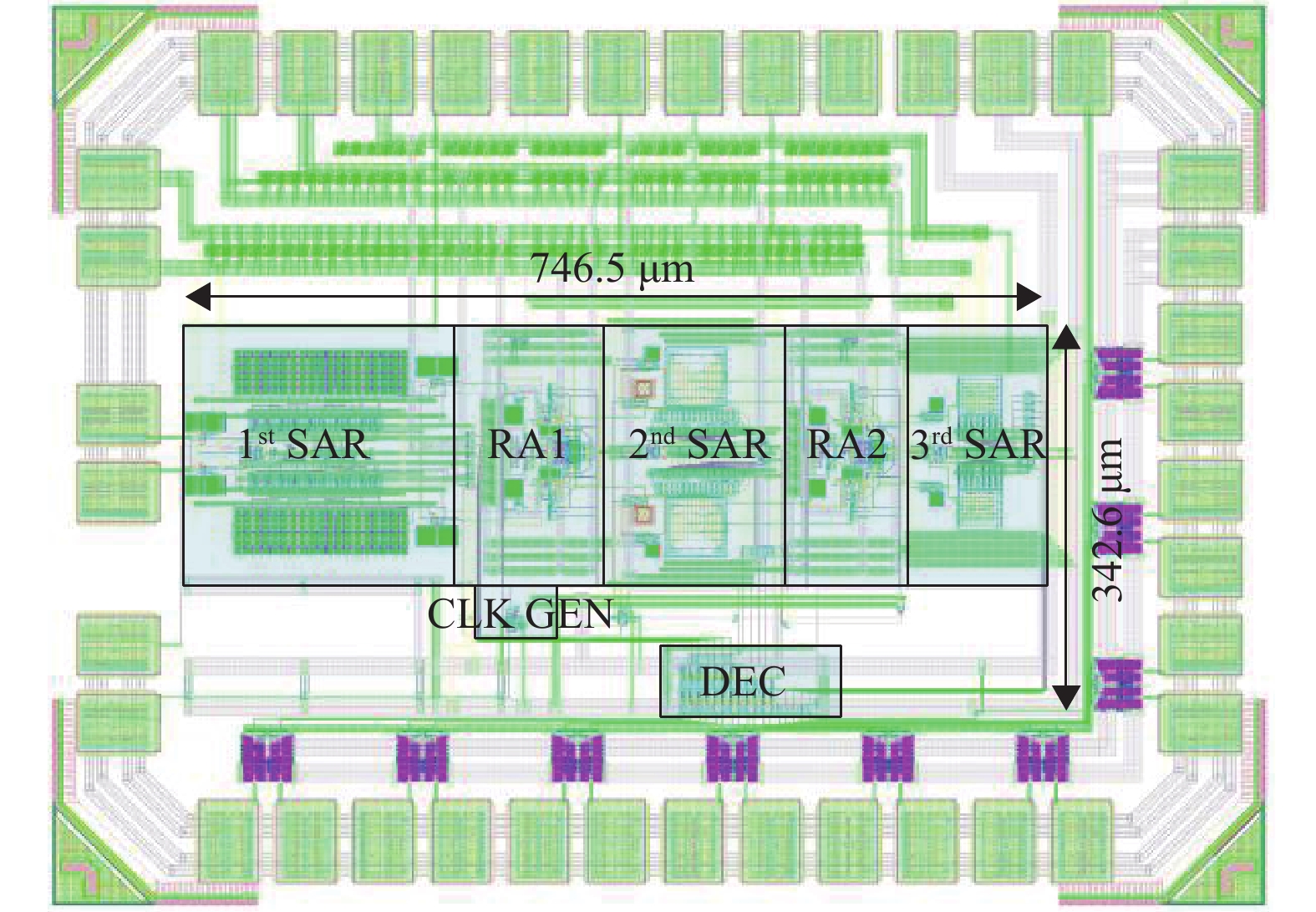

本文基于65 nm CMOS工艺设计了一款16位pipelined-SAR ADC,完整版图如图6所示。该ADC的面积为0.256 mm2,工作电源电压为1.1 V,差分输入摆幅为2.2 V。在25 MS/s采样频率下,测得ADC的平均功耗为2.8 mW,其中环形放大器功耗为2.35 mW(84%),SAR ADC功耗为0.19 mW(7%),时钟电路及其他数字电路的功耗为0.26 mW(9%)。

|

图 6 本文设计的ADC版图 Figure 6 Layout of the proposed ADC |

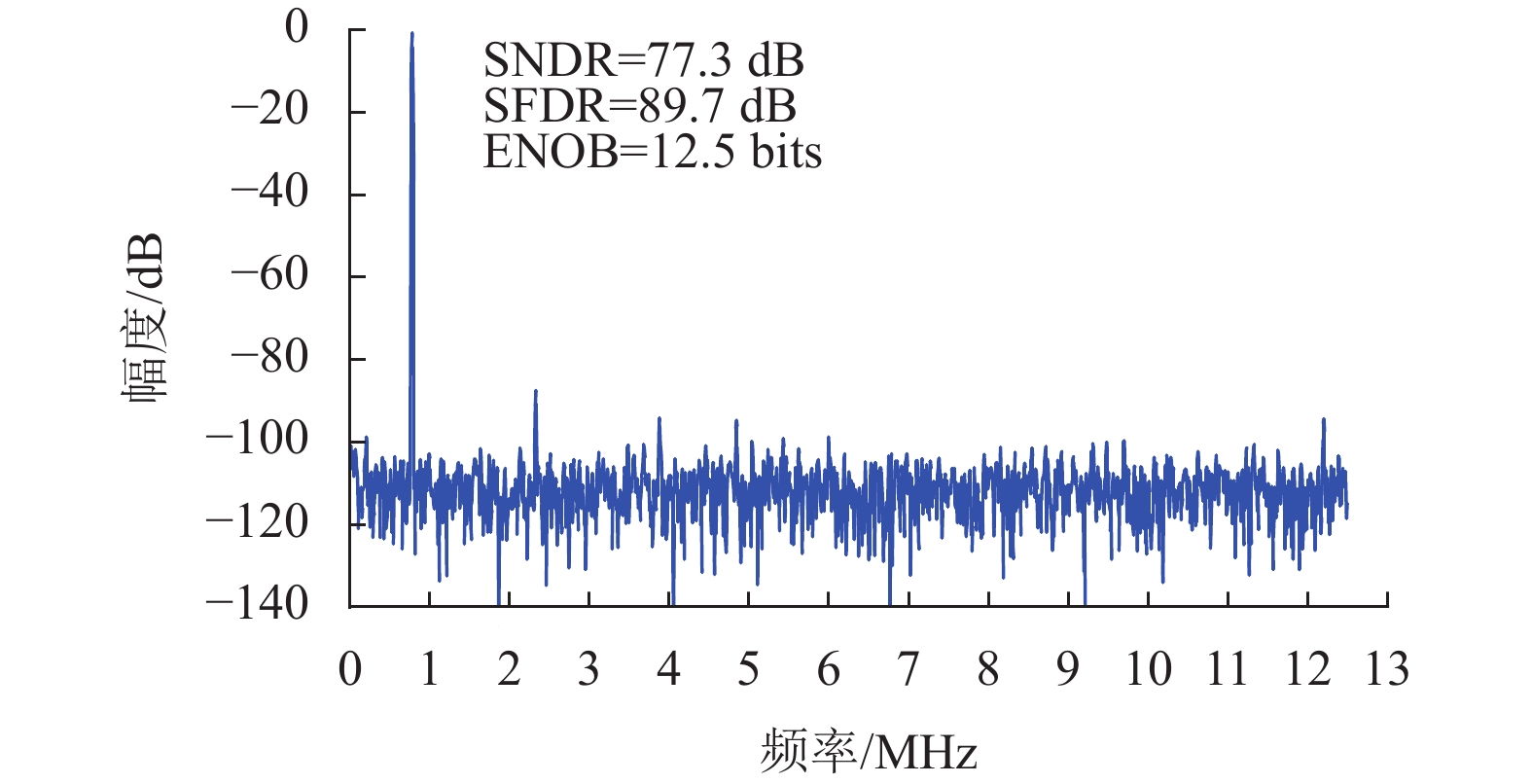

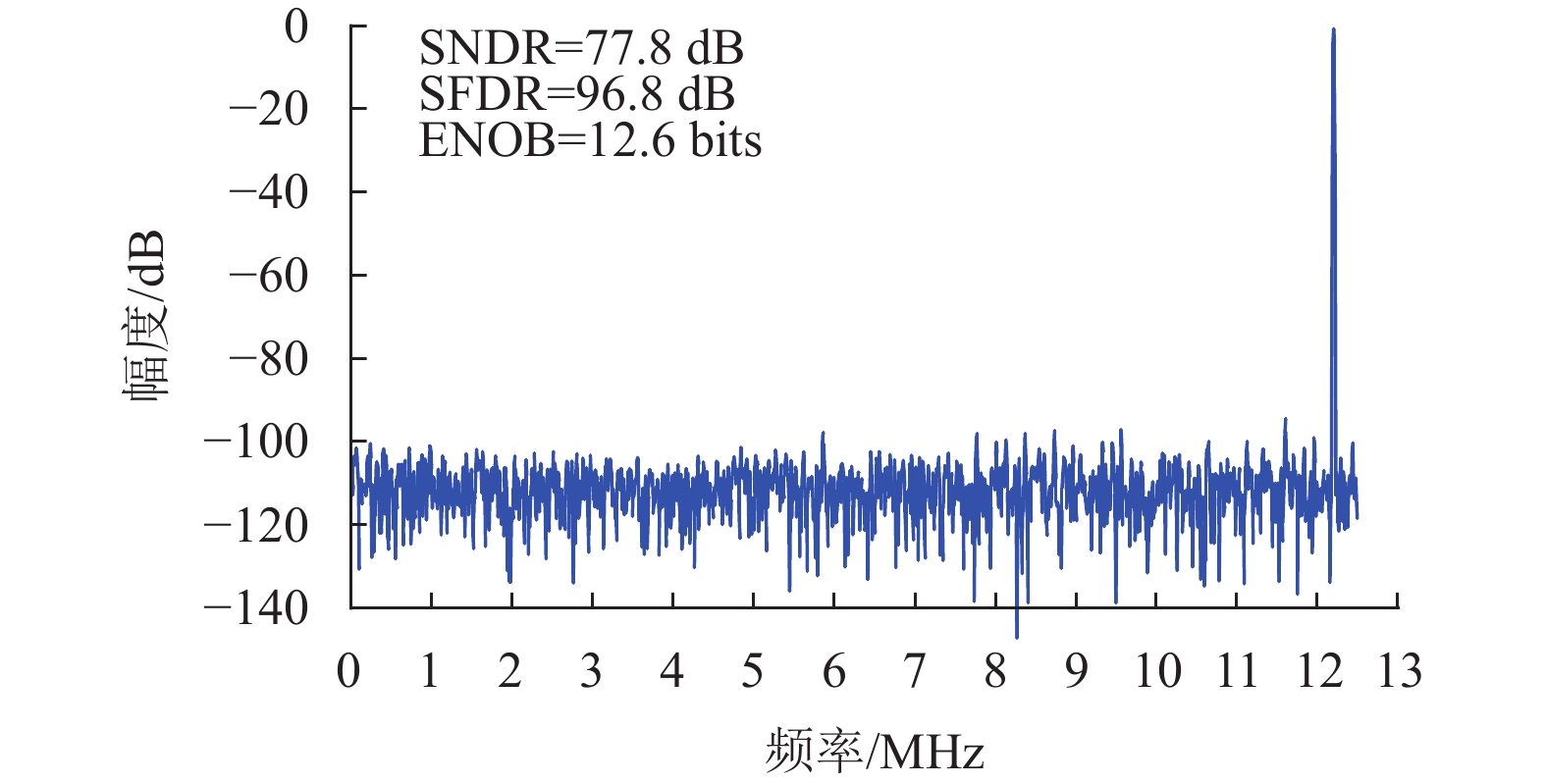

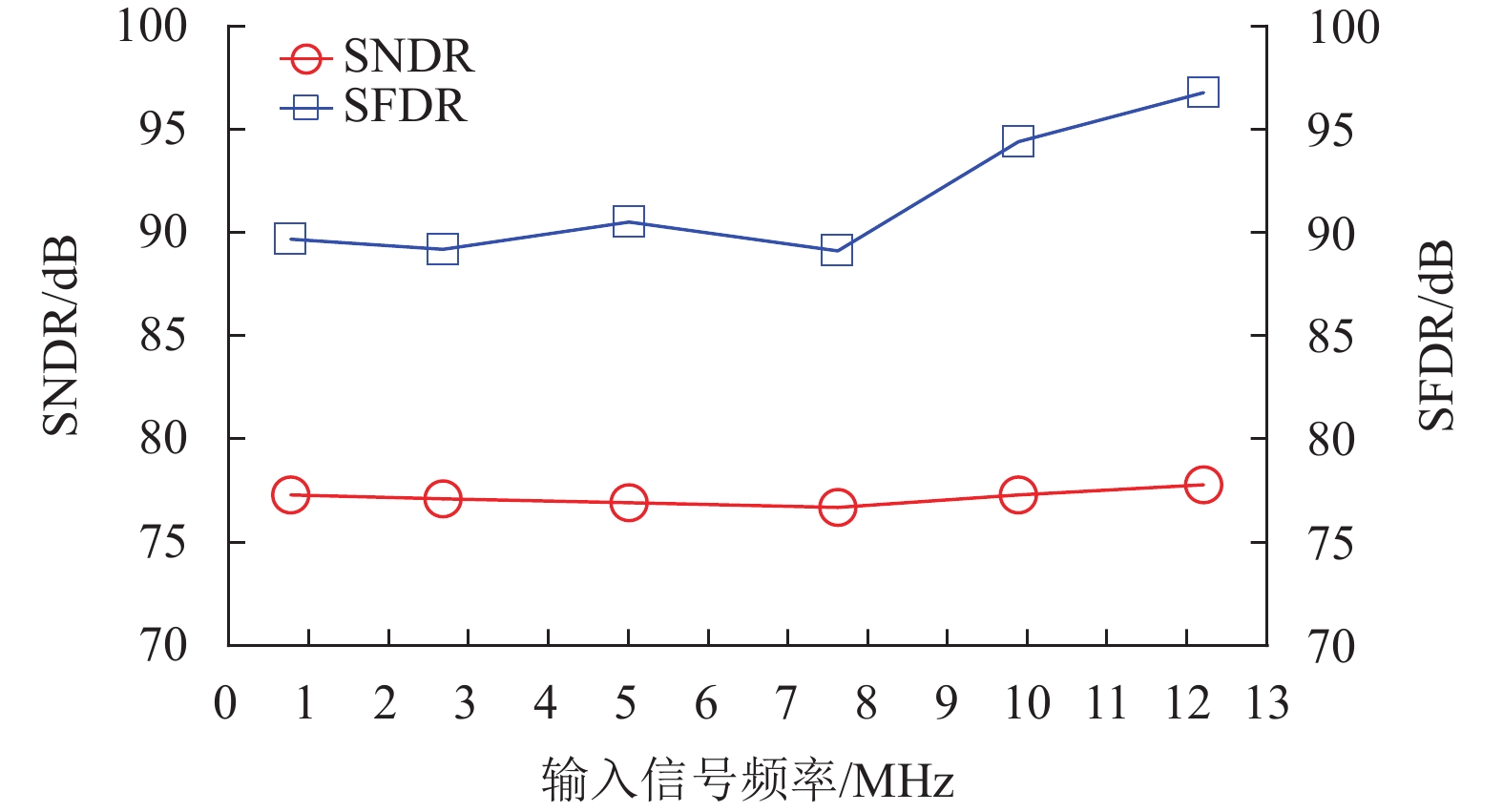

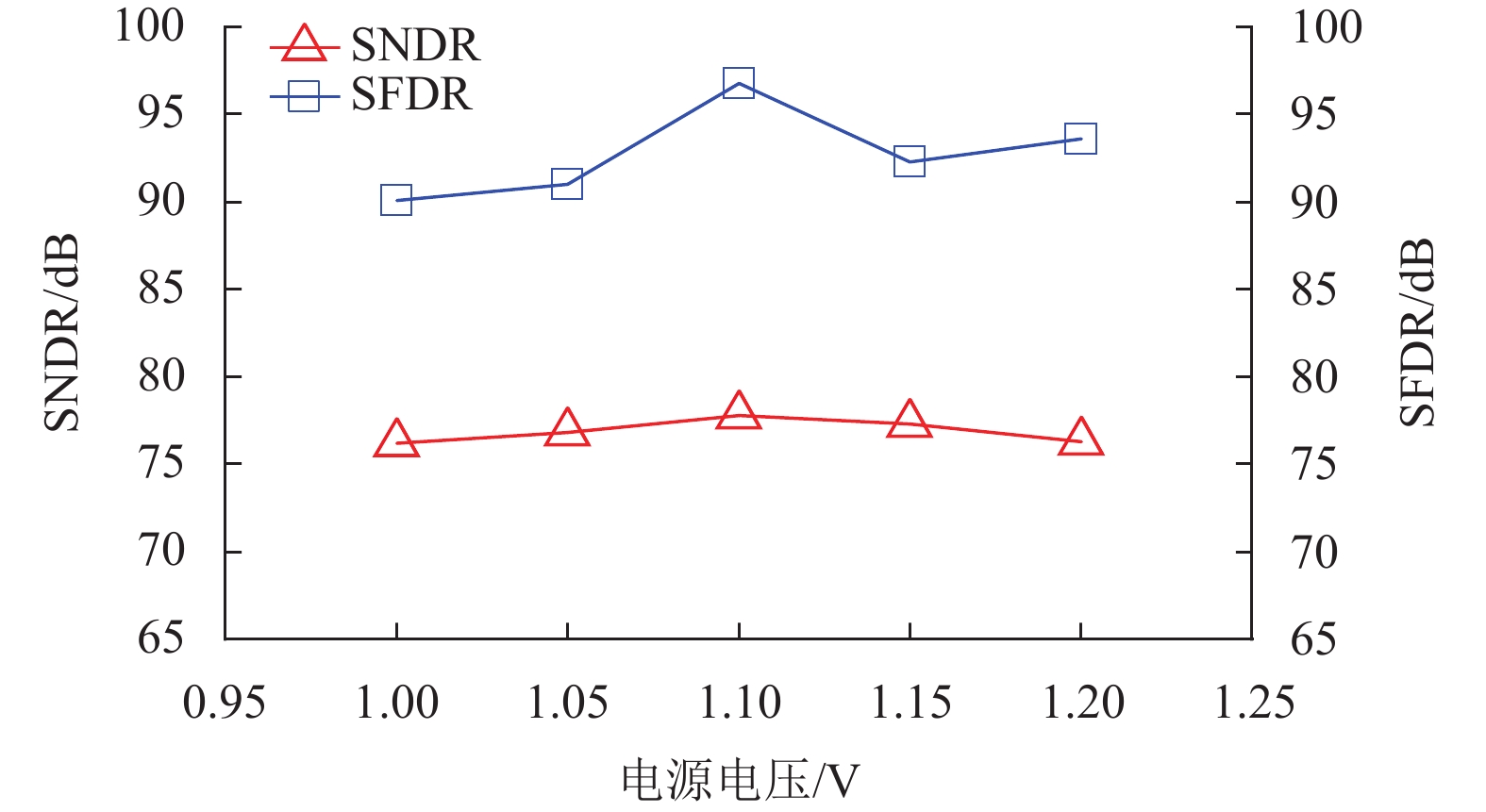

Pipelined-SAR ADC的SNDR主要受限于SAR ADC的采样噪声和级间残差放大器的等效输入噪声。在25 MS/s采样频率下,0.8 MHz输入信号时的ADC输出频谱如图7所示,ADC的SNDR和SFDR分别为77.3 dB和89.7 dB,有效位为12.5 bits。图8展示了12.2 MHz输入信号时的ADC输出频谱,ADC的SNDR和SFDR分别为77.8 dB和96.8 dB,有效位为12.6 bits。图9展示了不同输入频率下ADC的动态性能仿真结果,可以看到在整个奈奎斯特频率范围内,ADC都可实现超过85 dB的SFDR。图10展示了环形放大器在不同工作电压下ADC的动态性能。环形放大器的工作电压在1.0~1.2 V范围变化时,ADC的SNDR和SFDR变化较小,分别变化了1.6 dB和6.7 dB。这表明所设计的增益增强型环形放大器对电源电压变化不敏感,稳定性较好。

|

图 7 0.8 MHz输入信号时ADC输出频谱 Figure 7 Simulated ADC spectrum for 0.8 MHz inputs |

|

图 8 12.2 MHz输入信号时ADC输出频谱 Figure 8 Simulated ADC spectrum for 12.2 MHz inputs |

表1中将本文设计的pipelined-SAR ADC与已有文献的ADC的性能进行对比,本文的ADC具有最优的FoM值,与文献[13]相近,在SFDR方面优于文献[14-15],但是由于文献[13]采用校准电路导致其功耗较高。在相近的分辨率情况下,本文ADC的功耗最小,功耗为2.8 mW。

| 表 1 性能对比1) Table 1 Performance comparison |

|

图 9 不同输入频率下动态性能仿真结果 Figure 9 Simulated dynamic performance versus different input frequencies |

|

图 10 环形放大器在不同电源电压下ADC的动态性能 Figure 10 Simulated ADC dynamic performance versus different ring amplifier power supplies |

本文提出了一款基于增益增强型环形放大器的16位pipelined-SAR ADC。与传统的环形放大器相比,增益增强型环形放大器可以实现超过90 dB的开环增益,有效提升了pipelined-SAR ADC的线性度。基于所提出的增益增强型环形放大器,本文设计的pipelined-SAR ADC在无需校准的条件下,在25 MS/s采样频率实现了77.8 dB的SNDR和96.8 dB的SFDR,功耗为2.8 mW,具有高精度低功耗的优点。

| [1] |

JIANG W, ZHU Y, CHEN C, et al. A 14b 500 MS/s single-channel pipelined-SAR ADC with reference ripple mitigation techniques and adaptively biased floating inverter amplifier[J].

IEEE Journal of Solid-State Circuits, 2023, 58(10): 2709-2721.

DOI: 10.1109/JSSC.2023.3290119. |

| [2] |

WANG J C, KUO T H. A 72-dB SNDR 130-MS/s 0.8-mW pipelined-SAR ADC using a distributed averaging correlated level shifting ring amplifier[J].

IEEE Journal of Solid-State Circuits, 2022, 57(12): 3794-3803.

DOI: 10.1109/JSSC.2022.3196743. |

| [3] |

LEE C C, FLYNN M P. A SAR-assisted two-stage pipeline ADC[J].

IEEE Journal of Solid-State Circuits, 2011, 46(4): 859-869.

DOI: 10.1109/JSSC.2011.2108133. |

| [4] |

WANG J C, HUNG T C, KUO T H. A calibration-free 14-b 0.7-mW 100-MS/s pipelined-SAR ADC using a weighted-averaging correlated level shifting technique[J].

IEEE Journal of Solid-State Circuits, 2020, 55(12): 3271-3280.

DOI: 10.1109/JSSC.2020.3015863. |

| [5] |

KARANICOLAS A N, LEE H S, BARCRANIA K L. A 15-b 1-Msample/s digitally self-calibrated pipeline ADC[J].

IEEE Journal of Solid-State Circuits, 1993, 28(12): 1207-1215.

DOI: 10.1109/4.261994. |

| [6] |

LIU H C, LEE Z M, WU J T. A 15-b 40-MS/s CMOS pipelined analog-to-digital converter with digital background calibration[J].

IEEE Journal of Solid-State Circuits, 2005, 40(5): 1047-1056.

DOI: 10.1109/JSSC.2005.845986. |

| [7] |

PARK Y, SONG J, CHOI Y, et al. An 11-b 100-MS/s fully dynamic pipelined ADC using a high-linearity dynamic amplifier[J].

IEEE Journal of Solid-State Circuits, 2020, 55(9): 2468-2477.

DOI: 10.1109/JSSC.2020.2987684. |

| [8] |

HUANG H, XU H, ELIES B, et al. A non-interleaved 12-b 330-MS/s pipelined-SAR ADC with PVT-stabilized dynamic amplifier achieving sub-1-dB SNDR variation[J].

IEEE Journal of Solid-State Circuits, 2017, 52(12): 3235-3247.

DOI: 10.1109/JSSC.2017.2732731. |

| [9] |

HERSHBERG B, WEAVER S, SOBUE K, et al. Ring amplifiers for switched capacitor circuits[J].

IEEE Journal of Solid-State Circuits, 2012, 47(12): 2928-2942.

DOI: 10.1109/JSSC.2012.2217865. |

| [10] |

LAGOS J, HERSHBERG B P, MARTENS E, et al. A 1-GS/s, 12-b, single-channel pipelined ADC with dead-zone-degenerated ring amplifiers[J].

IEEE Journal of Solid-State Circuits, 2019, 54(3): 646-658.

DOI: 10.1109/JSSC.2018.2889680. |

| [11] |

LIM Y, FLYNN M P. A 1 mW 71.5 dB SNDR 50 MS/s 13 bit fully differential ring amplifier based SAR-assisted pipeline ADC[J].

IEEE Journal of Solid-State Circuits, 2015, 50(12): 2901-2911.

DOI: 10.1109/JSSC.2015.2463094. |

| [12] |

LIM Y, FLYNN M P. A 100 MS/s, 10.5 bit, 2.46 mW comparator-less pipeline ADC using self-biased ring amplifiers[J].

IEEE Journal of Solid-State Circuits, 2015, 50(10): 2331-2341.

DOI: 10.1109/JSSC.2015.2453332. |

| [13] |

ZHANG X W, QIAN F Y, XI J X, et al. A 16-bit 2.5-MS/s SAR ADC with on-chip foreground calibration[J].

Microelectronics Journal, 2022, 130: 105618.

DOI: 10.1016/j.mejo.2022.105618. |

| [14] |

WU J, LI F, LI W, et al. A 14-bit 200MS/s low-power pipelined flash-SAR ADC[C]//2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS) . Fort Collins, CO: IEEE, 2015: 1-4.

|

| [15] |

HUNG T C, KUO T H. A 75.3-dB SNDR 24-MS/s ring amplifier-based pipelined ADC using averaging correlated level shifting and reference swapping for reducing errors from finite opamp gain and capacitor mismatch[J].

IEEE Journal of Solid-State Circuits, 2019, 54(5): 1425-1435.

DOI: 10.1109/JSSC.2019.2891650. |

2024, Vol. 41

2024, Vol. 41