2. 河源广工大协同创新研究院, 广东 河源 517000

2. Heyuan Synergy Innovation Institute of GDUT, Heyuan 517000 China

新一代的5G无线通信将采用毫米波频段的大规模多输入多输出(Multiple Input Multiple Output, MIMO) 基站,对毫米波芯片提出了很高的要求:高频率、大带宽、高功率密度、低噪声等。作为第3代半导体材料的代表,氮化镓(Gallium Nitride, GaN) 器件的功率密度是砷化镓(Gallium Arsenide, GaAs) 功率密度的10倍以上,特别适合于5G移动通信的应用,具有巨大的发展前景[1]。

低噪声放大器是接收机中重要的模块之一,其噪声和增益决定着接收机系统的整体性能。目前低噪声放大器的设计广泛采用GaAs赝高电子迁移率晶体管(Pseudo-High Electron Mobility Transistor, pHEMT) 器件,但GaAs受制于其较窄的禁带宽度,击穿电场较低,难以满足大功率的应用。GaN除了适合高频大功率的应用,还被证实有可以比拟GaAs的噪声性能[2]。在实际应用中,为了避免GaAs低噪声放大器在接收过高功率的输入信号时而受到损坏,通常需要在信号输入端前使用限幅器[3]等保护电路,从而引入额外的噪声导致接收机系统的灵敏度下降,同时也增加了电路设计难度和生产成本。GaN的高功率特性使设计的电路可以耐受更大的输入功率,避免限幅器等保护电路的使用,实现单片式微波集成电路(Monolithic Microwave Integrated Circuit, MMIC) 的应用,降低设计的复杂度。同时GaN HEMT拥有较高的线性度[4],使设计的低噪声放大器能够有效抑制信号阻塞的发生,减少信号交调的影响,提高接收机系统的动态范围。

目前国际上已有一些性能良好的GaN毫米波低噪声放大器被报道[5-8]。文献[5]提出一款工作频率18~31 GHz、增益达到21 dB以上、NF 小于1.2 dB的GaN低噪声放大器。文献[6]报道了一款工作于35~36.5 GHz的窄带低噪声放大器,其增益大于33 dB,NF小于2.3 dB。当前国内用于5G毫米波通信的GaN低噪声放大器仍在技术突破阶段[9-11],报道相对较少,文献[9]实现的GaN单片低噪声放大器增益达到20 dB以上,NF平均为2 dB。

当前,全球可能优先部署的5G毫米波频段为n257(26.5~29.5 GHz) 和n258 (24.25~27.5 GHz) 频段[12]。本文面向新一代5G毫米波移动通信应用,采用三级级联的共源级拓扑结构设计了一款基于GaN HEMT技术的5G毫米波宽带低噪声放大器MMIC芯片,在24~30 GHz频率范围内实现了低噪声、高增益和高线性度,可以支持n257和n258的毫米波移动通信频段。

1 工艺简介本文设计的单片集成低噪声放大器采用的是法国OMMIC公司的GaN HEMT工艺。该工艺提供耗尽型(Depletion Mode, D-Mode) HEMT,T型栅长为100 nm。其典型的最大振荡频率(fmax) 为160 GHz,增益截止频率(ft) 为110 GHz。该工艺提供两层金属层、镍铬电阻、GaN高值电阻、氮化硅介质和氮化硅、二氧化硅混合介质的MIM电容等器件。该工艺在漏极和源极通过n++ GaN再生层形成非合金欧姆接触,降低了接触电阻[13],从而降低GaN HEMT的导通电阻,有利于低噪声的应用。

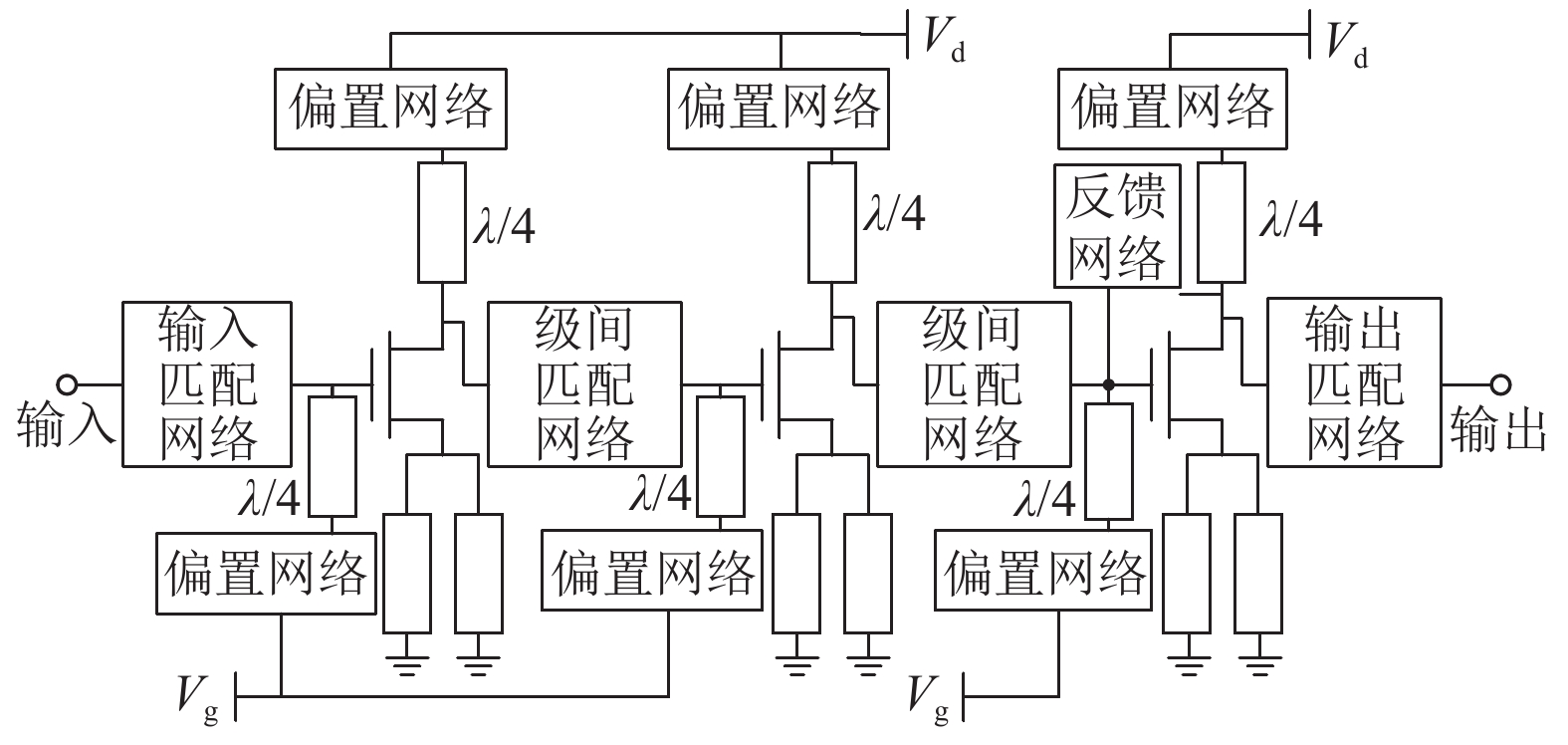

2 LNA电路设计 2.1 整体电路结构本文设计的低噪声放大器电路拓扑结构如图1所示,由GaN HEMT低噪声器件、偏置网络、λ/4传输线、匹配网络和反馈网络组成,其中λ为射频信号的波长。为了达到21 dB小信号增益的设计要求,采用了三级级联放大结构。第1级的设计主要考虑噪声系数,因为其噪声决定了整体电路的噪声水平。第2级主要考虑提高增益,同时兼顾噪声。第3级则重点提高输出功率和线性度,同时继续补足增益。通过对不同尺寸的HEMT管进行扫描仿真后,确定每一级器件的尺寸和直流偏置点,如表1所示,其中Vg为栅端偏置电压,Vd为漏端偏置电压,Ids为漏源静态电流。

|

图 1 低噪声放大器电路拓扑结构框图 Figure 1 Block diagram of low noise amplifier |

| 表 1 各级HEMT管的尺寸及偏置点 Table 1 Size and bias point of each HEMT |

偏置电路的设计影响每一级放大器乃至整体电路的稳定性。如图2所示,本文设计的低噪声放大器偏置网络由两个旁路滤波电容C1、C2和两个小电阻R0、R1构成,并通过λ/4传输线连接GaN HEMT的栅端或漏端。两个旁路电容的大小是不同的,大电容C1用于滤除带外频率较低的射频信号,小电容C2用于滤除工作频带内的射频信号。R0、R1是阻值为10~20 Ω的小电阻,能够进一步确保每一级放大电路在全频带无条件稳定。前两级放大器合并供电,第三级放大器单独供电。

|

图 2 偏置电路结构 Figure 2 Bias circuit structure |

若输入信号的功率太高,有可能会将放大器击穿。在每一级栅端偏置电路中串联一个千欧姆级的大电阻,可以增强放大管对高功率输入信号的承受能力,提高了鲁棒性。

2.3 输入匹配电路的设计低噪声放大器的设计过程中,最关键的就是噪声系数的最优设计,第一级放大器的噪声决定着整体电路的噪声性能,输入匹配的设计尤其重要。放大器的噪声系数可以定义为

| $ {\text{NF}} = {\text{N}}{{\text{F}}_{\min }} + \frac{{{G_{\text{n}}}}}{{{R_{\text{s}}}}}{\left| {{Z_{\text{s}}} - {Z_{{\text{sopt}}}}} \right|^2} $ | (1) |

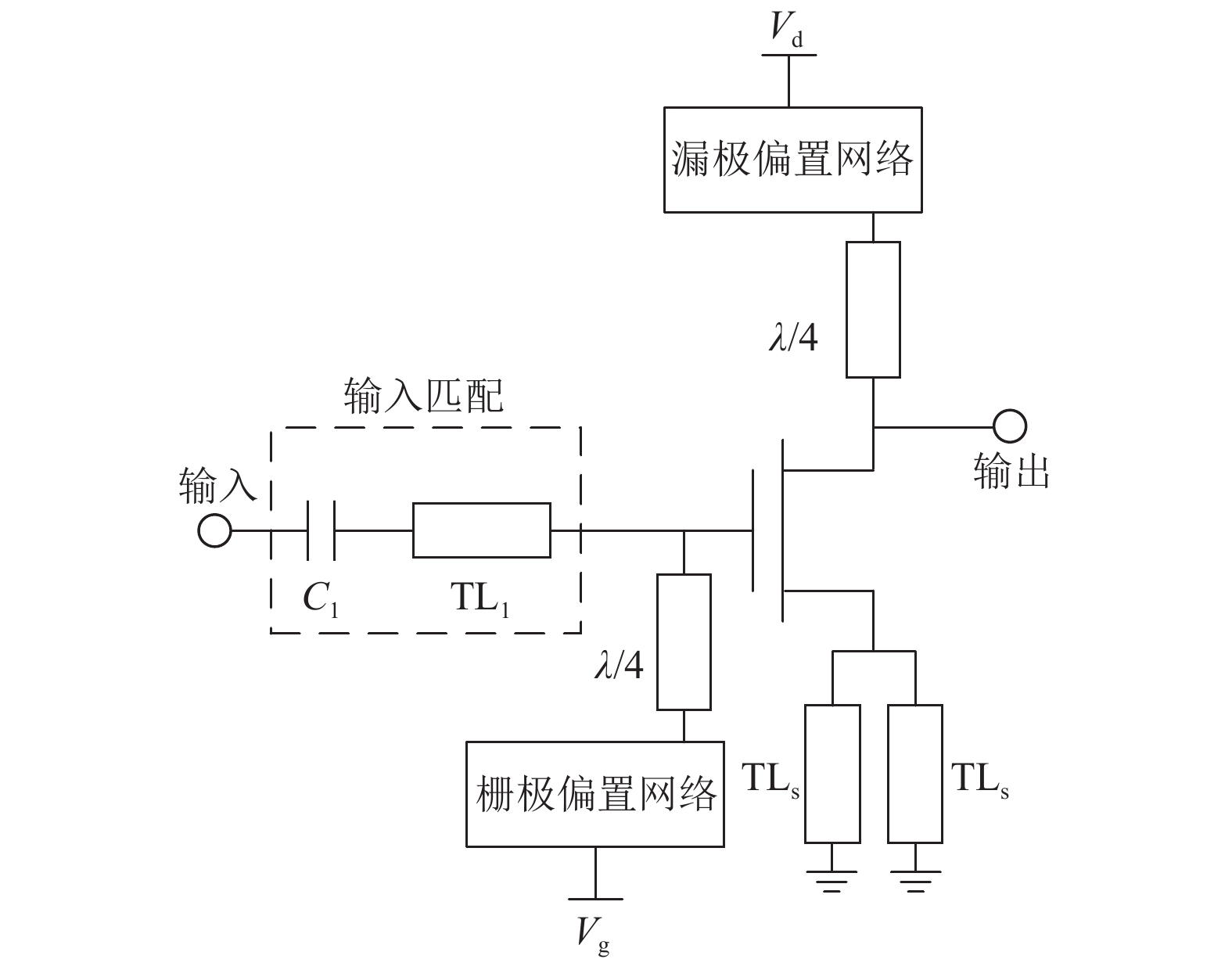

其中:NFmin为最小噪声系数,Gn为放大管的等效噪声电导,Rs为源电阻,Zs为源阻抗,Zsopt为最优噪声源阻抗。由此可以得出,对于给定的器件和源,当Zs=Zsopt时,可以实现最优噪声NF=NFmin。然而这种噪声匹配的方法往往与增益匹配相矛盾,导致输入级放大器的增益过低,由弗里斯(Friis)方程可知[14],后级放大器的噪声得不到有效的抑制。在源极添加电感,实现局部的串联反馈能够解决最优噪声匹配和共轭匹配之间的矛盾。本文设计的输入匹配电路如图3所示,电路设计中需要用到的电感均以微带线替代。栅端和漏端供电通过λ/4传输线与偏置网络相连接,不参与匹配。源端接入两段对称的传输线TLs实现源极电感反馈。假设源端接入的传输线为纯电感Ls,此时放大器的输入阻抗可定义为

|

图 3 带源极反馈电感的输入匹配电路 Figure 3 Input matching circuit with source feedback inductance |

| $ {Z_{{\text{in}}}} = \frac{{{g_{\text{m}}}{L_{\text{s}}}}}{{{C_{{\text{gs}}}}}} + \frac{1}{{{\text{j}}\omega {C_{{\text{gs}}}}}} + {\text{j}}\omega {L_{\text{s}}} $ | (2) |

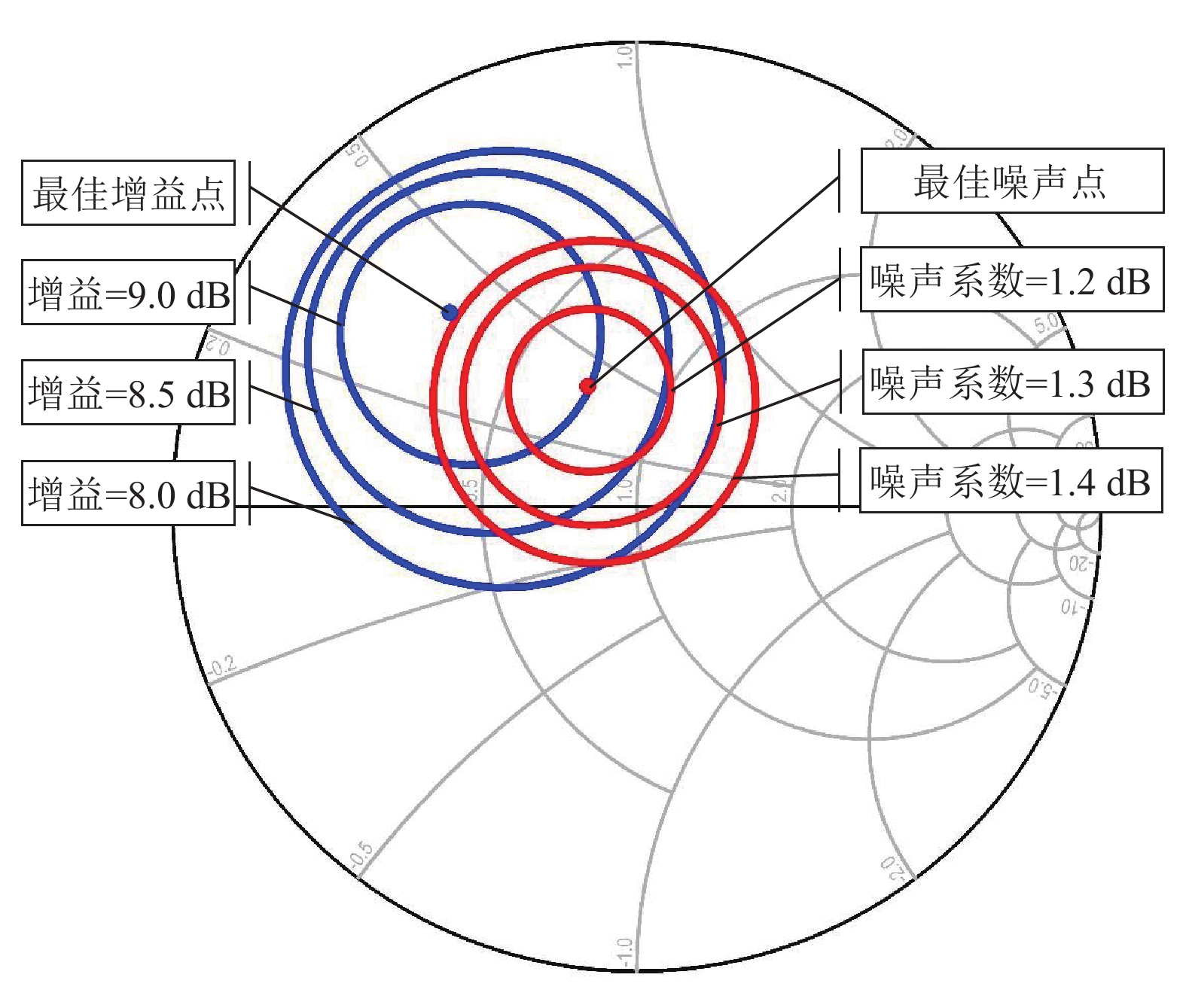

其中:gm为放大管的跨导,Cgs为放大管的栅源寄生电容,Ls为源端加入的电感,该式忽略了输出阻抗和其他寄生参数的影响。源端电感为输入阻抗提供了一个实部阻抗,通过恰当地调整Ls的值,能够使增益和噪声之间得到合适的折衷。通过ADS(Advanced Design System)仿真可以得出输入级在27 GHz时史密斯圆图中的噪声系数常量圆和可用增益常量圆如图4所示,由于源端反馈电感引入的实部阻抗会消耗部分增益,所以可用的增益会低于放大管原有的最大可用增益。同时,源端反馈电感的应用也是保证输入级电路稳定性的重要因素。权衡噪声、增益和输入回波损耗后,在1.2 dB等噪声圆和8.5 dB等增益圆相交部分选取合适的源阻抗点Zs,为了避免引入较大的噪声,输入匹配仅由C1和TL1组成,C1同时用于直流阻隔。

|

图 4 引入源端电感反馈后的可用增益常量圆和噪声系数常量圆 Figure 4 The available gain constant circle and noise constant circle |

第一、二级的级间匹配减少源极电感的大小,提高增益。加入一个到地的小电容,形成三阶的匹配网络,拓展带宽。

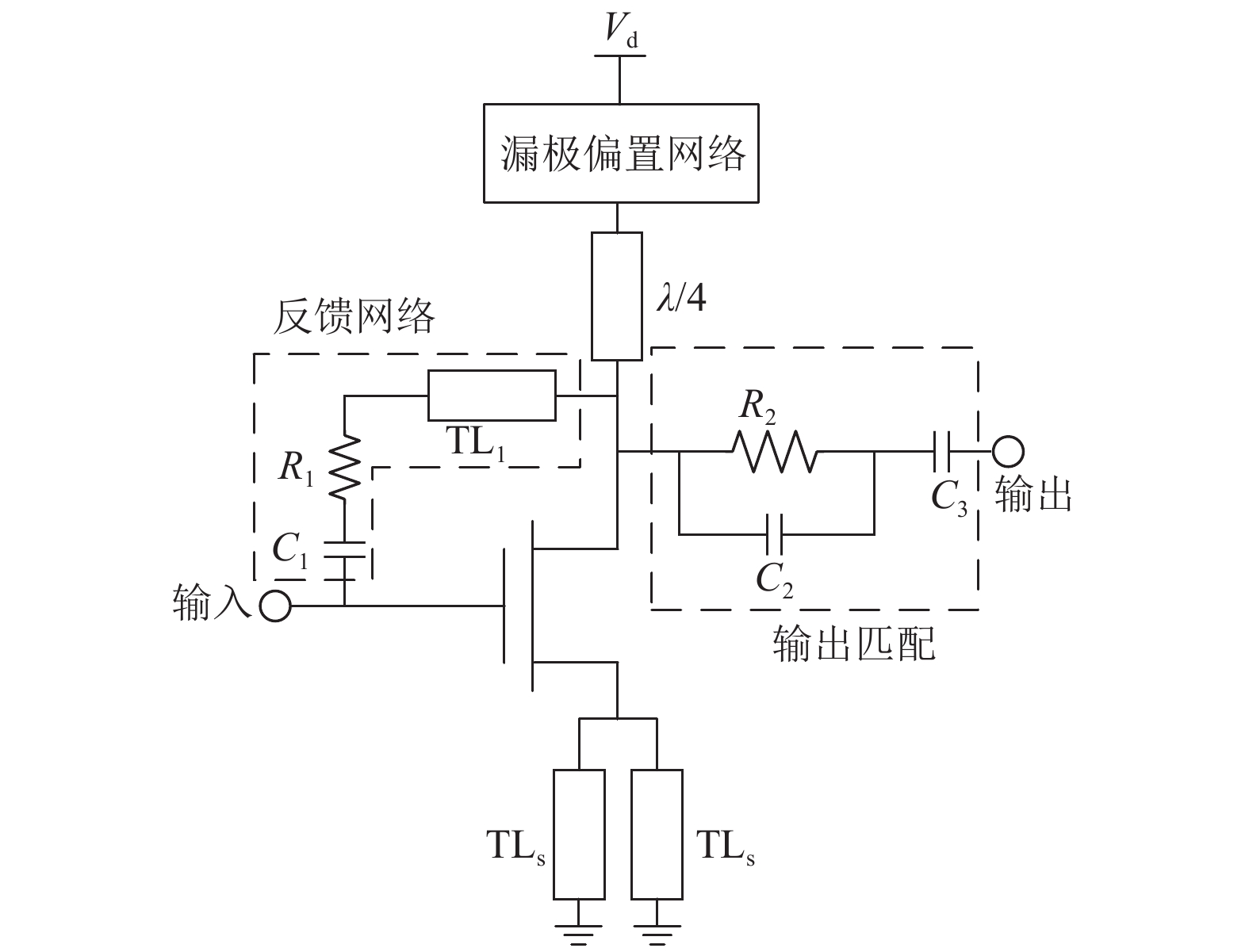

2.4 输出匹配电路的设计完成前两级放大电路基于最优噪声的设计后,第三级输出级的设计主要关注增益和带宽。输出匹配电路结构如图5所示,R2、C2并联后接输出隔直电容C3,微调漏端供电传输线,形成良好匹配,提高带内增益。电阻R2可以调整带内高频和低频的增益,提高增益平坦度,拓展带宽。漏端和栅端通过一个LRC反馈结构连接,电感TL1调节增益的峰值,电阻R1和电容C1可以抑制带增益的峰值,起到平坦增益的效果[15]。通过适当调节TL1、R1和C1,能够有效拓展带宽。

|

图 5 输出匹配电路和RLC反馈电路 Figure 5 Output matching circuit and RLC feedback circuit |

本次设计的单片集成低噪声放大器芯片尺寸为2.0 mm×1.5 mm,采用微探针台、矢量网络分析仪、频谱仪、噪声源等对芯片进行了在片的小信号S参数、噪声系数和输出1 dB功率压缩点的测试,测试平台如图6所示,信号输入、输出端口所用探针为GSG (ground-signal-ground )结构,漏极和栅极的馈电探针为SGGS (signal-ground-ground-signal)结构。所有测试在室温下进行。

|

图 6 氮化镓低噪声放大器芯片照片 Figure 6 Photograph of GaN LNA MMIC |

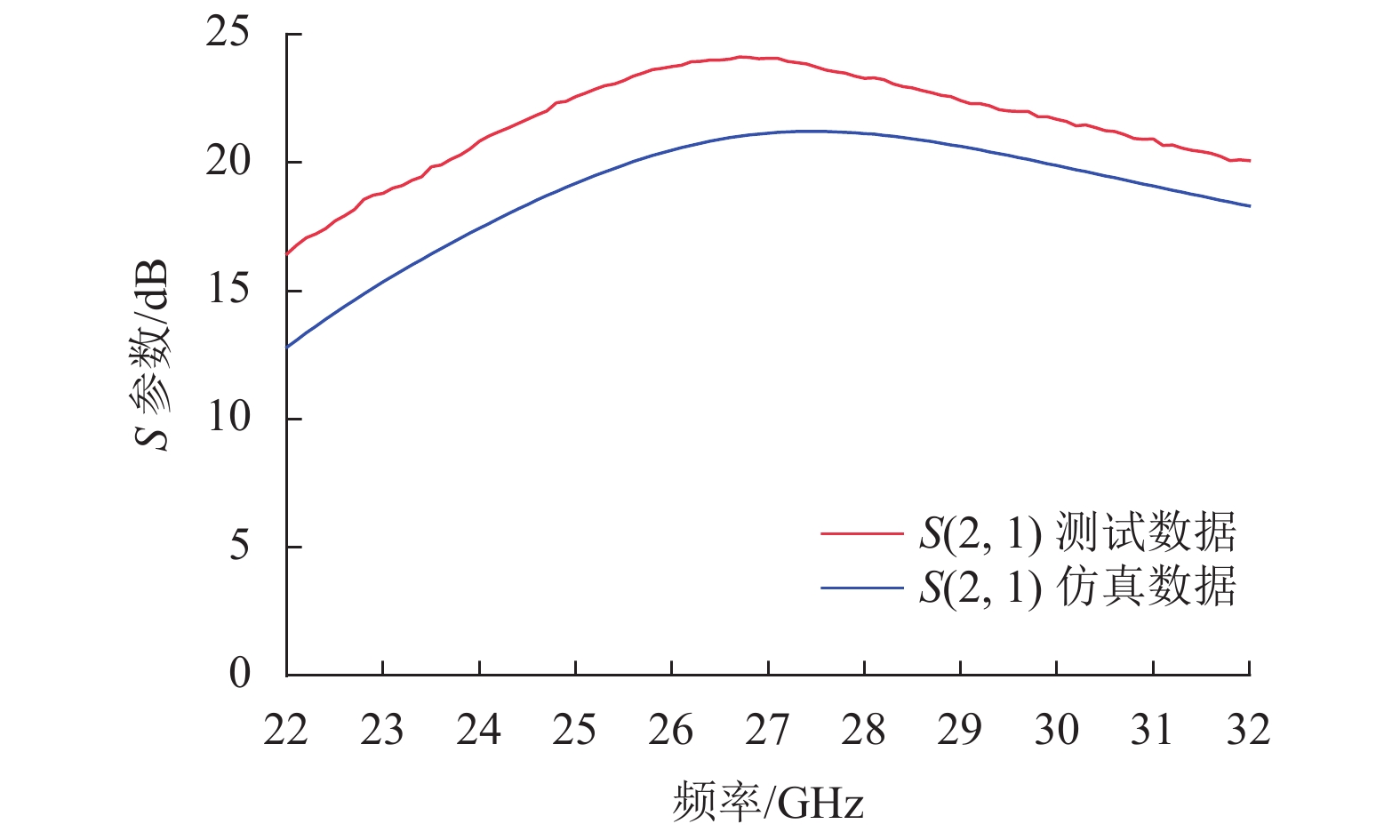

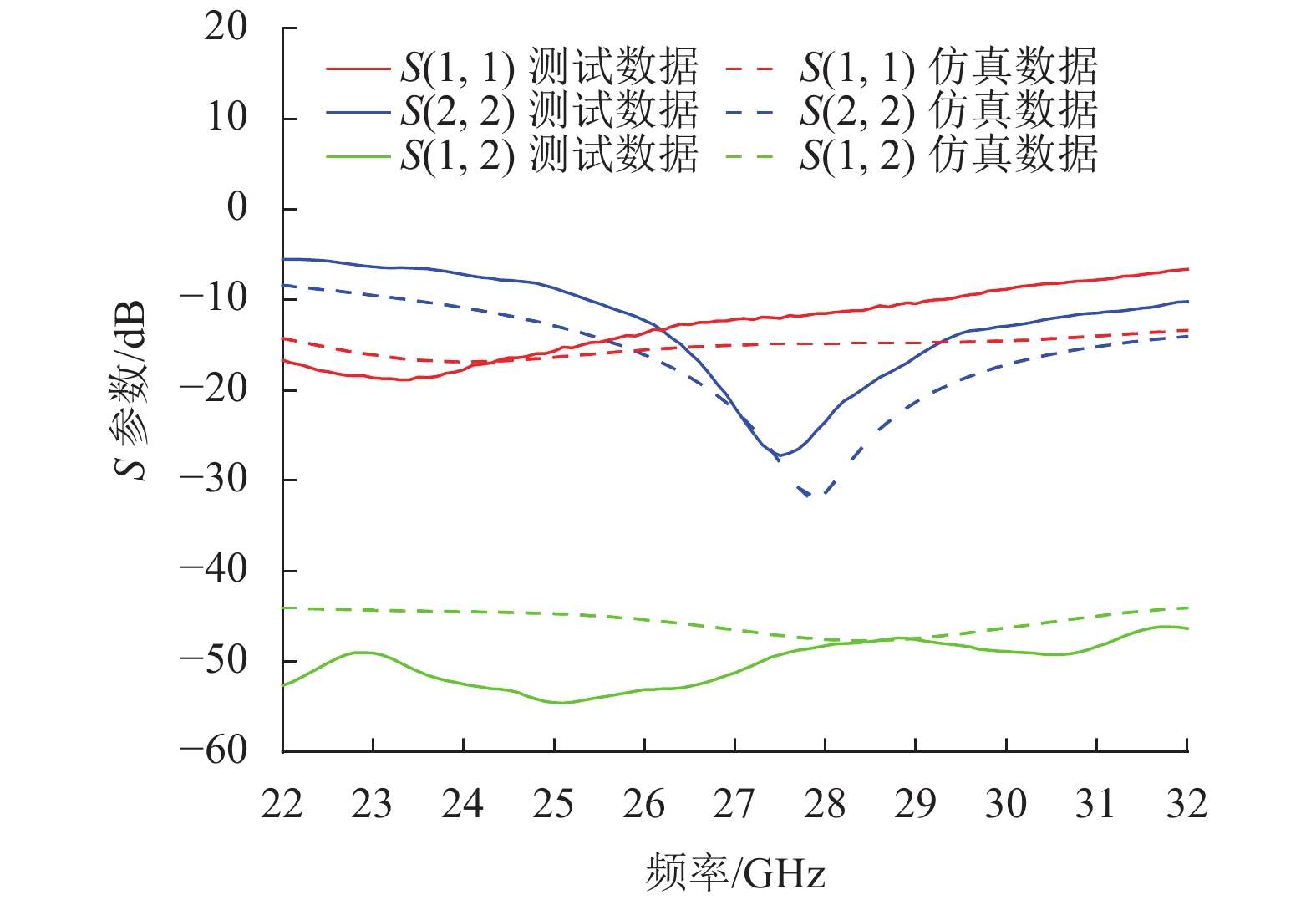

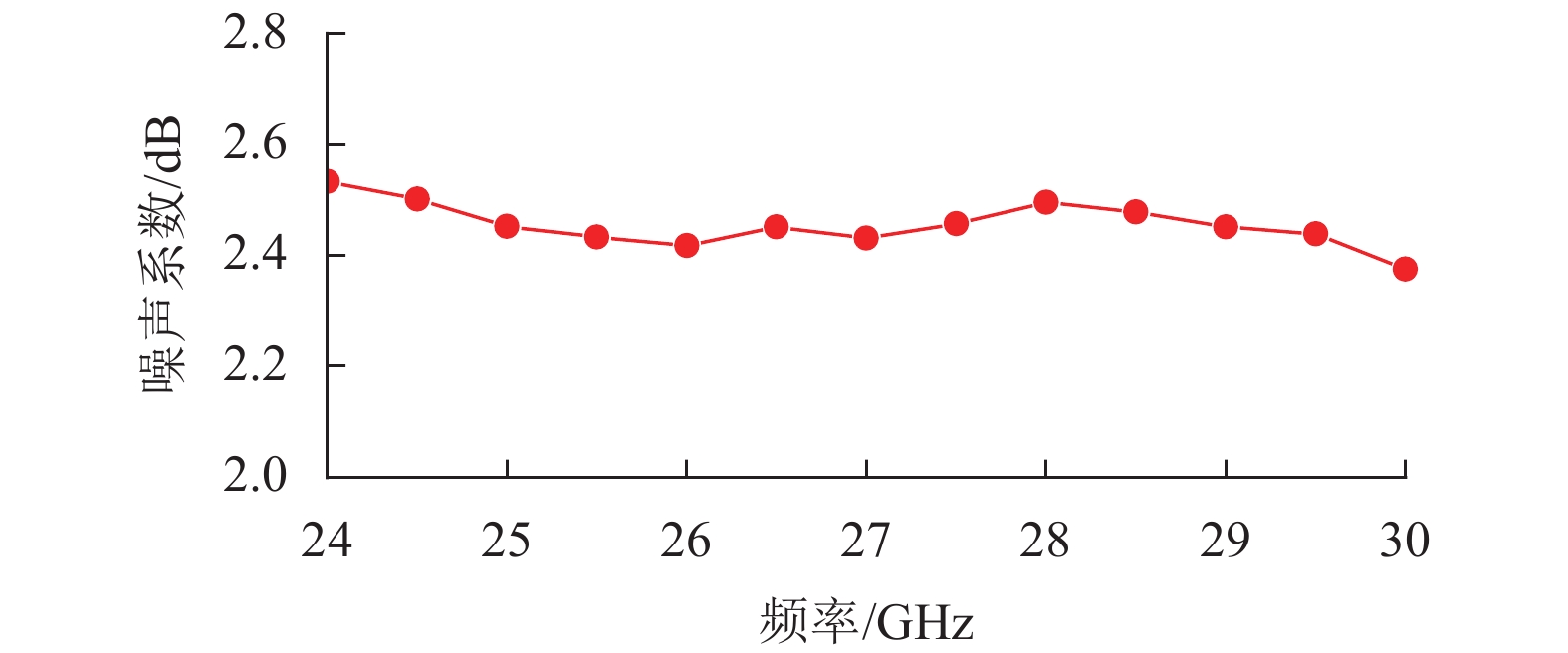

在片测试的小信号线性增益S21如图7所示。在频带24~30 GHz内,S21的测试结果为21.1~24.1 dB (−3 dB带宽)。对比图7中显示的仿真结果,仿真与实测存在差异。由仿真得出,S21在27.5 GHz处最大,为21.2 dB。实测数据最大小信号增益出现在26.7 GHz,为24.1 dB,实测中心频点比仿真往低频偏移0.8 GHz,整体数值比仿真偏高2~3 dB。出现差异的原因考虑是由于仿真模型的精确度不够高,寄生参数的模拟不够精确。如图8所示,该低噪放具有良好的输入、输出回波损耗,而且反向隔离度低于−45 dB。实测的噪声系数如图9所示,在24~30 GHz频率范围内,噪声系数为2.4~2.5 dB左右,其中,在26 GHz频点处,测得最低噪声系数为2.41 dB。图10给出了24~30 GHz频率范围内输出1 dB功率压缩点的测试数据,为14.4~15.8 dBm。全频带内芯片工作稳定,无振荡。在Vd=5 V,Vg=−1.2 V的偏置条件下,该低噪声放大器的直流馈电电流为50 mA,即直流功耗为250 mW。

|

图 7 S21仿真与实测结果 Figure 7 Simulation and measured results of S21 |

|

图 8 S11、S22、S12仿真与测试结果 Figure 8 Simulation and measured results of S11, S22 and S12 |

|

图 9 噪声系数测试结果 Figure 9 Measured results of Noise Figure |

|

图 10 输出1dB功率压缩点测试结果 Figure 10 Measured results of P1dB |

表2列举出本文与其他使用GaN HEMT工艺设计的低噪声放大器之间的性能对比。

| 表 2 性能对比 Table 2 Comparison of the performance |

本文提出了一种工作在24~30 GHz频段的低噪声放大器,采用栅长为100 nm的GaN HEMT工艺设计,芯片尺寸为2.0 mm×1.5 mm,直流功耗为250 mW。在工作频段内,噪声系数在2.4~2.5 dB左右的水平,增益为21.1~24.1 dB,输入回波损耗低于−10 dB,输出1 dB功率压缩点在14.4~15.8 dBm的水平。

| [1] |

TAKAGI K, MATSUSHITA K, KASHIWABARA Y, et al. Developing GaN HEMTs for Ka-band with 20W[C]//2010 IEEE Compound Semiconductor Integrated Circuit Symposium(CSICS) . Monterey, CA: IEEE, 2010: 1-4.

|

| [2] |

陈勇波, 周建军, 徐跃杭, 等. GaN高电子迁移率晶体管高频噪声特性的研究[J].

微波学报, 2011, 27(6): 84-88.

CHEN Y B, ZHOU J J, XU Y H, et al. Research on high frequency noise characters of GaN HEMTs[J]. Journal of Microwaves, 2011, 27(6): 84-88. |

| [3] |

贾晨阳, 彭龙新, 刘昊, 等. 毫米波GaAs单片限幅低噪声放大器[J].

固体电子学研究与进展, 2019, 39(3): 169-173.

JIA C Y, PENG L X, LIU H, et al. Millimeter wave GaAs MMIC limiter low noise amplifier[J]. Research & Progress of SSE, 2019, 39(3): 169-173. DOI: 10.19623/j.cnki.rpsse.2019.03.004. |

| [4] |

KAHIL S A K, LAURENT S, QUÉRÉ R, et al. Linearity characterization of GaN HEMT technologies through innovative on-wafer multi-tone load-pull measurements[C]//2016 11th European Microwave Integrated Circuits Conference(EuMIC) . London, UK: IEEE, 2016: 37-40.

|

| [5] |

ZHANG S, XU J, ZHENG P, et al. An 18–31GHz GaN-based LNA with 0.8dB minimum NF and high robustness[J].

IEEE Microwave and Wireless Components Letters, 2020, 30(9): 896-899.

DOI: 10.1109/LMWC.2020.3011135. |

| [6] |

PACE L, CICCOGNANI W, COLANGELI S, et al. A Ka-band low-noise amplifier for space applications in a 100 nm GaN on Si technology[C]//2019 15th Conference on Ph. D Research in Microelectronics and Electronics(PRIME) . Lausanne, Switzerland: IEEE, 2019: 161-164.

|

| [7] |

KIM S, KIM B, LEE Y, et al. A 28 GHz direct conversion receiver in 65 nm CMOS for 5G mmWave radio[C]//2019 International SoC Design Conference (ISOCC) . Jeju, Korea (South) : IEEE, 2019: 29-30.

|

| [8] |

POURNAMY S, KUMAR N. Design of 60 GHz broadband LNA for 5G cellular using 65 nm CMOS technology[C]//2017 7th International Conference on Communication Systems and Network Technologies (CSNT) . Nagpur, India: 2017: 320-324.

|

| [9] |

吴少兵, 李建平, 李忠辉, 等. Ka波段GaN单片低噪声放大器研制[J].

固体电子学研究与进展, 2018, 38(2): 81-84.

WU S B, LI J P, LI Z H, et al. Fabrication of Ka-band GaN MMIC LNA[J]. Research & Progress of SSE, 2018, 38(2): 81-84. DOI: 10.19623/j.cnki.rpsse.2018.02.001. |

| [10] |

张浩, 王科平, 冷思明. 23~47 GHz宽带BiCMOS低噪声放大器设计[J].

微波学报, 2019, 35(6): 45-48.

ZHANG H, WANG K P, LENG S M. Design of a 23~47 GHz Wideband BiCMOS low noise amplifier[J]. Journal of Microwaves, 2019, 35(6): 45-48. |

| [11] |

王美兰, 陈炎桂, 胡楠. 一种用于5G终端的毫米波收发器前端芯片的研制[J].

微波学报, 2020, 36(4): 86-89.

WANG M L, CHEN Y G, HU N. Research and development of a millimeter wave transceiver front end chip for 5G terminal application[J]. Journal of Microwaves, 2020, 36(4): 86-89. |

| [12] |

张忠皓, 周瑶, 李福昌, 等. 5G毫米波产业发展现状分析[J].

邮电设计技术, 2021(2): 37-41.

ZHANG Z H, ZHOU Y, LI F C, et al. Analysis on the development status of 5G millimeter wave industry[J]. Designing Techniques of Posts and Telecommunications, 2021(2): 37-41. |

| [13] |

FERREYRA R A, SUZUKI A, KAZUMOTO T, et al. n++ GaN regrowth technique using pico-second laser ablation to form non-alloy ohmic contacts[J].

IEEE Electron Device Letters, 2017, 38(8): 1079-1081.

DOI: 10.1109/LED.2017.2721951. |

| [14] |

DARABI H. 射频集成电路及系统设计[M]. 北京: 机械工业出版社, 2019: 93-97.

|

| [15] |

NIKANDISH G, MEDI A. Design and analysis of broadband darlington amplifiers with bandwidth enhancement in GaAs pHEMT technology[J].

IEEE Transactions on Microwave Theory and Techniques, 2014, 62(8): 1705-1715.

DOI: 10.1109/TMTT.2014.2328972. |

2022, Vol. 39

2022, Vol. 39