DMA控制器是SoC的核心组件之一,通过独立地控制内存和外设接口之间的数据传输,能大大减轻CPU的负担,提高数据处理效率[1].因此DMA设计的好坏直接影响SoC芯片的整体性能.与其他集成电路IP设计类似,DMA设计也要考虑DMA IP的复用性,均衡运行速度与电路面积,同时实现与SoC的良好融合.针对这些设计目标,国内外学者进行了深入的研究[2-11].文献[2]设计了可配置多通道的DMA控制器,不过没有考虑到FIFO BUFFER的大小,有可能造成资源的浪费.文献[3]中的设计能够降低CPU负载,提高与外设的数据传输速率,但仅为单通道结构,缺乏通用性.文献[4]为DMA数据传输设计了专用的数据通路,虽然避开了AHB总线的限制,能实现多路数据并行传输,但使得SoC内部总线时序变得复杂,必须考虑总线与专用数据通路对内存读写的仲裁.本文针对导航应用实时性高、数据量大的特点,设计了应用于导航基带SoC的DMA控制器,缩短了芯片的首次定位时间,提高了其整体性能.

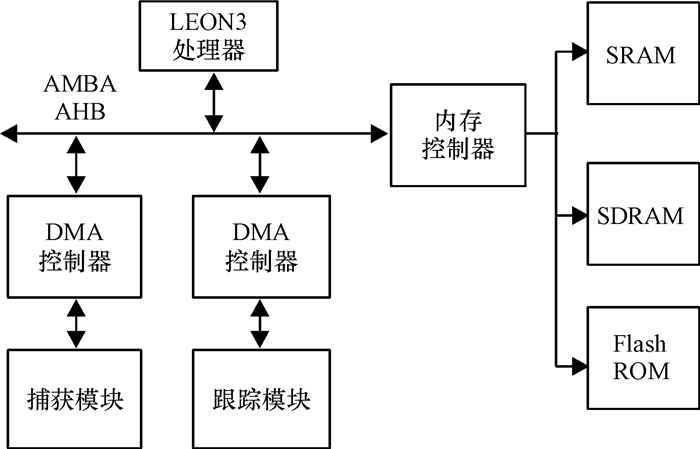

导航基带SoC芯片选用了Aeroflex Gaisler公司的LEON3处理器[12],基于SPARC V8体系结构.片上总线为ARM公司的AMBA 2.0总线[13],保证了数据传输的畅通.为了实现对导航信号的快速捕获和跟踪,芯片内置2路捕获、跟踪模块,利用片上SRAM控制器实现对实时数据的存储.

操作系统选用RTEMS 4.10版,使得系统具有很好的实时性,同时驱动程序编写相对LINUX等其他嵌入式操作系统更为简易.

1 系统架构设计整个系统架构采用了经典的基于AMBA总线的SoC结构,如图 1所示.AMBA 2.0 AHB总线连接片上CPU、内存等各高速设备,通过内存控制器实现对SRAM、SDRAM和FLASH ROM的读写.捕获模块和跟踪模块都连接到DMA模块上,通过DMA模块将产生的数据存储到RAM内.

|

图 1 导航基带SoC结构 Figure 1 Navigation Baseband Architecture |

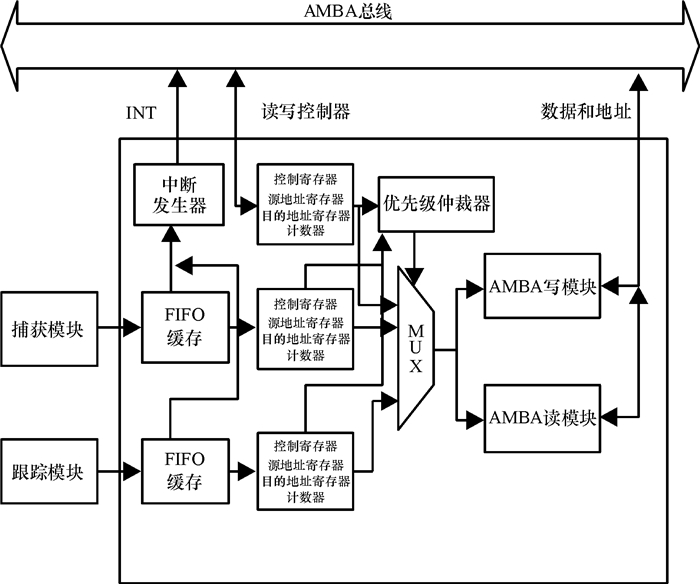

如图 2所示,DMA模块主要由缓存及中断产生逻辑模块、寄存器及仲裁模块、总线读写模块和相应接口组成.捕获和跟踪模块通过并行的数据接口分别接入到DMA模块,产生的数据存储到对应的FIFO缓存中,缓存容量大小固定并连接一个中断产生逻辑电路.当某一缓存满时,产生对应中断请求信号,通过总线请求中断.

|

图 2 DMA控制器结构 Figure 2 DMA Controller Architecture |

内置3组控制寄存器组,每组包括32位的控制寄存器、源地址计数器、目的地址计数器和数据计数器各一个.通过连接到AHB总线和AMBA总线控制器的内存地址映射(Memory Map)实现对寄存器的读写.每组控制寄存器产生的信号首先送固定优先级仲裁器仲裁,仲裁器控制一个复用器输出对应信号.

总线读写模块由独立的AMBA写模块和AMBA读模块组成.通过产生符合总线规范的时序读写数据到相应地址.

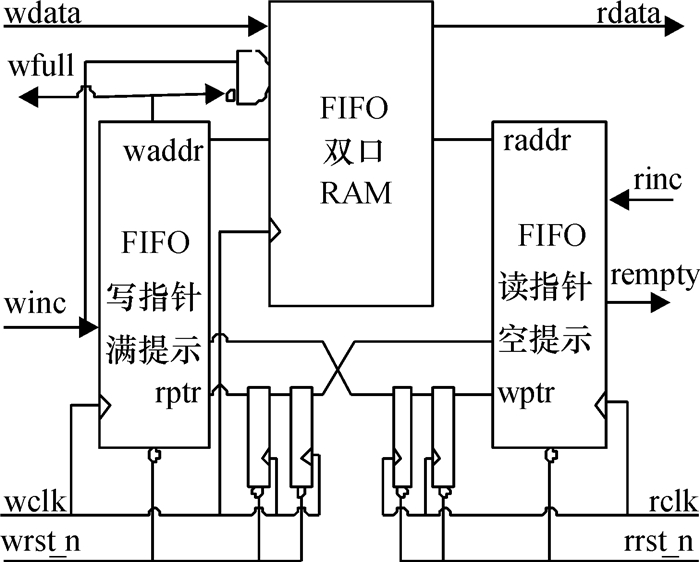

3 FIFO模块设计由于捕获模块和跟踪模块的数据产生率大大慢于总线读写时钟,为了加快DMA的数据传输速率,考虑使用两路异步FIFO作为缓存.

FIFO结构如图 3所示.因为读写采用不同的时钟,故而考虑使用双口RAM作为存储模块.双口RAM的字长和存储深度根据前端RF采样的AD参数决定.为解决跨时钟域数据传输中的亚稳态问题,FIFO读写计数指针都采用格雷码编码,通过多级寄存器传输减少亚稳态产生概率.

|

图 3 FIFO模块结构 Figure 3 FIFO module architecture |

FIFO指针空满比较算法参考了Clifford E. Cummings的论文[14].即构造一个指针宽度为N+1,深度为2N字节的FIFO.读写指针以格雷码表示.前两位均不相同,而后两位LSB相同为满.当指针完全相等时,FIFO为空.

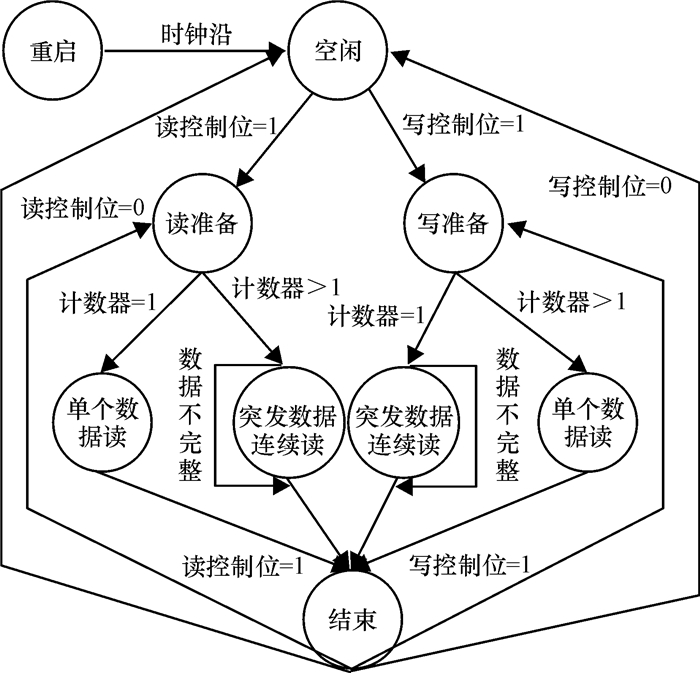

4 DMA控制器的工作流程初始时,总线处于空闲状态,等待DMA传输请求.当控制寄存器的Read或Write位置1时,进入相应的读准备或写准备状态.根据计数器的设置值,DMA再决定采取single或者burst模式读写总线.读写数据处理完毕后进入finish状态,再根据控制寄存器的值决定是否循环读写.工作流程如图 4所示.

|

图 4 FSM图 Figure 4 FSM Diagram |

本节以通过DMA控制器向内存SDRAM中连续写入1 024个数据为例阐述RTEMS下DMA的驱动实现,其他读写操作是相类似的.具体写操作流程如下.

(1) 初始化:RTEMS中对内存控制器及系统其他部分的初始化在此不赘述.通过INIT_DMA函数完成对DMA控制寄存器的初始化:首先在控制寄存器中将写控制位使能置1,其他位置0,然后通过目的地址寄存器设置目的地址,最后在计数器中设置要传输的数据个数:1024.至此初始化工作完成.

(2) 中断处理:DMA BUFFER触发中断后,系统进入中断函数INTER_DMA_START中执行.首先调用Kernel函数kzalloc分配1024 Byte连续内存空间.然后使能DMA控制寄存器的启动位置1,并中断返回主进程.此时总线由DMA接管,DMA开始进入BURST WRITE传输模式,且控制寄存器BUSY位被硬件置1.

(3) 结束处理:数据DMA传输完毕后, 清空数据缓存, 触发数据DMA中断.系统进入中断函数INTER_DMA_DONE中执行.通过检查BUSY位及计数器的值,可以确定是否成功完成所有1 024个数据的传输.至此,一次传输操作结束.

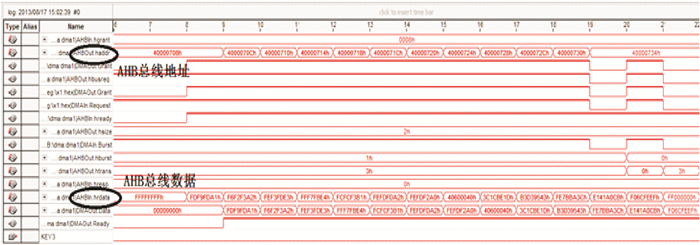

6 DMA IP的软硬件联合验证采用Verilog HDL语言实现该DMA控制器方案的代码[15],使用Altera的QuartusⅡ进行综合调试,将所有模块综合映射到Altera公司的Cyclone4 EP4C115F29C7上,得到正确的门级电路网表,综合后共消耗6 348个LE.在RTEMS操作系统下通过软件中断的方式模拟数据传输.图 5是采用Altera的Signal Tap技术观察到的fpga上DMA对总线的实时读burst模式波形,可以看到DMA模块成功地完成了burst模式下一组数据的读取.

|

图 5 读burst模式验证波形 Figure 5 Read burst module verification waveform |

为了考察DMA方案所带来的影响, 本文研究DMA与非DMA(中断FIFO方式)两种情况下,基带SoC进行首次定位所需要的时间TTFF.通过不同信噪比接收信号和动态条件下进行测试, 得出数据和结论.

7.1 测试设计导航基带SoC首次定位时间TTFF又称冷启动时间.冷启动时系统在没有任何历史信息的条件下上电开机,然后尝试定位并锁定卫星,由于没有先前信息,这将花去很长的时间.系统采用类似于轮询的方法,从所有的卫星中锁定信号.

从上电开机到得出定位数据,系统执行4个步骤:初始化操作系统—捕获—跟踪—位置解算,同时与用户进行人机交互.处理器在这4个步骤中主要负责初始化操作系统、位置解算和人机交互任务.DMA控制器可以代替处理器,负责把捕获、跟踪生成的数据从FIFO缓存存入内存内,供解算处理.进而处理器可以专注于位置解算和人机交互任务,从而缩短了首次定位时间TTFF.

为了全面考察系统性能,测试实验选取3种不同条件下的中频GPS信号作为信号源.第1种条件下GPS信号信噪比为42 dB/Hz,系统加速为0 g.第2种条件信噪比为42 dB/Hz,系统加速为20 g.第3种条件信噪比为34 dB/Hz,系统加速为0 g.系统从时刻T1上电启动,并进行计时,在时刻T2解算出定位数据后停止计时,则首次定位时间TTFF=解算出定位数据时刻T2-系统上电启动时刻T1.每种条件下,进行5次重复测试,TTFF通过求取平均值得到,因此数据具有较好的可靠性.测试结果如表 1所示.

| 表 1 首次定位时间TTFF统计 Table 1 TTFF statistics at first positioning time |

由表 1可以看到:

(1) 第1种条件下,系统处于低动态较高信噪比的环境,因而DMA与非DMA两种方式下系统TTFF都相对较短.而DMA方式比非DMA方式用时间少了1.1 s.可见,DMA将CPU从数据搬运任务中解放了出来,使其拥有更多的空闲时间进行其他任务,进而缩短了首次定位时间.

(2) 第2种条件下,系统处于高动态的极端环境,捕获、跟踪导航信号难度大大增加.由于重捕获、跟踪失锁,TTFF明显增加.DMA方式比非DMA方式用时间少了2.1 s.相比第一种条件,采用DMA方式对缩短TTFF效果更明显.

(3) 第3种条件下,系统处于较低信噪比的弱信号环境,同样使捕获、跟踪导航信号难度增加,TTFF在非DMA方式下为28.6 s,DMA方式下为26.8 s,分别比条件一的26.4 s与25.8 s长.由表 1可见DMA方式比非DMA方式用时间少了1.8 s.采用DMA方式对缩短TTFF也有较明显的效果.

测试表明:DMA控制器能有效减轻导航基带SoC中CPU的负载,缩短系统首次定位时间.

8 结语SoC技术近年来发展迅速,代表了未来IC发展的趋势.而GPS基带SoC作为一种由多个IP组成的复杂系统,单个IP组件的设计只有充分考虑整体系统软硬的融合才能发挥SoC的最优性能.本文的DMA IP从系统整体着眼,硬件上运用FIFO BUFFER和中断机制等实现了与捕获、跟踪模块的良好结合,软件上通过寄存器组位的设计使得RTEMS实时操作系统下的驱动设计方便实现.通过FPGA的实验验证表明,本设计能够实现基于AMBA总线的数据读写控制,减轻了CPU负担.

| [1] | 白中英. 计算机组成原理[M]. 北京: 科学出版社, 2005. |

| [2] |

陈双燕, 王东辉, 侯朝焕. 基于SystemC的可配置多通道DMA控制器的设计与实现[J].

微电子学与计算机, 2007, 24(5): 48-51.

CHEN S Y, WANG D H, HOU C H. Design and implementation of a configurable multi-channel dma controller based on SystemC[J]. Microelectronics & Computer, 2007, 24(5): 48-51. |

| [3] |

史斌, 丁志刚, 张伟宏. 基于PXA3xx处理器的NAND闪存DMA方案[J].

计算机应用, 2009, 29(8): 2136-2138.

SHI B, DING Z G, ZHANG W H. NAND flash DMA application based on PXA3xx processor[J]. Journal of Computer Applications, 2009, 29(8): 2136-2138. |

| [4] |

张路煜, 李丽, 潘红兵, 等. SoC系统中多端口DMA控制器的设计[J].

电子测量技术, 2014, 37(9): 32-36.

ZHANG L Y, LI L, PAN H B, et al. Design of a multi-interface DMA controller based on SoC[J]. Electronic Measurement Technology, 2014, 37(9): 32-36. |

| [5] | 孙钟秀, 费翔林, 骆斌. 操作系统教程[M]. 3版. 北京: 高等教育出版社, 2003. |

| [6] |

谢勇, 申敏, 郑建宏. AMBA总线结构中高性能DMA控制器的硬件实现[J].

重庆工学院学报(计算机与自动化版), 2006, 20(8): 72-74.

XIE Y, SHEN M, ZHENG J H. The hardware application of high performance DMA controller in AMBA bus architecture[J]. Journal of Chongqing Institute of Technology: Computer and Automation Column, 2006, 20(8): 72-74. |

| [7] | 郝军. DMA控制器的仿真与验证[D]. 西安: 西安电子科技大学微电子学院, 2013. |

| [8] | 耿剑波. 基于AMBA总线的DMA模块的设计与验证[D]. 西安: 西安电子科技大学微电子学院, 2013. |

| [9] | 赵强. 基于AHB总线协议的DMA控制器设计[D]. 西安: 西安电子科技大学微电子学院, 2014. |

| [10] | 魏芸. 基于FPGA的PCIe总线DMA平台设计[D]. 武汉: 武汉理工大学信息工程学院, 2013. |

| [11] |

李木国, 黄影, 刘于之. 基于FPGA的PCIe总线接口的DMA传输设计[J].

计算机测量与控制, 2013, 21(1): 46-49.

LI M G, HUANG Y, LIU Y Z. The Design of DMA for PCIe bus based on FPGA[J]. Computer Measurement & Control, 2013, 21(1): 46-49. |

| [12] | AEROFLEX GAISLER. GRLIB IP library user's manual[EB/OL]. (2013-07-13)[2015-4-22]. http://www.gaisler.com/index.php/products/ipcores/soclibrary. |

| [13] | ARM Ltd. AMBA bus specification[EB/OL]. (2009-07-01)[2015-4-22]. http://download.csdn.net/download/LanYieL/1454221. |

| [14] | CLIFFORD E. Cummings. Simulation and synthesis techniques for asynchronous FIFO design[EB/OL]. (2011-04-12)[2015-4-22]. http://download.csdn.net/detail/zhusichao/3185455. |

| [15] | 夏宇闻. Verilog数字系统设计教程[M]. 2版. 北京: 北京航空航天大学出版社, 2008. |

2016, Vol. 33

2016, Vol. 33