LTE(Long Term Evolution, 长期演进)是移动通信技术与宽带网络相融合的技术潮流, 它是3G的演进, 改进和增强了3G的空中接口技术, 因此又被称作3.9G.现阶段, TD-LTE已经纳入运营商的计划中, 作为未来移动通信发展的领先技术, 研究LTE的技术理论及实现有重大意义[1-3].

在TD-LTE中, 物理上行控制信道(Physical Uplink Control Channel, PUCCH)的作用是发送上行控制信息, 但由于受到无线信道的多径时延、多普勒效应等的影响, 基站接收端很难准确恢复接收到的信号, 而PUCCH的解调参考信号(Demodulation Reference Signal, DMRS)就能很好地帮助基站接收端解决这一问题[1].解调参考信号与PUCCH的控制信息一起进行传输, 在基站接收端侧, 通过对解调参考信号进行检测, 可以得到信道状态估计矩阵, 从而能够准确恢复出控制信息.

关于LTE上行链路参考信号的研究与实现, 已有不少成果.文献[4]对LTE中上行链路中参考信号(解调参考信号和sounding参考信号)的生成、特性、分类及作用进行分析.文献[5]介绍了探测参考信号SRS生成涉及的各个公式, 给出了程序实现的设计流程, 并用DSP具体实现生成SRS信号.文献[6]完成了LTE上行链路Sounding参考信号的设计并基于PicoArray芯片完成Sounding参考信号实现模块的代码编写测试.文献[7]对LTE上行链路中参考信号接收端进行系统分析, 与算法设计并对LTE上行链路参考信号基站侧进行DSP实现、性能测试与验证.

现有文献都是采用DSP实现参考信号的生成.虽然DSP编程速度快且方便, 但相对FPGA技术来说会产生较大的时延.而LTE系统对时延要求较高, 很难满足系统要求.本文则基于现场可编程逻辑门阵列(FPGA)技术来实现LTE的PUCCH的解调参考信号的生成, 该设计方案可以实现时隙与时隙之间跳频的解调参考信号的生成, 具有性能高时延低的特点, 能很好地达到LTE 3GPP的R9规范中预期的要求.

1 PUCCH的解调参考信号解调参考信号的生成表达式如下:

| $ \begin{gathered} {r^{{\text{PUCCH}}}}\left( {m\prime {N_{{\text{RS}}}}^{{\text{PUCCH}}}{M_{{\text{sc}}}}^{{\text{RS}}} + m{M_{{\text{sc}}}}^{{\text{RS}}} + n} \right) = \hfill \\ \bar w\left( m \right)z\left( m \right){\text{ }}{r_{u, v}}^{(\alpha )}\left( n \right), \hfill \\ \end{gathered} $ | (1) |

其中, m=0, …, NRSPUCCH-1, n=0, …, MscRS-1, m′=0, 1.w(m)是扩频正交序列.对于PUCCH的格式2a/2b, 当m =1, 等于调制符号d (10), 其他情形时, z(m)=1.

参考信号序列ru, v(α)(n)的α值随着不同的PUCCH格式的控制信息而不同.

对于PUCCH的格式1/1a/1b,

| $ \alpha \left( {{n_s},l} \right) = \frac{{2{\rm{\pi }}{n_{cs}}\left( {{n_s},l} \right)}}{{{N_{{\rm{sc}}}}^{{\rm{RB}}}}}, $ | (2) |

常规CP,

| $ \begin{gathered} {n_{{\text{cs}}}}\left( {{n_s}, l} \right) = \hfill \\ \left[{{n_{{\text{cs}}}}^{{\text{cell}}}\left( {{n_s}, l} \right) + \left( {n\prime \left( {{n_s}} \right)\cdot{\Delta _{{\text{shift}}}}^{{\text{PUCCH}}} + \left( {{n_{{\text{oc}}}}\left( {{n_s}} \right){\text{mod}}{\Delta _{{\text{shift}}}}^{{\text{PUCCH}}}} \right)} \right){\text{mod}}N\prime } \right]{\text{mod}}{N_{{\text{sc}}}}^{{\text{RB}}}. \hfill \\ \end{gathered} $ | (3) |

扩展CP,

| $ \begin{gathered} {n_{{\text{cs}}}}\left( {{n_s}, l} \right) = \hfill \\ \left[{{n_{{\text{cs}}}}^{{\text{cell}}}\left( {{n_s}, l} \right) + \left( {n\prime \left( {{n_s}} \right){\Delta _{{\text{shift}}}}^{{\text{PUCCH}}} + \frac{{{n_{{\text{oc}}}}\left( {{n_s}} \right)}}{2}} \right){\text{mod}}N\prime } \right]{\text{mod}}{N_{{\text{sc}}}}^{{\text{RB}}}. \hfill \\ \end{gathered} $ | (4) |

对于PUCCH格式2/2a/2b, 传输的资源由资源指示确定, 循环移位也是由式(2)得到.以上公式中的参数的详细说明可以参考文献[8-10].

2 解调参考信号生成的FPGA实现 2.1 硬件芯片简介考虑到DMRS生成涉及的参数较多以及算法较为复杂, 本设计所选芯片为Cyclone Ⅲ.Cyclone Ⅲ FPGA[11-12]具有显著的低功耗、高性能特点, 含有5K至120K逻辑单元(LE), 288个数字信号处理(DSP)乘法器, 存储器达到4 Mbits.它的低功耗、高密度和充足的DSP功能使设计人员可以在大量新的无线应用中使用低成本系列产品, 例如无线微基站的数字IF和基带功能等.

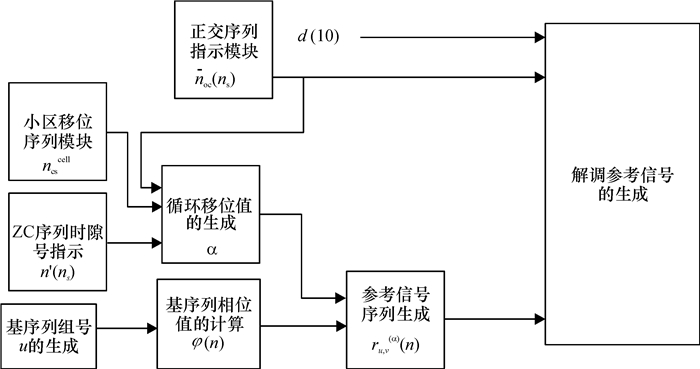

2.2 设计流程本文上一节从理论上分析了解调参考信号的生成过程, 本节结合FPGA来设计DMRS的生成.根据FPGA设计模块化的特点[13-14], 本文所提出的实现方案将DMRS的生成分成8个模块来进行实现, 如图 1所示.

|

图 1 解调参考信号生成的各模块关系图 Figure 1 The module relationship chart of the demodulation reference signal generation |

在图 1中, 基序列组号模块得到的u值输入到基序列相位值计算模块, 得到对应的12个相位值, 小区移位序列模块输出的小区循环移位值ncscell、ZC序列时隙号指示模块输出时隙指示n′(ns)与正交序列指示模块输出noc(ns)一同输入到循环移位值的生成模块, 得到α, α与φ(n)共同确定参考信号序列, 参考信号序列与调制符号d (10)、正交扩频序列一同输入到解调参考信号生成模块, 得到解调参考信号序列.

为了保持解调参考信号与控制信息进行资源映射时的同步性, 需要设置开关功能的参数来指示DMRS模块工作.当PUCCH需要传输控制信息的时候, 控制信息的基带处理过程需通过开关功能参数指示给解调参考信号模块.这时候, 解调参考信号模块开始工作, 生成DMRS.DMRS的信号的个数是与PUCCH格式相关的, 不同的PUCCH格式, 在一个时隙中所占的符号个数是不一样的.在顶层模块中考虑这两方面的控制参数进行设计.

DMRS的设计根据前面的算法应将DMRS生成分成3大部分, 分别是指示符号d (10)、正交扩频序列和参考信号序列.指示符号d (10)直接由PUCCH控制信息模块直接传送得到, 无需进行计算, 只需预留输入端口.正交扩频序列根据不同的CP的类型来取对应矩阵, 可以采用查表方法, 把矩阵存在ROM或者RAM中.

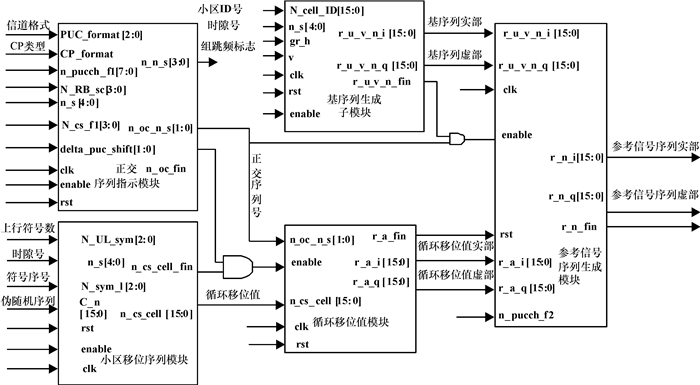

参考信号序列在整个设计中是重点.参考信号序列是组成解调参考信号的主要部分, 并且其由于涉及到的参数较多, 设计实现时会比较复杂, 所以本设计中要把循环移位序列的生成分割成5个模块, 参考信号序列是由组跳频指示u、基序列、循环移位值以及关于当前发送帧的子帧号和时隙号ns等参数计算得到.其中参考信号序列需要的正交指示参数noc(ns)是从正交序列模块直接输入得到的.图 2是参考信号序列所涉及的基序列生成、正交序列指示、小区移位序列、循环移位值等模块的设计图.

|

图 2 参考信号序列相关模块的设计图 Figure 2 The design chart of the related modules of the reference signal sequence |

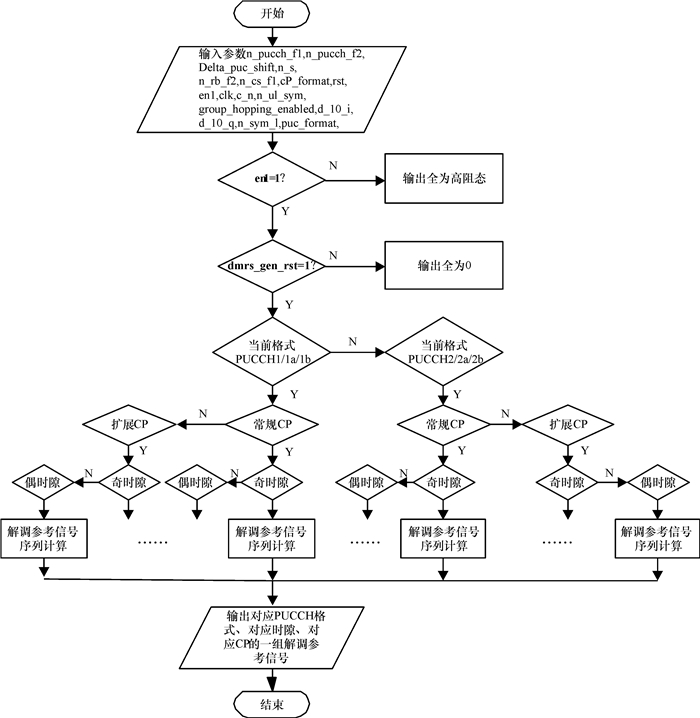

根据上述的设计流程, 本文给出的DMRS生成的实现步骤分为3大步骤, 如图 3所示.

|

图 3 DMRS生成的总体设计流程图 Figure 3 The overall design flow chart of the generation of DMRS |

(1) PUCCH有控制信息需要进行基带处理时, DMRS使能端en1为高电平[15], 解调参考信号模块开始工作, 复位信号为低电平时, 输出全为0;高电平时, 开始正常工作.

(2) 判断当前的控制信息的类型, 分为PUCCH 1/1a/1b和PUCCH2/2a/2b, 接下来判断CP类型, 分常规CP和扩展CP, 最后是判断奇偶时隙, 这些信息的判断, 主要是与后面的解调参考信号的生成的算法相关的.

(3) 根据2.2节的设计思路, 完成解调参考信号计算模块, 输出对应的解调参考信号序列组.

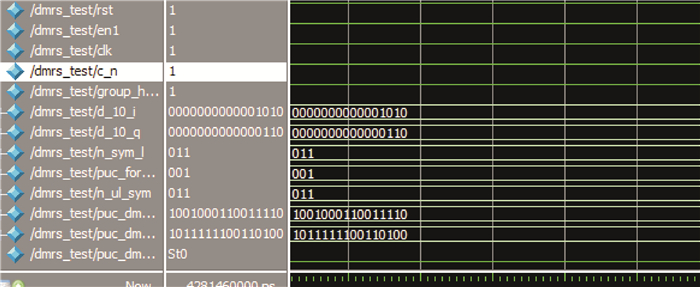

2.4 仿真结果本文采用的仿真平台为Modelsim软件.仿真测试时钟的频率为100 MHz[16], 在测试文件中预先设定好初始值.由于解调参考信号是一个复数序列, 在仿真中得到的仿真值是用实部和虚部来表示的.设计中, puc_dmrs_i为复数的实部, puc_dmrs_q为复数的虚部.

在图 4中, 得到仿真结果puc_dmrs_i为100100011001110, puc_dmrs_q为1011111100110100, 实部跟虚部所表示的数为小数, 它的最高位权为2-1, 次高位为2-2, 依次类推到最低位.实部跟虚部的平方和约为0.91, 其与理论值1相比, 误差相对来说有点大, 经过分析, 误差主要出现在模块与模块的弧度值与正余弦值的转换中, 需要采用CORDIC算法来提高精度.经过多次的调试, 仿真结果误差在可控范围内, 表明本设计能够实现与理论计算得到的结果相符合, 可以达到协议规定的要求.

|

图 4 解调参考信号的功能仿真图 Figure 4 The functional simulation chart of the demodulation reference signal |

本文针对LTE物理层上行控制信道的解调参考信号的生成进行FPGA设计.该设计方案在FPGA平台上的实现, 能为解调参考信号的进一步应用做好准备工作.本文提出的设计是根据3GPP物理层协议规范R9版本有关上行控制信道的解调参考信号的内容进行的, 仿真结果证实了该基于FPGA的设计实现方案能够很好地满足上述有关协议规范的要求.

| [1] |

赵训威, 林辉, 张明, 等.

3GPP长期演进(LTE)系统架构与技术规范[M]. 北京: 人民邮电出版社, 2010: 1-27.

|

| [2] |

林艳芳. TD-LTE关键技术及发展[J].

数字通信, 2011, 38(1): 35-37, 47.

Lin Y F. Key technology and development in TD-LTE[J]. Digital Communication, 2011, 38(1): 35-37, 47. |

| [3] |

陈超. LTE关键技术与标准演进分析[J].

无线互联科技, 2013(2): 85-86.

Chen C. Key technologies and Standards Evolution Analysis in LTE[J]. wuxian hulian keji, 2013(2): 85-86. |

| [4] |

李剑, 陈发堂. LTE中上行链路参考信号研究[J].

电子测试, 2009(5): 35-38.

Li J, Chen F T. Research on LTE's reference signals of uplink[J]. Electronic Test, 2009(5): 35-38. |

| [5] |

刘文文, 李校林, 李小文. TD-LTE系统中探测参考信号的DSP实现[J].

电子技术应用, 2011, 37(12): 53-55, 59.

Liu W W, Li X L, Li X W. DSP realization of sounding reference signal in TD-LTE system[J]. Application of Electronic Technique, 2011, 37(12): 53-55, 59. DOI: 10.3969/j.issn.0258-7998.2011.12.020. |

| [6] |

吕倩. LTE中Sounding参考信号设计与实现[D]. 北京邮电大学信息与通信工程学院, 2011.

|

| [7] |

邵道炯. TD-LTE上行链路中参考信号技术的研究与DSP实现[D]. 电子科技大学通信与信息工程学院, 2011.

|

| [8] |

王映民, 孙韶辉, 王可, 等.

TD-LTE技术原理与系统设计[M]. 北京: 人民邮电出版社, 2010: 105-145.

|

| [9] |

崔明. LTE-Advanced中参考信号的设计研究[D]. 南京邮电大学电子科学与工程学院, 2011.

|

| [10] |

张志林.

3GPP LTE物理层和空中接口技术[M]. 北京: 电子工业出版社, 2011: 89-125.

|

| [11] |

王诚, 吴继华, 范丽珍, 等.

Altera FPGA/CPLD设计(基础篇)[M]. 2版. 北京: 人民邮电出版社, 2011: 1-105.

|

| [12] |

吴继华, 王诚, 蔡海宁, 等.

Altera FPGA/CPLD设计(高级篇)[M]. 2版. 北京: 人民邮电出版社, 2011: 285-327.

|

| [13] |

杜玉晓, 张浩腾, 陈汶育, 等. 基于FPGA的高速多通道实时同步采集传输系统的设计与实现[J].

广东工业大学学报, 2013, 30(3): 37-44.

Du Y X, Zhang H T, Chen W Y, et al. The design and implementation of high-speed multi-channel and real-time synchronous acquisition transmission system based on FPGA[J]. Journal of Guangdong University of Technology, 2013, 30(3): 37-44. |

| [14] |

罗珍, 刘海林. 用二维坐标下降法实现x=b/a的FPGA设计[J].

广东工业大学学报, 2011, 28(1): 32-37.

Luo Z, Liu H L. FPGA design of the dichotomous coordinate descent algorithm for complex divider problems[J]. Journal of Guangdong University of Technology, 2011, 28(1): 32-37. |

| [15] |

夏宇闻.

Verilog数字系统设计教程[M]. 2版. 北京: 北京航空航天大学出版社, 2008: 68-125.

|

| [16] |

Janick Bergeron. Writing Testbenches Functionnal Verification of HDL Models[M]. Springer: Kluwer Academic Publishers, 2003: 223-256.

|

2015, Vol. 32

2015, Vol. 32