CMOS图像传感器是近些年发展较快的一种新型图像传感器.与CCD相比,CMOS图像传感器具有体积小、成本低、重量轻、功耗低、编程方便、易于控制等优点.CMOS图像传感器已经广泛应用于各种通用图像采集系统中.随着CMOS集成电路设计和工艺的不断进步和完善,CMOS正在朝着高分辨率,高灵敏度,低噪声,大动态范围,高智能化的方向不断发展[1-5].采用FPGA作为主控芯片,整个系统具有设计方便、仿真简单和传送高速数据时有更小的高频噪声干扰等优势[6-8].因此,提出基于FPGA的CMOS图像传感器实时采集和显示的设计方案, 为图像检测系统项目的研究提供了有价值的设计参考.

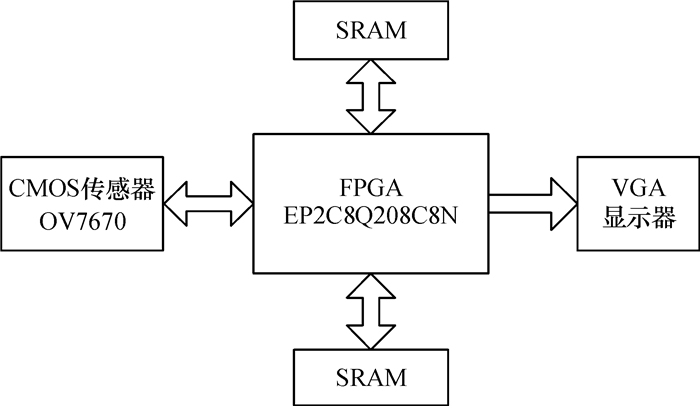

1 系统结构系统整体结构包括4部分:CMOS图像传感器图像数据采集模块、FPGA逻辑控制模块、SRAM读写模块及VGA显示模块.图 1为系统结构框图.

|

图 1 系统结构框图 Figure 1 Diagram of the circuit system structure |

系统以Altera公司的FPGA(现场可编程逻辑器件)EP2C8Q208C8N作为逻辑控制器[9],利用I2C(Inter-Integrate Circuit)总线配置CMOS图像传感器,采用两片SRAM (静态随机存储器)进行乒乓读写.FPGA根据CMOS图像传感器输出的同步信号,将CMOS图像传感器采集到的图像数据存储到其中一片SRAM中,同时读取另外一片SRAM,送到VGA显示器进行显示.整个系统的时序控制和数据流的读写控制都由FPGA来完成.

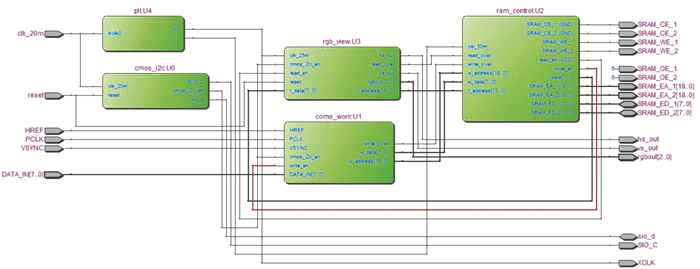

2 电路设计本文采用自顶向下的模块化设计思想,在Quartus Ⅱ平台下用Verilog硬件描叙语言来描叙整个驱动电路.如图 2所示,系统由以下4部分构成:时钟模块、图像采集模块、存储器控制模块、VGA显示模块.

|

图 2 电路原理图 Figure 2 Schematic diagram of circuit |

时钟模块把输入FPGA的20MHz时钟进行倍频,生成25MHz与50MHz时钟,分别输入VGA显示模块和存储器控制模块.图像采集模块的输入时钟为20MHz,该模块由I2C配置模块和图像数据采集模块构成,图中所示为cmos_i2c与cmos_work两大模块.在cmos_i2c模块中对寄存器进行配置,输出时钟SIO_C与双向数据sio_d.cmos_work, 主要完成取亮度信号的同时过滤掉色差信号的功能,最后输出写地址信号w_address与数据w_data.存储器控制模块对两片SRAM进行乒乓操作,即主要对图像采集模块输出的数据w_data进行乒乓读写.上述乒乓操作主要是由read_over与write_over两个输入信号进行SRAM读写切换,即采集到的数据进行SRAM存储与SRAM数据输出至VGA显示模块.最终,VGA显示模块对VGA显示的时序进行控制,达到很好的VGA显示效果.

2.1 图像采集模块图像采集模块由I2C配置模块和图像数据采集模块构成[10-11].OV7670图像传感器的初始化配置由SCCB总线接口编程完成,可以输出整帧、子采样、取窗口等方式的各种分辨率8位影响数据.用户可以完全控制图像质量、数据格式和传输方式.所有图像处理功能过程包括伽玛曲线、白平衡、饱和度、色度等都可以通过SCCB接口编程[12].而用于OV7670图像传感器配置的SCCB总线与I2C总线类似,它是一种双向二线制同步串行总线[13].因此,本文采用I2C总线对OV7670图像传感器进行配置.本设计只对主要的几个寄存器进行重新配置,其他采用默认设置.

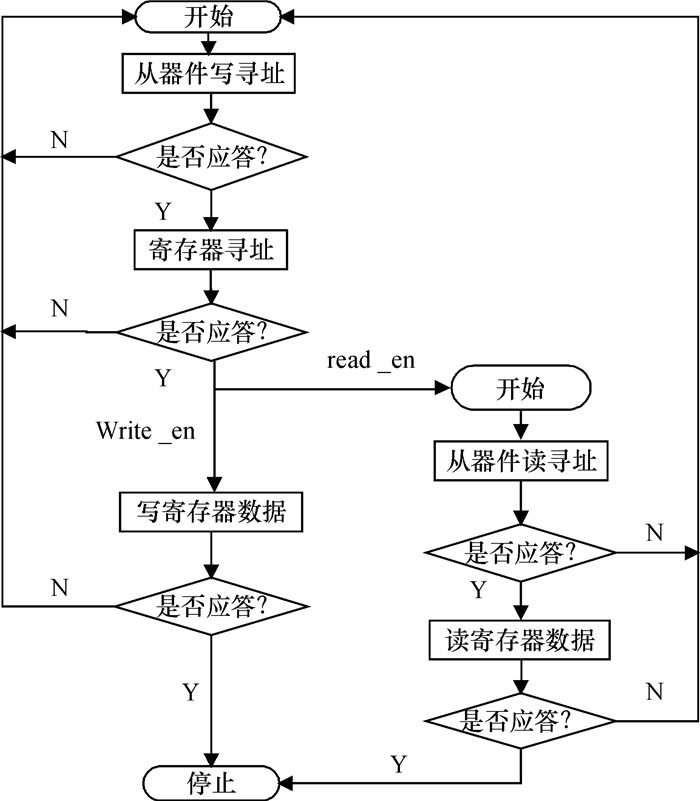

图像数据采集模块主要完成对I2C总线上的主从设备(传感器和其内部寄存器)的起始、读写和停止的时序控制[14].首先,要对OV7670内部寄存器进行配置,当write_en=1时,FPGA向OV7670发送写地址0X42,然后OV7670向FPGA发送应答信号;FPGA收到应答后,发送要进行写操作的寄存器的地址,然后OV7670向FPGA发送应答信号,FPGA收到应答后再发送写入该寄存器的数据,这样对每个寄存器依次进行写操作,其中发送每个地址和数据必须应答.当write_en=0时, 对OV7670内部寄存器进行读操作,过程和写操作类似,而本文主要对其进行配置,也即对OV7670进行写操作.图 3为I2C时序控制流程图.

|

图 3 I2C时序控制流程图 Figure 3 Flow chart of I2C timing control |

本文采用两片SRAM存储器进行乒乓操作,存放分辨率640×480每帧的图像数据.两块SRAM通过寄存器wren来进行切换,当wren=1时读出寄存器SRAM_ED_2中的数据,并把读地址r_address送入寄存器SRAM_EA_2,同时向寄存器SRAM_ED_1写入数据,并把写地址w_address送入寄存器SRAM_EA_1;当wren=0时两块SRAM切换,此时读出寄存器SRAM_ED_1数据,并把读地址r_address送入寄存器SRAM_EA_1,同时向寄存器SRAM_ED_2写入数据,并把写地址w_address送入寄存器SRAM_EA_2.由于采用乒乓机制,图像数据的采集与显示并行,从而提高了图像采集和显示的效果.相应Verilog代码如下.

……

reg wren;

assign SRAM_EA_1 = wren ? w_address : r_address;

assign SRAM_EA_2 = wren ? r_address : w_address;

assign SRAM_ED_1 = wren ? w_data : 8'hzz;

assign SRAM_ED_2 = wren ? 8'hzz : w_data;

assign r_data = wren ? SRAM_ED_2 : SRAM_ED_1;

……

2.3 显示模块对于普通的VGA显示器,共有5个信号:R、G、B三基色信号,行同步信号HSYNC和场同步信号VSYNC.本系统中,FPGA产生分辨率640×480(约30万像素),刷新频率60Hz的VGA时序信号,包括行同步、场同步及颜色信号[15].其中的颜色信号为灰度信号,即为CMOS图像传感器输出的YUV格式的信号去除色差信号U、V所剩下的亮度信号.该灰度信号经过电阻网络构成的D/A转换电路输出VGA显示.

2.4 时钟模块本系统中,输入CMOS图像传感器时钟为25MHz,SRAM读写模块时钟为50MHz,VGA显示需要25.175 MHz,系统提供该模块25 MHz时钟频率.而外部晶振是20MHz,在Quartus ii中用MegaWizard工具生成倍频模块,调用FPGA内部锁相环,进行倍频可得到上述的时钟频率.

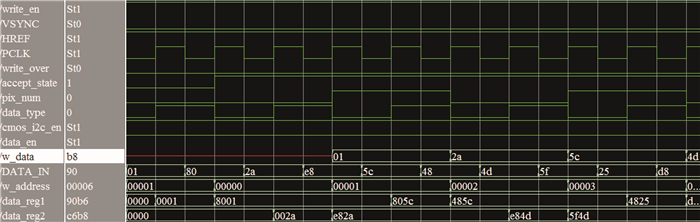

3 系统功能仿真结果及分析 3.1 CMOS采集模块仿真分析CMOS采集模块中,输出数据格式为YUV(也称YCrCb)4:2:2的格式,YUV的输出时序为Y-U-Y-V.由于相对于色差信号,人眼对亮度信号Y更为敏感,因此,对输入图像数据去除色差信号U、V,只取亮度信号Y.

该模块Modelsim仿真结果如图 4所示,首先CMOS传感器输出数据为8位数据DATA_IN,给DATA_IN的值为图中序列01-80-2a-e8-5c-48-4d……利用两个16位寄存器data_reg1和data_reg2可以实现分别存储和输出,相当于隔一个PCLK时钟取一个DATA_IN的值.最终,整个输出只有亮度信号数据w_data,而没有色差信号数据.

|

图 4 CMOS采集模块仿真波形图 Figure 4 Simulation waveform diagram of CMOS capture module |

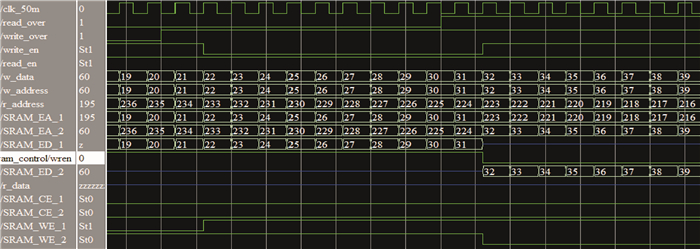

在SRAM控制模块中,设置read_en为1,即读使能,则CMOS采集的数据一直VGA输出.两块SRAM通过寄存器wren来进行切换.SRAM控制模块Modelsim仿真波形如图 5所示,当wren=1时把SRAM_ED_2设为高阻态,此时读寄存器SRAM_ED_2数据,并把读地址r_address送入寄存器SRAM_EA_2,同时向寄存器SRAM_ED_1写入数据w_data,并把写地址w_address送入寄存器SRAM_EA_1;当wren=0时两块SRAM读写状态、地址和数据切换.整个数据的传输在wren由1变为0的时刻进行切换,写入的数据w_data分别输出至寄存器SRAM_ED_1和SRAM_ED_2,没有出现丢数据的情况.

|

图 5 SRAM模块仿真波形图 Figure 5 Simulation waveform diagram of SRAM module |

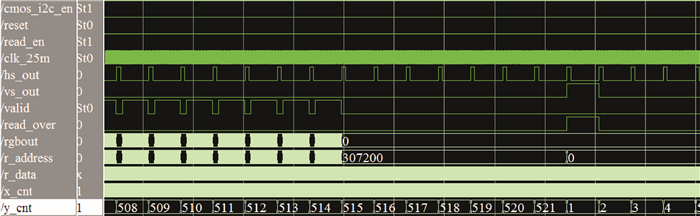

VGA标准输出分辨率为640×480,如图 6所示,r_address计数到307200(640×480)时,即为显示一帧图片的像素大小(约30万像素).

|

图 6 显示模块仿真波形图 Figure 6 Simulation waveform diagram of displaying module |

本系统采用FPGA作为逻辑控制芯片,利用CMOS图像传感器进行图像采集,两片SRAM作为帧存芯片.仿真结果及显示表明,系统实现了SRAM的乒乓操作,设计的CMOS图像传感器,其驱动时序表明其能够很好地满足实时图像输出需求,为干电池缺陷在线检测系统的研究提供了有力支持.

| [1] |

王旭东, 叶玉堂. CMOS与CCD图像传感器的比较研究和发展趋势[J].

电子设计工程, 2010, 18(11): 178-181.

Wang X D, Ye Y T. Comparative research and future tendency between CMOS and CCD image sensor[J]. Electronic Design Engineering, 2010, 18(11): 178-181. DOI: 10.3969/j.issn.1674-6236.2010.11.050. |

| [2] |

程开富. CMOS图像传感器的最新进展及其应用[J].

光电机信息, 2003(1): 16-26.

Cheng K F. CMOS image sensor and its application of the latest[J]. OME Information, 2003(1): 16-26. |

| [3] |

Sunetra K M, Sabrina E K, Russell C G, et al. CMOS active pixel image sensors for highly integrated image systems[J].

IEEE Journal of Solid State Circuit, 1997, 32(2): 187-197.

DOI: 10.1109/4.551910. |

| [4] |

Blank N Z. CCD versus CMOS - has CCD imaging come to an end[J].

Photogrammetric Week, 2001(1): 131-137.

|

| [5] |

Kleinfelder S, Lim S, Liu X Q, et al. A 10000 frames/s CMOS digital pixel sensor[J].

IEEE Journal of Solid State Circuits, 2001, 36(12): 2049-2059.

DOI: 10.1109/4.972156. |

| [6] |

曾桂英, 潘金艳. 基于FPGA的CMOS图像传感器采集系统设计[J].

科学技术与工程, 2010, 10(3): 692-695.

Zeng G Y, Pan J Y. Design of the CMOS Sensor image acquisition system based on FPGA[J]. Science Technology and Engineering, 2010, 10(3): 692-695. |

| [7] |

谢磊. 基于FPGA的VGA图像控制器的设计与实现[J].

新乡学院学报, 2009, 26(6): 51-53.

Xie L. Research and design of VGA display system based on FPGA[J]. Journal of Xinxiang University, 2009, 26(6): 51-53. |

| [8] |

侯舒志, 姚素英, 周津, 等. CMOS图像传感器时序控制方法研究与实现[J].

固体电子学研究与进展, 2007, 27(1): 119-122.

Hou S Z, Yao S Y, Zhou J, et al. Research andimplementation of timing control for CMOS image sensor[J]. Research & Progress of SSE, 2007, 27(1): 119-122. |

| [9] |

Corporation A. Cyclone FPGA family datasheet[EB/OL]. [2011-04-01]. http://www.altera.com.cn.

|

| [10] |

丁昊杰, 刘敬彪, 盛庆华. 基于CMOS图像传感器的视频采集系统设计[J].

现代电子技术, 2012, 35(14): 178-181.

Ding H J, Liu J B, Sheng Q H. Design of video acquisition system based on CMOS image sensor[J]. Modern Electronic Technique, 2012, 35(14): 178-181. DOI: 10.3969/j.issn.1004-373X.2012.14.056. |

| [11] |

刘泽伟, 解梅. 基于FPGA的视频图像采集系统的设计与实现[J].

仪器与仪表学报, 2008, 29(4): 382-385.

Liu Z W, Xie M. A system design and realization for video image acquirement based on FPGA[J]. Chinese Journal of Scientific Instrument, 2008, 29(4): 382-385. |

| [12] |

OmniVision Technology Inc. OV7670/OV7171 CMOS VGA (640x480) CAMERACHIP with OmniPixel Technology[EB/OL]. [2006-04-05]. http://www.ovt.com.

|

| [13] |

王晗, 李翔, 李忠敏, 等. 基于OV7670的图像采集与显示设计[J].

中国科技信息, 2013(11): 90-91.

Wang H, Li X, Li Z M, et al. Image acquisition and display design based on OV7670[J]. China Science and Technology Information, 2013(11): 90-91. DOI: 10.3969/j.issn.1001-8972.2013.11.045. |

| [14] |

Philips Semiconductors. The I2C-bus specification[EB/OL]. [2000-01]. http://www.philips.com.cn.

|

| [15] |

Video Electronics Standards Association. VESA and industry standards and guidelines for computer display monitor timing[EB/OL]. [2004-10-29]. http://bbs.elecfans.com.

|

2015, Vol. 32

2015, Vol. 32