由于片上系统不能满足大规模集成电路发展需要,新的设计方法片上网络(NoC)应运而生.它是把传统的计算机网络技术移植到芯片内部,以成本低廉的点对点分组交换架构取代传统的总线架构.文献[1]详细介绍了片上网络各组成部分,包括常见的Mesh拓扑网络跟Torus拓扑网络以及交换技术等基本概念.文献[2]提出一种基于片上网络的互连拓扑结构-层次化路由结构MLR(Multi-Layer Router).该结构通过层次化设计减小网络直径, 具有良好的对称性和扩展性.文献[3]具体提出了MECS拓扑网络结构(见图 1),但由于IP核数量的增加,输入缓冲区容易堵塞增加时延,而且对重要数据包传输也没有进行优先处理.文献[4]提出了虚拟通道控制器的设计.文献[5]提出利用交叉开关进行并行输入.文献[6]提出了一种拓扑结构,每个资源节点与两个路由节点连接,内部的路由节点与3个相邻的路由节点相连,虽然容错性能很好但它的面积和功耗都比较大.文献[7]对不同数目的缓冲区进行分析,优化性能.文献[8]采用模拟退火算法减少虚拟通道数目并优化分配方式, 达到功耗优化的目标.文献[9]采用了缓冲区被多个端口共享FIFO方式提高网络性能和硬件开销.文献[10]提出了QoS服务质量保证,针对不同数据采用不同优先级方式确保了高优先级数据包低延时的传输.本文针对当前决定NoC网络复杂程度的关键性因素拓扑网络, 采用了文献[3]的拓扑网络结构MECS,该结构的优点是多个IP核集成在一个路由节点上,然后采用一对多通信方式,提高了连通性,它们之间的传输不需要经过多个路由节点,避免了经过中间路由器的延迟和能量损耗,节点间平均距离(hop)最大为2,不仅节约了硬件资源,减少了通信延迟时间和提高了吞吐量,而且相对于3维拓扑网络[11]结构物理布局布线难度较小,而且在此基础上对输入输出模块进行改进和对特殊需要的数据包进行优先传输.本文分4部分,第1部分是MECS工作原理,第2部分是路由器结构,第3部分是路由算法,最后是实验验证结果.

|

图 1 MECS拓扑网络结构 Figure 1 MECS topology network architecture |

MECS是一种新型拓扑网络,使用一对多高程度的互连的通信模式,拥有较小网络直径.MECS是采用多个IP核集成在一个路由节点内,数据来自节点内IP核发出的和接收来自其他路由节点存储到Cache的.转发数据采用交换开关方式,输出到本地、水平方向路由节点和竖直方向路由节点,XY方向是采用广播方式直接输入到输入缓冲中,然后再比较是否要进行第二次广播[12],因此从源IP核到目的IP核之间最多只需要2次跳跃, 路由算法是采用XY无死锁算法,采用虚直通交换,避免了数据丢失,保证了较高的服务质量

2 路由器基本结构如图 1所示,MECS拓扑网络结构有64个IP核,按照编号把IP核每4个集成在一个路由节点上.因此64个IP核总共需要6位二进制数表示.0000_00表示第一个路由节点的第一个IP核, 以此类推,1111_00表示16个路由节点第64个IP核.总共有32条链路,网络直径为2,相比较Torus和Mesh拓扑网络结构,MECS能大程度地减少路由节点的个数和传输时转发的跳数,缩短了网络直接平均距离和延时.图 2为本文提出的MECS路由节点结构,拥有输入模块、IP核模块、VC控制器和交叉开关、路由算法模块.其中仲裁器采用的是轮询仲裁方式,路由算法是采用XY确定性算法,交换开关采用交叉阵列式.

|

图 2 路由单元结构 Figure 2 Routing unit structure |

如图 3所示,把微片大小定义为32位,其中头两位00表示头微片,头微片携带路由信息,01表示数据微片,10表示尾微片.首先数据从IP核出来,根据目的资源节点可以推算出目的节点在哪个路由节点上,然后把路由节点信息放在头微片上,数据分割成多个数据微片,最后在尾微片处结束.由于本文只有64位IP核,那么就只需6bit,高4位为节点数低2位是IP核数目例如0000_01则为第一个节点第2个IP核,其中节点数前两位为竖直方向,后两位为水平方向.P位为数据流优先级位,在网络接口注入数据时为某些重要业务或突发性业务设置优先级,在链路堵塞时,具有高优先级的数据流对链路拥有优先权,使系统得到及时实现功能.

|

图 3 微片结构 Figure 3 Filt structure |

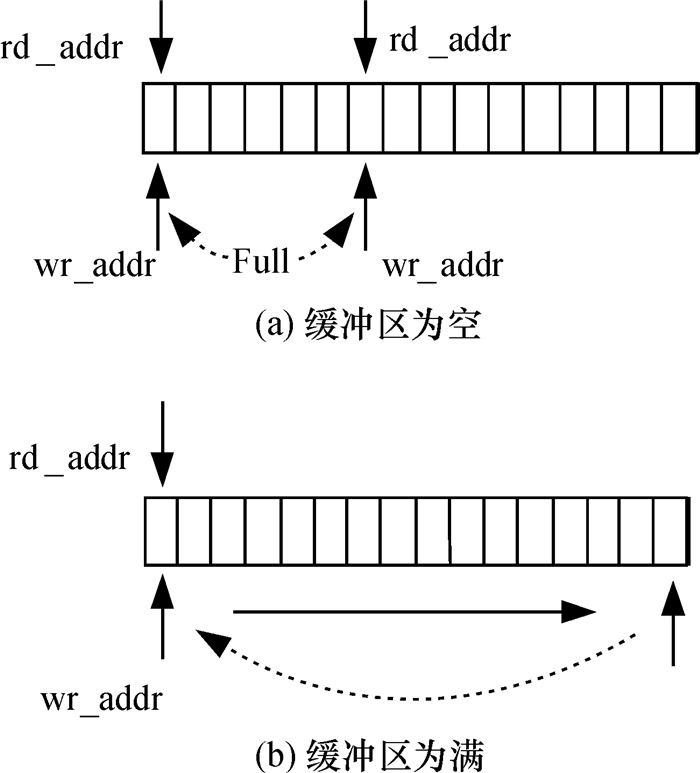

因为NoC受面积影响大,FIFO移位寄存器设计更适合,因为SRAM的地址译码器逻辑部分要求有额外的面积开销,并且在数据存储接入期间信号会有更频繁的翻转变换.本文输入的数据采用FIFO对数据包各微片并行存储.缓存器空间的大小由两个指标来定义,深度和宽度.宽度定义了包中并行字节的数量(FIFO内部字节的宽度),深度给出了路由缓存能够存储的给定大小的微片的最大数量.本文采用深度为12、位宽为32位的输入缓冲区,如图 4所示(a)为缓冲区空,(b)为满.用2个状态位表示,读和写循环单次用1表示,循环双次用0表示,当读写位置一样时,两个状态位相等则是空,不等则为满.每个输入端都拥有2个虚拟通道,其空满状态由标志位表示,由VC控制器控制.

|

图 4 FIFO空满标志 Figure 4 Empty or full flag of FIFO |

本文数据传输采用虚直通交换机制[13].它把数据包分割成很小的微片,如图 3所介绍的结构.所有的微片按数据包中的顺序排列好,以“流水线”的形式头微片先于数据微片和尾微片依次在网络中传输.在输入到Cache时,首先检查flit类型,如果是头微片且Cache为空则在仲裁器中标记,然后从缓冲区中输出数据flit,遇到尾flit时把标记取消,最后询问下一个Cache,这样保证了同一个包所有的微片按序传输,而且不会让其他数据包的微片插入进来,导致数据包出错.当没遇到堵塞时相当于直通,并且只占用缓冲区很少的资源就立马把微片转发出去,缩短了存储转发的时延.当遇到堵塞时,把数据全存储在最后一个堵塞的Cache中.因此每个Cache的深度应该等于或者大于数据微片的大小,等待下次输出.

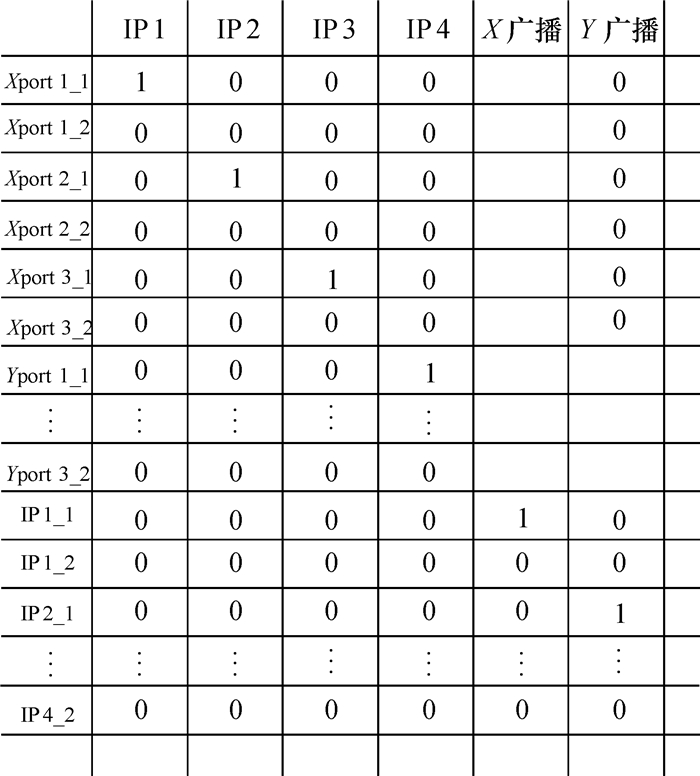

2.2 VC控制器和交叉开关仲裁器本文通过设置统一个数虚拟通道,并采用不同数目测试各自虚拟通道利用率和整个网络延时、吞吐量等性能.当网络出现多个业务竞争同时竞争同一资源传输数据导致堵塞时,仲裁器[14]根据一定的法则将资源优先分配给某个资源请求者.在输入缓冲区采用的是轮询方式仲裁存储数据.当要进入交叉开关后,存在多个输入端口传输的数据竞争同一个输出端口情况,这就存在如何分配和竞争的问题,本文输出数据时首先仲裁优先级高的业务进行传输,同一优先级的业务则按照计数器仲裁方式进行传输,来自水平方向和竖直方向的数据跟本路由节点4个IP核产生的数据共同竞争统一资源或者并发使用不同资源缩短时延,从而可以提高吞吐量.其中同等优先级下的交叉开关阵列如图 5所示.行为输入端口,列为输出端口,即从行端口中的Cache取出数据输出到列的端口去.

|

图 5 交叉开关 Figure 5 Crossbar |

图 5中每列最多只有一个1(1表示为列与行端口建立了通路,它是由仲裁器和路由算法决定),其余为0,当整个包微片输出完,然后恢复为0.此交换开关允许并行输出,如图 5所示是Xport1_1(水平输入端口1虚拟通道1)经过仲裁获得输入到IP核的优先权,建立了通路,直到数据包传输完毕,恢复为0,然后在其他端口继续竞争仲裁,其他类似都是并行工作.

2.3 路由算法路由算法[15]是在NoC网络中决定数据微片从一个路由器转发给下一个是哪个路由器的策略.是根据数据包头微片包含的路由节点信息、IP核信息、数据微片类型信息、业务类型优先权信息和本地路由信息相结合, 通过一定的仲裁方式来决定下一跳路由节点的算法.

本文路由节点的数据来自两个方面,分别是从其他路由节点输入到缓存和本地路由节点输出的,首先从缓冲区中取出数据先判断该数据的优先级,如果是优先级高则优先取得输出权,(1)假如是从竖直缓冲区取出数据则直接传输到本节点目的IP核;(2)如果是水平缓冲区先直接判断是否本路由节点就是目的节点,如果不是则把输入进行竖直方向广播,如果是就直接判断是本路由节点的哪一个IP核;(3)如果是从IP核直接输出的数据,那么就先判断目的IP核是否为本路由节点,如果是就直接输入IP核,如果不是则先判断水平方向是否一致,如果不一致则在水平方向进行广播,如果是就直接进入竖直方向广播.当发现不是高优先级时,那么就将进入计数器仲裁方式,通过自身计数器数值大小最高的取得输出权按照同样的方式进行传输,如果没有获取到优先权,那么就将进入下一轮回的等待,计数器要加1.其中当取得输出权时,必须在交叉开关阵列中标识为1,说明已经被占用,其他输入端口想竞争时,直到数据微片输出完(标志位为0)时才能再次竞争资源,

3 实验结果本文详细介绍了MECS路由器结构,并用模拟仿真软件Modelsim10.0版本实现,采用verilog语言编写而成的,实例化64个IP核16个路由器节点,每个路由器节点集成有4个内部IP核,连接成4×4MECS网络,

如图 6所示,目的是从第1个路由节点(编号00)第1个IP核发出数据(00_0111_11_1_0000000,其中最高两位是00,说明是头微片,)传输到第7个节点的第4个IP核位置,由于此数据包拥有高优先级1,则比其他普通数据拥有竞争资源优先传输数据.IP核在路由节点(编号0000)发出数据判断出要X广播,由于设置了其他IP核也发出数据进行Y广播,存在竞争资源,如图所示得到了权限,进行广播,不用存储.数据在水平方向其他的路由节点进行判断接收,第三个路由节点(编码0011)判断数据符合自己,则把数据存入Xport1缓冲区中,通过FIFO得到数据进行判断,发现是要进行Y广播,则要跟路由其他水平缓冲区和IP核其他发出Y广播的进行竞争端口权限,图中竞争失败,原因是此通道已经被使用了,等待一组微片时间,然后得到权限,输出到第7个路由节点(0111)Yport1缓冲区,由于同样的原因,竞争失败,之后因为高优先级得到输入权限,第4个IP核成功接收数据.

|

图 6 实验结果 Figure 6 The experimental results |

往每个IP核注入32 Bit*5*20数据量,初始化数据向指定IP核传输数据,每个路由节点最多共有6路并行工作,实际整个传输过程有16个路由节点共有63路并行工作,原因是数据先后注入并传输到指定目的传输,按照路由算法依次传递存在时间差以及数据没覆盖所有链路导致,当更多数据在网络传输时,该拓扑结构的传输路径短和多路并发优势就发挥出来.在功能仿真下[16],以1 ns为时间单位,完成时间为306 ns,理想时间是200 ns,而MESH需要时间是438 ns.其中MECS位宽是一个flit单位32 Bit, 平均带宽是6.69*105Bit/s,其与理想状况相比,同一路由节点各Cache内共同竞争水平或竖直方向时要发生资源竞争,按照高优先级后按计时器优先级规则占用资源,从而导致时间延迟,比理想状况直接有链路到达时间慢,但节省更多硬件资源.

实验证明,本文所设计的拓扑网络能成功发送和接收数据,实现无差错、无丢失,通过与2DMesh相比较,在注入通信量很大的情况下评估整体网络性能,通过波形图体现本拓扑网络比后者在时间延迟方面有较大的缩短,通过设置不同数目虚拟通道以及注入不同的数据包总量时,发现当虚拟通道为4时,延时最少,虚拟通道利用率较高.结果表明,该结构适用于片上网络的应用.

4 结束语近年来,众多学者对NoC的拓扑网络研究主要集中在MESH和Torus上,并在此基础上不断完善,但由于各自缺陷,发展已受到限制.本文提及的架构思想原理新颖,物理实现发展正在加速成熟,拥有网络直径小、实现技术容易和节省硬件开销等优点.从仿真结果看,相比传统的拓扑网络,MECS确实拥有传输延迟小、吞吐量大、所消耗功能低和硬件资源节省等众多优势,而且在物理布局布线方面也不会存在技术问题,因此这结构将会是NoC发展的一个重要研究方向,给CMP芯片厂商巨大的推力.本研究内容交换机制为虚拟直通技术可能存在一定的限制性,采用冲孔交换技术跟虚拟通道技术优化结合和解决传输热点问题是笔者以后着重研究的课题.

| [1] |

William J D, Brian T. Principles and P Practices of Interconnection Networks[M]. San Francisco: Morgan Kaufmann, 2004.

|

| [2] |

陈芳露, 陆雯青, 虞志益, 等. 一种新型片上网络互连结构的仿真和实现[J].

小型微型计算机系统, 2010, 31(5): 883-887.

Chen F L, Lu W Q, Yu Z Y, et al. Simulation and implementation of a new NoC-based interconnection network[J]. Joumal of Chinese Computer Systems, 2010, 31(5): 883-887. |

| [3] |

Grot B, Hestness J, Keckler S W, et al. Express cube topologies for on-chip interconnects[J].

IEEE 15th International Symposium, 2009, 6(5): 163-174.

|

| [4] |

张旺, 汪金辉, 侯立刚, 等. 基于FPGA的片上网络虚拟通道控制器的设计[J].

微电子学与计算机, 2012, 29(5): 10-14.

Zhang W, Wang J H, Hou L G, et al. The design of netword-on-chip virtual channel controller based on FPGA[J]. Microelectronics & Computer, 2012, 29(5): 10-14. |

| [5] |

万玉鹏, 吴宁. NoC路由单元的系统级设计[J].

苏州科技学院学报:工程技术版, 2009, 22(2): 61-64+68.

Wan Y P, Wu N. NoC system's design of router[J]. Suzhou of University of Science and Technology:Engineering and Technology, 2009, 22(2): 61-64+68. |

| [6] |

Lehtonen T, Liljeberg P, Plosila J. Fault tolerance analysis of NoC architectures circuits and systems[J].

IEEE International Symposium on Circuits and Systems, 2007, 2(2): 27-30.

|

| [7] |

王荣阳, 王科. 基于NIRGAM的片上网络性能仿真[J].

航空电子技术, 2014, 45(1): 30-34.

Wang R Y, Wang K. Performance simulation of network-on-chip based on NIRGAM[J]. Avionics Technology, 2014, 45(1): 30-34. |

| [8] |

周芳, 吴宁, 周磊, 等. 面向低功耗的片上网络虚通道分配算法[J].

东南大学学报:自然科学版, 2013, 43(2): 263-267.

Zhou F, Wu N, Zhou L, et al. Low-power-aware virtual channel allocation algorithm for network on chip[J]. Journal of Southeast University:Natural Science Edition, 2013, 43(2): 263-267. |

| [9] |

刘炎华, 孙玲, 赖宗声. 一种用于片上网络的异步共享FIFO设计[J].

微电子学与计算机, 2013, 30(7): 159-162.

Liu Y H, Sun L, Lai Z S. Design of a asynchronous shared-FIFO for NoC[J]. Microelectronics & Computer, 2013, 30(7): 159-162. |

| [10] |

衡霞, 支亚军, 韩俊刚. 基于片上网络多处理器QoS研究与设计[J].

计算机科学, 2013, 40(6A): 220-222.

Heng X, Zhi Y J, Han J G. Based on network on chip of multiprocessor QoS mechanism research and design[J]. Computer Science, 2013, 40(6A): 220-222. |

| [11] |

相沪平. 网络广播及其实现原理[J].

甘肃科技, 2009, 25(01): 66-67.

Xiang H P. Broadcast network and Implementation[J]. Gansu Science and Technology, 2009, 25(01): 66-67. DOI: 10.3969/j.issn.1000-0952.2009.01.025. |

| [12] |

虞潇, 李丽, 张宇昂, 等. 一种面向功耗免死锁三维全动态3D NoC路由算法[J].

电子学报, 2013, 41(02): 329-334.

Yu X, Li L, Zhang Y A, et al. A power-aware dead lock avoid three-dimensional full-adaptive routing algorithm for 3D NoC[J]. Acta Electronica Sinica, 2013, 41(02): 329-334. DOI: 10.3969/j.issn.0372-2112.2013.02.019. |

| [13] |

王峥, 顾华玺, 杨烨, 等. 片上网络交换机制的研究[J].

中国集成电路, 2007, 16(12): 22-27.

Wang Z, Gu H X, Yang Y, et al. A study of switching mechanisms in network-on-chip[J]. China Integrated Circuit, 2007, 16(12): 22-27. DOI: 10.3969/j.issn.1681-5289.2007.12.004. |

| [14] |

赵国鸿, 吴虎城. 分布式总线仲裁器的设计[J].

计算机工程与科学, 1998, 20(02): 11-14+70.

Zhao G H, Wu H C. Design of the distributed bus arbiter[J]. Computer Engineering & Science, 1998, 20(02): 11-14+70. |

| [15] |

王丹丹, 郭大昌, 王静. 星图应用米哈尔顿拉丁方的并行路由算法[J].

广东工业大学学报, 2011, 28(1): 62-67.

Wang D D, Guo D C, Wang J. A parallel routing algorithmon star graph network employing the hamiltonian circuit latin square[J]. Journal of Guangdong University of Technology, 2011, 28(1): 62-67. |

| [16] |

张宇华. 基于可编程逻辑器件技术的基本模型机实验的设计与实现[J].

广东工业大学学报:社会科学版, 2010, S1: 49-51.

Zhang Y H. The design and implementation of the basic model machine based on complex programmable logic device(CPLD) technology[J]. Journal of Guangdong University of Technology:Social Sciences Edition, 2010, S1: 49-51. |

2015, Vol. 32

2015, Vol. 32