短时傅里叶变换作为一种常用的时−频分析方法,在语音信号、信号识别等方面应用十分广泛[1-3],其基本思想是在傅里叶变换的基础上实现时域的局部化。对于时变信号,短时傅里叶变换采用一个滑动窗截取信号,并且认为窗内的信号是平稳的,对这些信号进行傅里叶变换,可以得到信号在某一时刻的频谱。通常情况下,为了克服窗与窗内数据的关联性,相邻两窗会有所重叠,重叠的长度越长对分析该信号的频谱越准确。本文设置每次滑动的数据长度为滑动窗长度的1/4。

1 滑动短时傅里叶变换的原理离散序列信号的短时傅里叶变换的定义为

| ${X_n}\left( {{{\rm{e}}^{{\rm{j}}\omega }}} \right) = \sum\limits_{m = - \infty }^\infty x (m)w(n - m){{\rm{e}}^{ - {\rm{j}}\omega n}}$ |

式中:

本设计所采用的开发板为Altera公司提供的Stratix ii-EP2S180C3,使用的软件环境为Quartus ii 13.0,波形仿真采用了第三方软件Modelsim,开发板的实物图如图1所示。

|

Download:

|

| 图 1 Stratix ii-EP2S180C3开发板 | |

本设计充分利用Altera公司所提供的IP核,简化了以往设计的过程,设计利用ROM核存储汉明窗的数据。FIFO核实现滑动窗。通过使用FFT核实现傅里叶变换,要根据设计需求进行FFT核模式的选取,并根据芯片手册进行FFT核时序的编写。利用这些工具可以很方便地实现滑动短时傅里叶变换的功能,不需要推导复杂的数学公式,相对于文献[4-6]中的复杂数学公式推导更简洁,更容易使用现有工具进行实现。

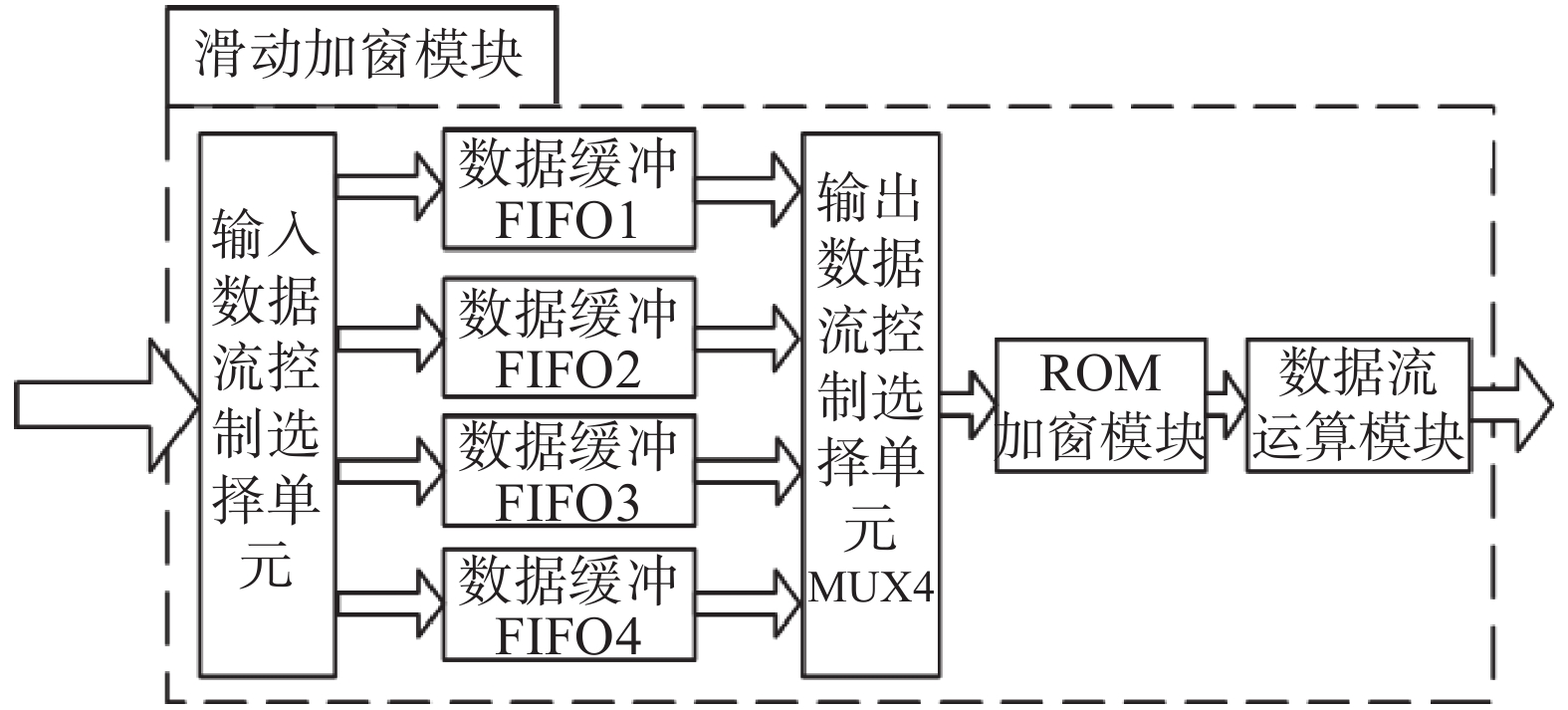

3 设计思路总框图设计的前提条件是希望判断下一段信号在各个窗内频谱特征,根据频谱特征可以检验信号所含有的频率成分,用于信号解调,设计总体框图如图2所示。

|

Download:

|

| 图 2 滑动短时傅里叶变换的FPGA设计框图 | |

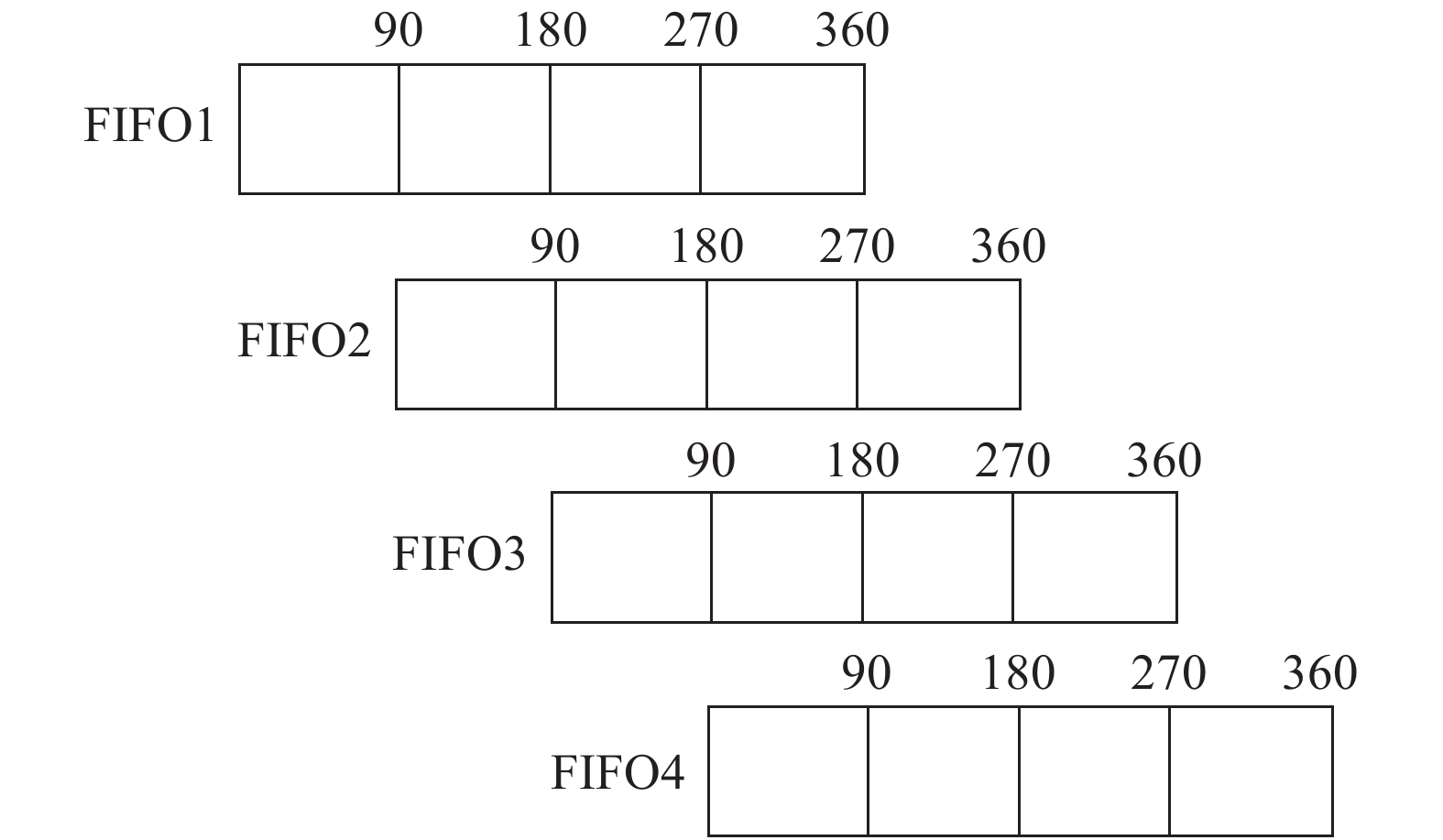

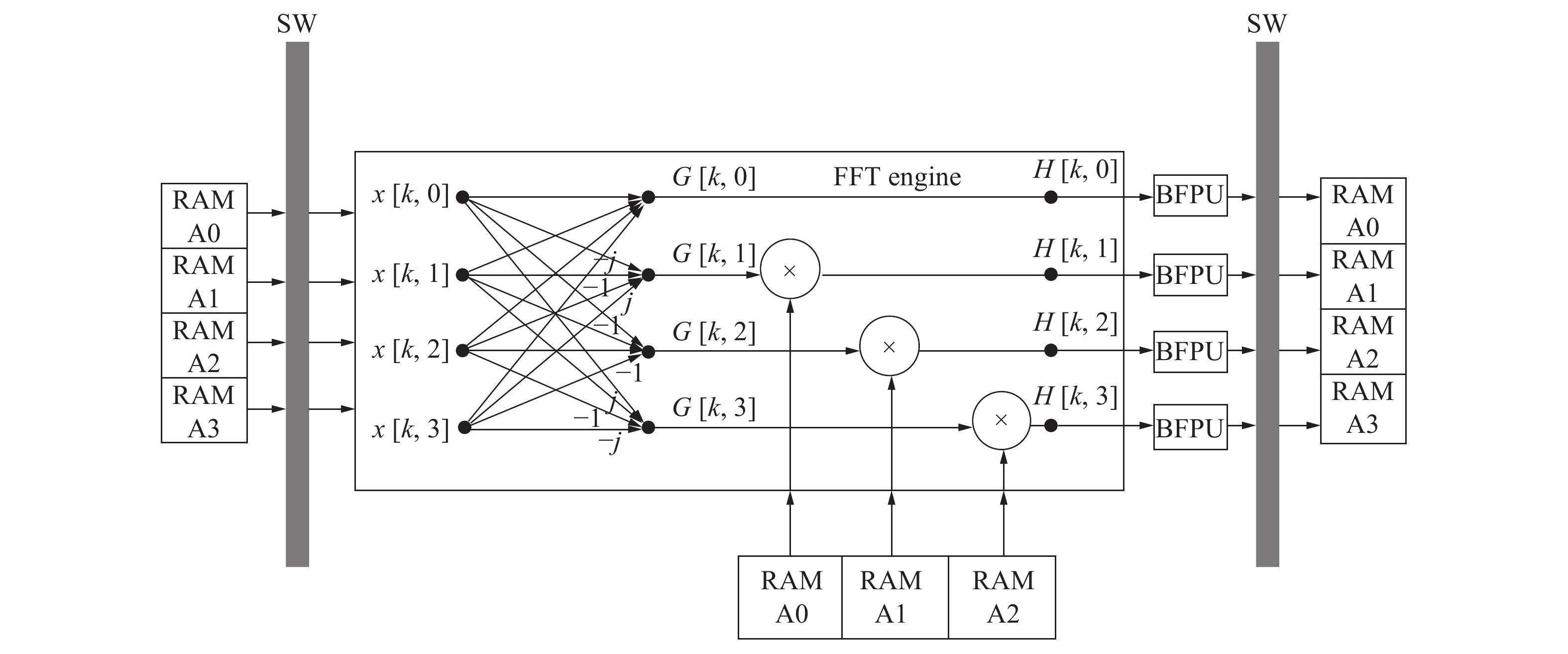

设计中为了避免数据堵塞及丢失,应用了乒乓思想[7],使用了4个相同的FIFO。4个FIFO通过输入数据选择流单元进行控制,使用FIFO_cnt的计数大小判定当前哪个FIFO写入数据。设计中每次滑动窗更新数据长度为90,则当FIFO1_cnt的大小大于90,此时FIFO2就要准备进行写入数据;当FIFO2_cnt的大小大于90,此时FIFO3就要准备进行写入数据;当FIFO3_cnt的大小大于90,此时FIFO4就要准备进行写入数据。至此一个循环下,FIFO的写使能都打开了。输出数据流选择单元也是通过FIFO_cnt的数据大小来决定当前哪个FIFO的数据输出,每个时刻只有一个数据输出,其FIFO间的滑动图如图3所示,90、180、270、360分别代表FIFO中的4个地址段。

|

Download:

|

| 图 3 滑动窗(FIFO)控制设计 | |

汉宁窗的实现采用了ROM核,存放汉宁窗[8]函数数据。通过MATLAB生成360点Hanning窗函数系数表,由于该数据为浮点数,而本设计中采用定点化运算,将系数表生成mif文件,作为ROM的初始化文件。

FIFO核和ROM核的使用中设计一个共同的使能,当FIFO核有数据读出时,ROM核也会有数据读出,两者同步输出:送入乘法器进行加窗计算,输出数据位宽24位,送给后端的FFT模块进行计算,根据FFT的输出有效信号source_valid的高低指示,进行判断信号特征,解调信号。

4 FPGA具体实现 4.1 滑动窗口设计滑动窗使用了异步FIFO[9],FIFO选择结构如图4所示。其中FIFO的大小设置的512,数据位宽是16,读时钟Rdclk和写时钟Wrclk的大小相差5倍,FIFO的读写使能分别为Rdreq、Wrreq,输出满标志位Wrfull,空标志位Rdempty。

|

Download:

|

| 图 4 异步FIFO的结构 | |

设计中需要4个FIFO,4个FIFO轮换输出数据,4个FIFO的切换采用了状态机的思想,状态机设计了8种状态,如图5所示。当一个状态完成之后,再切换到下一个状态,否则一直处于当前状态。

|

Download:

|

| 图 5 滑动窗的状态机设计 | |

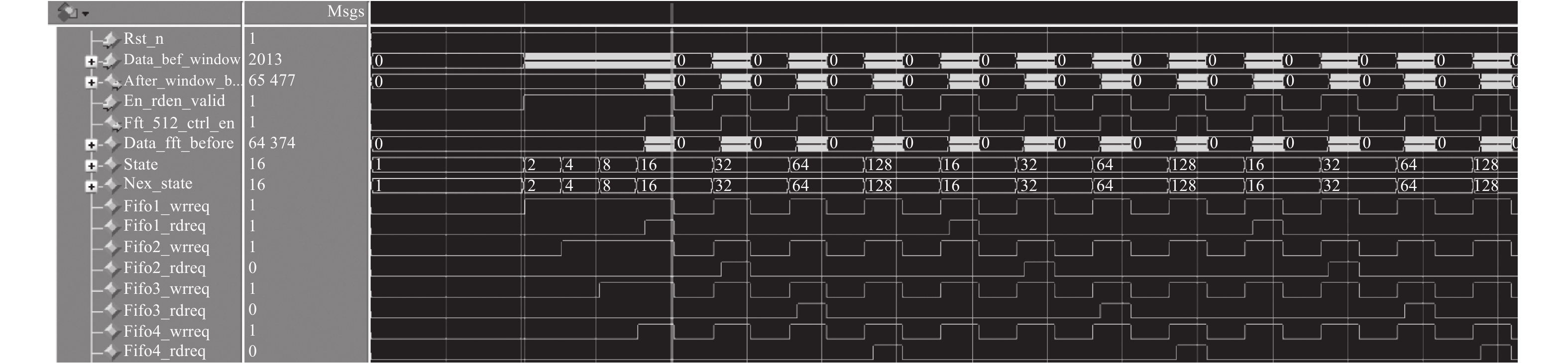

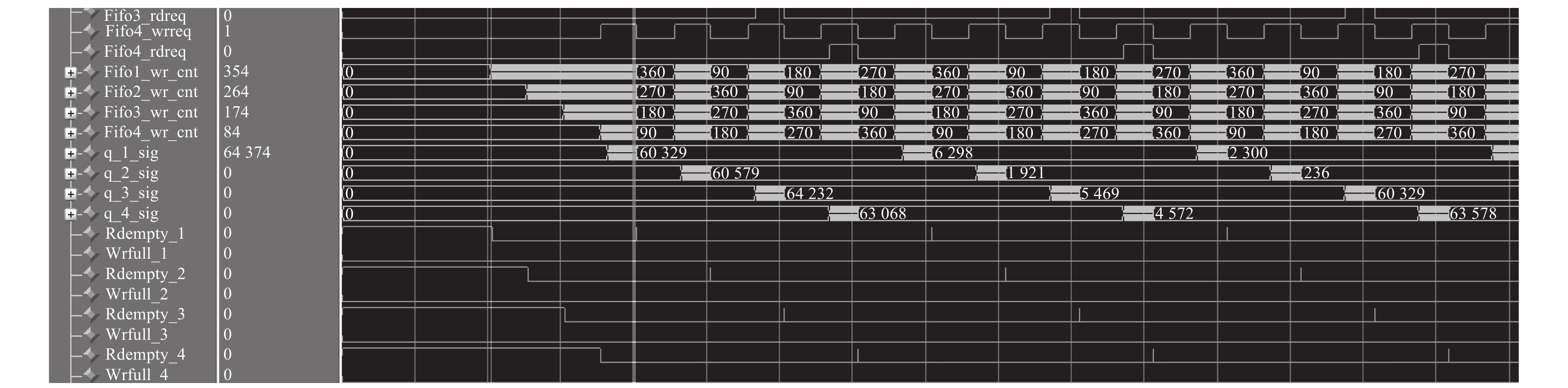

图6为滑动窗口的仿真波形,刚开始时,Fifo1_wreq的电平为高,FIFO1开始写入数据;当写到第90个数据时,此时FIFO2的Fifo2_wreq置成高电平,FIFO2开始写入数据;此时State同时发生跳转;当FIFO2写数据写到第90个时,FIFO3的Fifo3_wreq被置高电平,FIFO3开始写数据;此时state在此发生了跳转,数据继续进行写入;当FIFO3写入数据写到第90个数据时,此时FIFO1写到了第270个数据,FIFO4的Fifo4_wreq被置成高电平,开始写数据;此时4个FIFO的Wreq都被制成高电平,写入数据。当FIFO1再写进18个数据时就要开始读数据,Fifo1_rdreq变为1,维持读时钟的72个高电平,360个数据被写进FIFO1时,同时也读空了,之后开始新的循环。

|

Download:

|

| 图 6 滑动窗口的仿真波形 | |

当FIFO1在写进288个数据时就要开始读数据,Fifo1_rdreq变为1,维持读时钟的72个高电平,360个数据被写进FIFO1时,同时也读空了,此时FIFO1的读使能就被关闭;当FIFO2在写进288个数据时,FIFO2就要开始读数据,Fifo2_rdreq变为1,维持读时钟的72个高电平,360个数据被写进FIFO2时,同时也读空了,Fifo2_rdeq变为0;同理FIFO3、FIFO4。4个FIFO轮流输出数据,每次只有一个读使能有效。

图7为滑动窗模块的仿真波形,可以看到每个窗相邻的将有3/4的数据是重复的,4个FIFO轮换输出数据。

|

Download:

|

| 图 7 滑动窗口控制仿真波形 | |

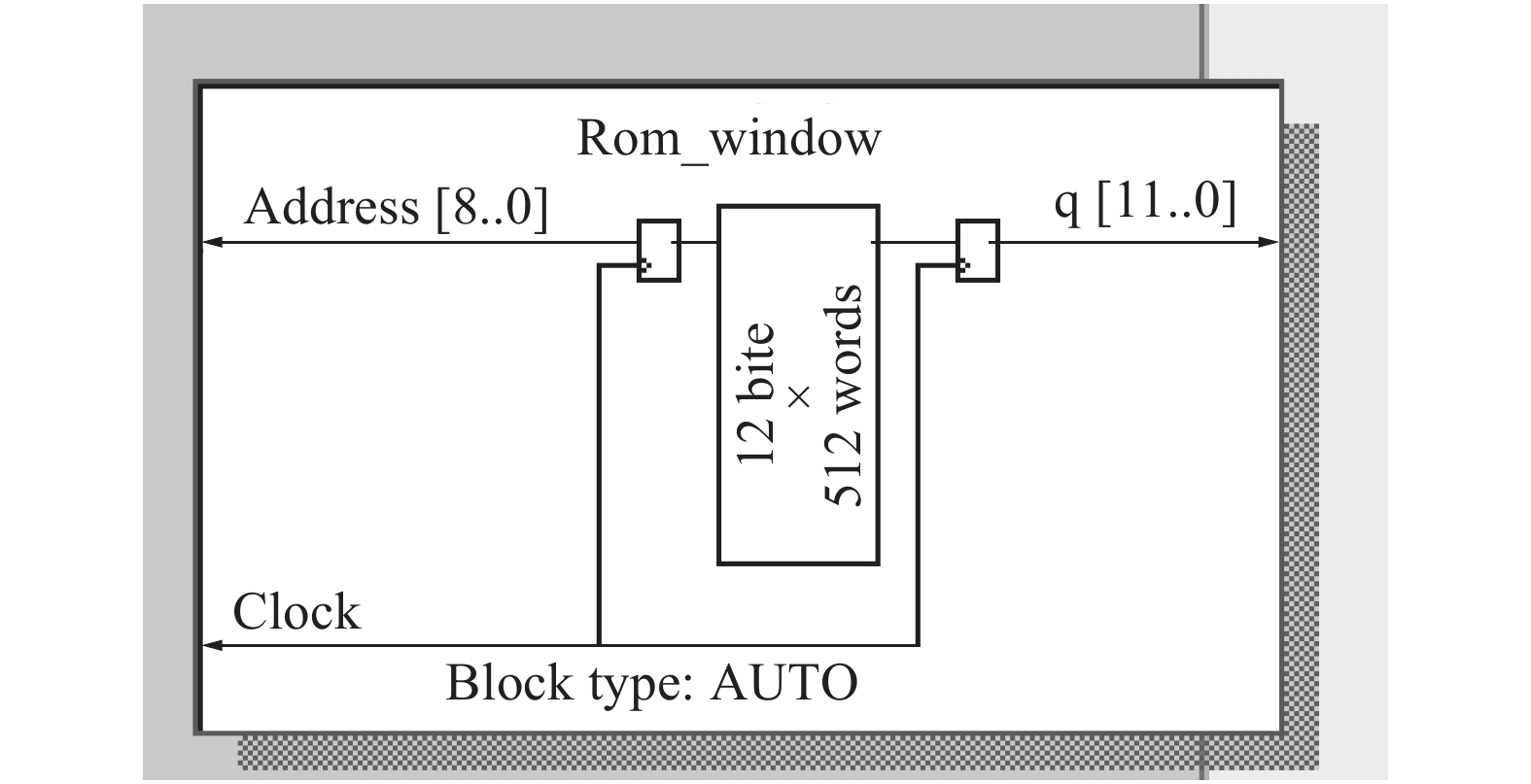

Hanning窗使用了ROM[10],ROM采用Altera公司提供的IP核,ROM中的地址线由于只能为2的整次数幂,取最贴近码元宽度的512作为该ROM的地址数,数据位宽为A/DC的输出数据宽度12,ROM值在初始化时被赋予了汉宁窗的数据,其结构如图8所示。

|

Download:

|

| 图 8 ROM窗结构 | |

Hanning窗数据仿真波形为图9,在每个时钟的上升沿数据从ROM端读出,其数据波形如图中的q所示。

|

Download:

|

| 图 9 ROM读出的数据显示波形 | |

乘法器的结构如图10所示。

|

Download:

|

| 图 10 乘法器设计的结构图 | |

输入端数据Dataa、Datab分别来自于FIFO输出的数据和ROM窗内的数据,二者相乘之后的结果为24位,为信号加过窗的数据,数据送给FFT模块进行计算。

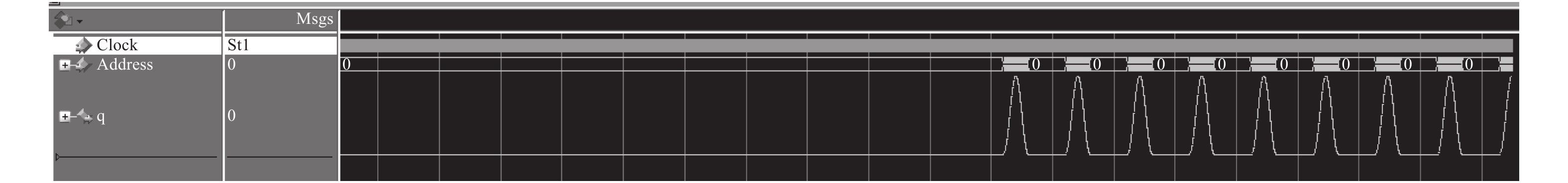

4.4 傅里叶变换模块设计傅里叶变换[11]部分选择FFT核[12],FFT核可以设置FFT变换的数据长度、输入数据精度、运算中旋转因子数据精度,并提供了4种运算结构,可以根据板子的运算速度及硬件资源情况进行选择使用。由于数据是实时采集进来的,所以设计结构中选择了流模式。流模式的运算分2个进程:载入数据及输出数据进程和FFT变换运算过程,且这2个进程可以同一时间处理。当FFT变换启动时,输入数据首先在时钟的控制下输入信号到FFT核内部的存储器内,当一帧数据载入完成后才开始计算,FFT变换后的数据在FFT变换完成后再输出到相应的端口,流模式下的FFT结构如图11所示。

|

Download:

|

| 图 11 流模式下的FFT结构 | |

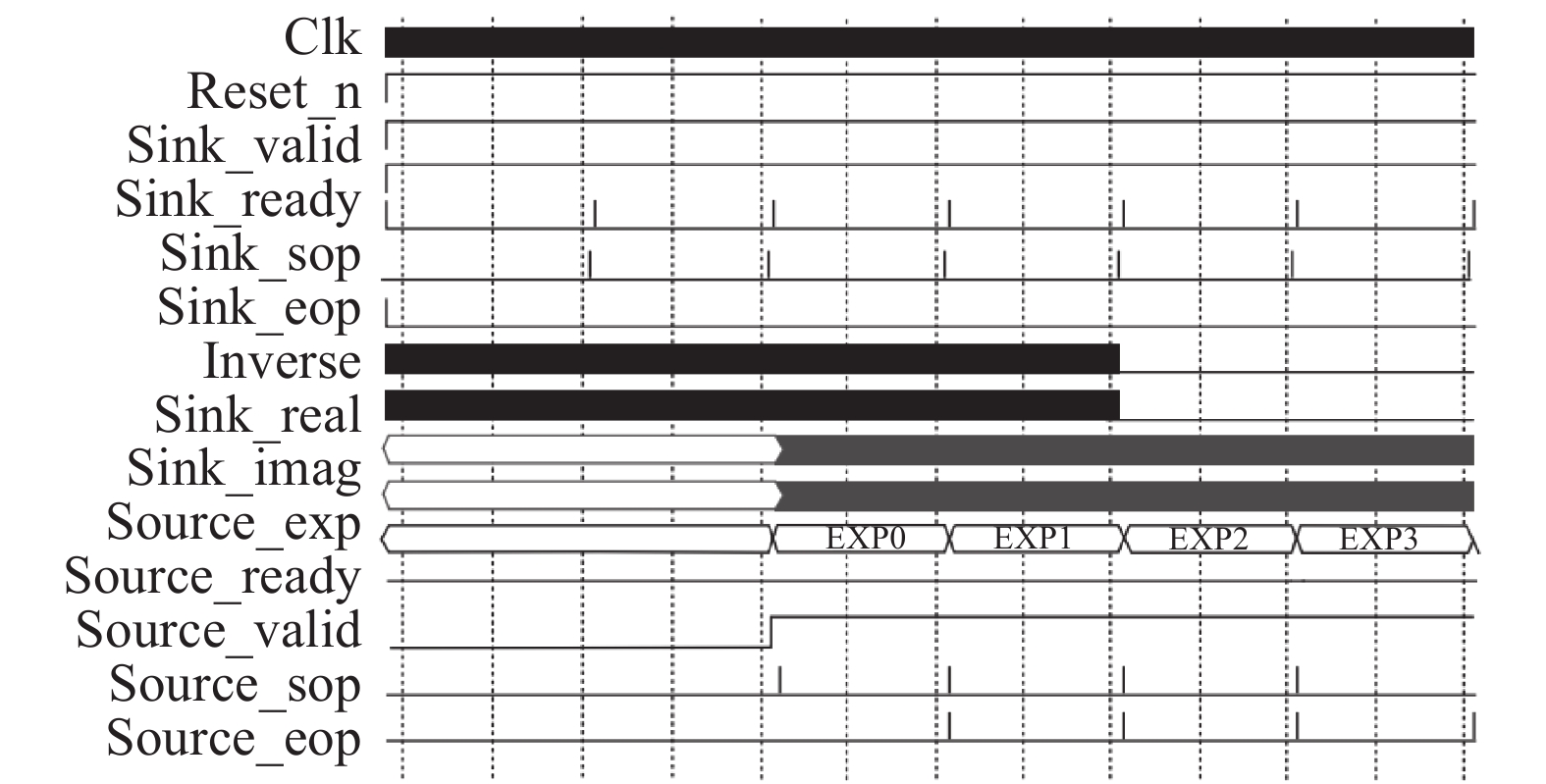

流模式的时序接口如表1所示。流模式的FFT时序图如图12所示。从图中可以看出,输入数据是连续的,无论载入数据还是FFT运算,数据输出都是同时进行的。

|

|

表 1 FFT核模块端口介绍 |

|

Download:

|

| 图 12 流模式下的FFT时序 | |

实际应用中,可以根据变换有效数据输出时Source_valid为高电平期间来确定出现峰值的位置,进而根据位置号推算出信号中包含的信号频率,进行信号的解调等处理。

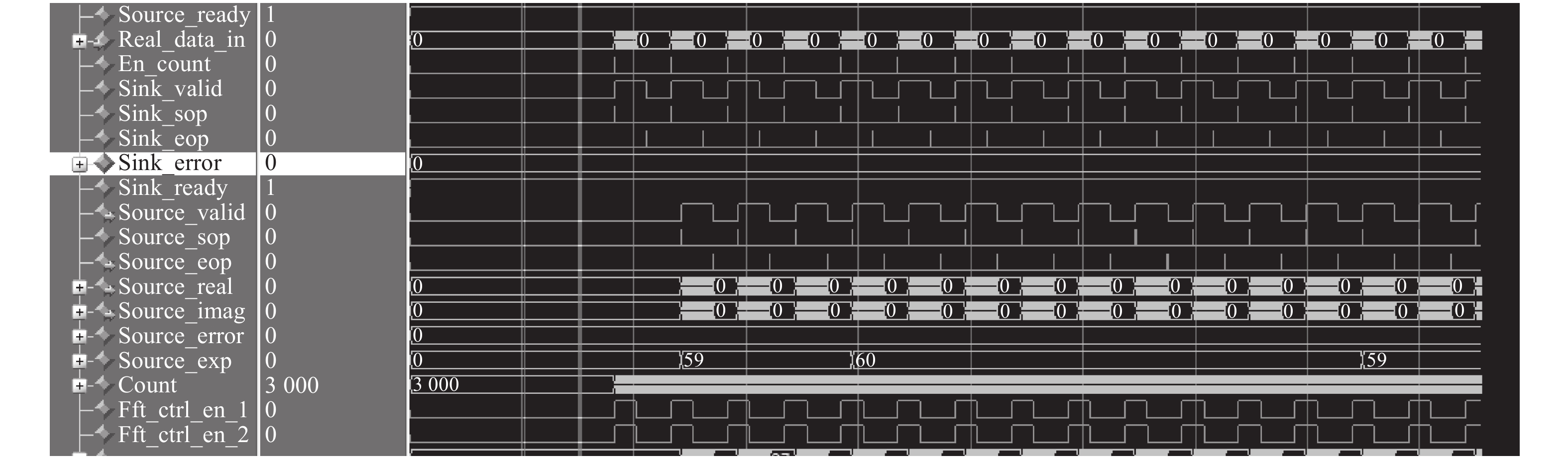

流模式下的FFT工作,Modelsim的波形如图13所示。当有数据输入时Sink_valid为1;当输入第一个数据时,Sink_sop为高;当输入最后一个数据时,Sink_eop电平由低变高,维持一个时钟的高电平。FFT核计算结束结果输出,Source_valid拉高。当输出数据第一个值时,Source_sop被拉高一个时钟的高电平,之后变成低电平;当输出数据最后一个值时,Source_eop被拉高一个时钟的高电平,之后变成低电平。

|

Download:

|

| 图 13 流模式下的FFT仿真波形 | |

本文提出了利用Altera公司提供的现有IP核进行直接设计实现滑动短时傅里叶变换,从思路到实现上难度都不大,并给出了具体的设计与实现,其采用的方法可以用来其他的相关处理。

1)滑动窗口的实现采用了具有数据先进先出特点的FIFO作为数据缓存,读写时钟可以不一样,且不用控制地址线,使用操作都很简单。

2)设计中使用了Altera公司提供的FFT核直接进行傅里叶变换,只需要根据FFT手册进行恰当的时序设计,完成自己想要的功能,不需要从原理基础上设计出一个傅里叶变换模块,可以减少研发时间,降低研究成本。

| [1] |

徐永海, 赵燕. 基于短时傅里叶变换的电能质量扰动识别与采用奇异值分解的扰动时间定位[J]. 电网技术, 2011, 35(8): 174-180. ( 0) 0)

|

| [2] |

杜放辉, 骆海涛, 艾冬生, 等. 基于全极点滑动窗离散短时傅里叶变换的解调[J]. 探测与控制学报, 2013, 35(5): 61-64, 68. ( 0) 0)

|

| [3] |

章兰英, 侯孝民, 郑海昕. 短时傅里叶变换软件解调中窗函数影响分析[J]. 装备指挥技术学院学报, 2005, 16(6): 98-101. DOI:10.3783/j.issn.1673-0127.2005.06.023 ( 0) 0)

|

| [4] |

陈军. 基于FPGA的短时傅里叶变换分析及实现设计[J]. 贵州大学学报(自然科学版), 2017, 34(2): 64-69. ( 0) 0)

|

| [5] |

王珍, 孙兰, 杨阳. 短时傅里叶变换的FPGA实现及其应用[J]. 噪声与振动控制, 2012, 32(5): 154-158. ( 0) 0)

|

| [6] |

陈军. 基于MaxplusⅡ的短时傅里叶变换分析及仿真实现研究[J]. 辽宁大学学报(自然科学版), 2016, 43(1): 27-31. DOI:10.3969/j.issn.1000-5846.2016.01.006 ( 0) 0)

|

| [7] |

郭天圣, 鲁敏. 基于“乒乓操作”思想实现高速FFT的仿真[J]. 河南科技, 2013(22): 13-15. ( 0) 0)

|

| [8] |

涂亚庆, 沈廷鳌, 张海涛. 基于重叠短汉宁窗DTFT算法的科氏流量计信号处理方法[J]. 数据采集与处理, 2013, 28(1): 22-27. DOI:10.3969/j.issn.1004-9037.2013.01.005 ( 0) 0)

|

| [9] |

刘环雨. 一种FIFO的读写单元设计[J]. 微处理机, 2019, 40(1): 13-15. DOI:10.3969/j.issn.1002-2279.2019.01.004 ( 0) 0)

|

| [10] |

杨敏, 王利, 张金时, 等. 基于FPGA的DDFS信号发生器设计[J]. 自动化仪表, 2019, 40(2): 95-97, 102. ( 0) 0)

|

| [11] |

冷建华. 傅里叶变换[M]. 北京: 清华大学出版社, 2004: 50-60.

( 0) 0)

|

| [12] |

孙桂玲, 纪永鑫, 张潺潺. 高速高精度FFTIP核的设计与仿真研究[J]. 系统仿真学报, 2010, 22(8): 2018-2022. ( 0) 0)

|

2020, Vol. 47

2020, Vol. 47