2. National & Local Joint Engineering Laboratory for RF Integration and Micro-packaging Technologies, Nanjing 210003, China

集成电路的特征尺寸遵循着摩尔定律迅速减小,当前14 nm工艺CMOS集成电路已经投入了商用[1]。而等比例缩小原则表明,为保持器件性能不退化,晶体管的横向和纵向尺寸都要保持相同的比例缩小,这也意味着集成电路的有源层厚度也需要进一步减薄,特别是SOI技术[2]、FinFET技术[3]和无结晶体管技术[4]等新技术出现以后,有源硅层的厚度由10 μm以上(PD SOI)减薄到了几十纳米[5](FD SOI),直至10 nm以下[6](UTB SOI)。当前已经出现了在2~5 nm的硅膜上研制晶体管的报道[7~8]。

为了监测硅膜本身,或者硅膜与介质层界面的质量,人们最常用的方法是电容-电压(CV)特性法,该方法通过提取金属-绝缘层-半导体(MIS)或金属-氧化层-半导体(MOS)结构的低频或高频CV曲线,可以提取硅膜掺杂浓度、绝缘层厚度、绝缘层固定电荷和界面态密度等物理参数[9]。但是,常规CV法适用的前提是硅膜厚度远远大于最大耗尽层宽度。如前所述,当硅膜厚度很薄时,在CV测定时硅膜会完全耗尽,从而改变CV曲线,影响参数提取的准确性。为此,本文借助二维仿真器件MEDICI研究了薄硅膜厚度下MIS结构的低频和高频CV特性,通过分析能带结构,探讨硅膜厚度对CV特性影响的的内在原因,而后研究了金属与半导体功函数差和绝缘层固定电荷对薄硅膜厚度MIS结构CV曲线的影响规律。本文的研究为借助CV法对薄硅膜MIS结构进行精确参数提取与表征奠定了基础。

1 CV特性为了简化分析,首先考虑理想MIS结构,即满足如下假设:1) 绝缘层为理想绝缘层,即界面电荷、绝缘层固定电荷、可动电荷和界面态均可忽略不计;2) 半导体和金属的功函数差为零;3) 金属和金属键合的界面无任何缺陷。

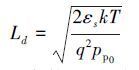

在对MIS结构进行CV特性研究时,和硅膜厚度tsi相关的特征尺寸有3个:最大耗尽区宽度Wdm、德拜长度Ld和反型层厚度tinv。通常Wdm>Ld>tinv。为此,分以下4种情况研究MIS结构的CV特性:1) tsi>Wdm;2) Ld<tsi<Wdm;3) tsi< Ld;4) tsi<tinv。

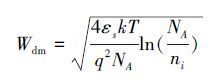

其中,最大耗尽区宽度Wdm和德拜长度Ld的表达式为[10]

|

(1) |

|

(2) |

式中:εs为硅的介电常数,k为波尔兹曼常数,T为绝对温度,q为电子电荷,NA为半导体掺杂浓度,ni为本征载流子浓度,pp0为P型硅的平衡空穴浓度。

图 1给出了这4种情况下,MIS结构低频和高频电容与外加电压关系的MEDICI二维数值仿真结果。其中,半导体为P型,半导体掺杂浓度为5×1014 cm-3,绝缘层厚度ti为0.5 μm。由图 1(a)可以看出,对于常规MIS结构,即硅膜厚度大于Wdm时,低频CV特性曲线有一个极小值,并在正负偏压较大时饱和;当硅膜厚度小于Wdm时,低频饱和电容值不变,低频电容极小值随着硅膜厚度的减小而逐渐增大;当硅膜厚度小于Ld时,低频电容极小值在逐渐增大的同时CV曲线中间会存在一个“平台”,并且随着硅膜厚度的不断减小,低频CV曲线的“平台”逐渐上移且变宽;当硅膜厚度小于反型层厚度tinv时,低频CV曲线呈一条直线。由图 1(b)可以看出,对于常规MIS结构,高频CV特性曲线在正负偏压较大时饱和,并在正偏压较大时,电容饱和值也是极小值。当硅膜厚度小于Wdm时,负偏压高频饱和电容值不变,高频电容极小值随着硅膜厚度的减小而逐渐增大;当硅膜厚度小于Ld时,高频电容极小值在增大的同时相应的电压极小值向负偏压方向移动;当硅膜厚度小于tinv时,高频CV曲线呈一条直线。

|

| 图 1 不同硅膜厚度下,MIS结构CV特性曲线 |

为了研究不同硅膜厚度下CV曲线相差巨大的物理本质,借助MEDICI研究了施加不同外加电压时MIS结构半导体层的本征费米能级(禁带中心能级),如图 2所示。该图给出了本征费米能级(禁带中心能级)和费米能级差在半导体层中的分布。由图 2(a)可见,对于常规MIS结构,当外加电压为-4 V时,表面处能带向上弯曲,空穴堆积在靠近表面的薄层内,MIS结构的总电容近似等于绝缘层电容;当外加电压为0 V时,表面处能带基本不弯曲,电荷基本平衡,MIS结构的总电容为平带总电容[10]:

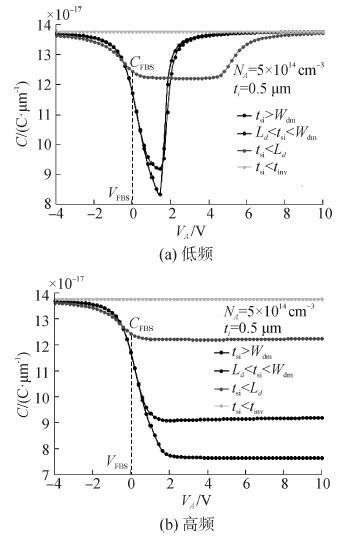

|

(3) |

式中:εi为绝缘层的介电常数,ti为绝缘层厚度。

当外加电压为1.4 V时,表面处能带相对于体内向下弯曲,费米能级高于本征费米能级,电子浓度超过空穴浓度,表面处于弱反型状态。此时,空间电荷区由反型层中的电子和耗尽层中已电离的受主负电荷组成。由图 1(a)可知,此时低频CV曲线取得极小值,其值由半导体微分电容的最小值决定,与硅膜厚度无关;当外加电压为-4 V时,表面处能带进一步向下弯曲,表面强反型,MIS结构低频总电容由绝缘层电容决定,高频总电容达到极小值[10]:

|

(4) |

其仅与最大耗尽区宽度有关。

|

| 图 2 不同硅膜厚度下,不同偏置时MIS结构半导体层的本征费米能级相对费米能级分布曲线 |

当硅膜厚度小于Wdm时,如图 2(b)所示,当外加电压分别为-4、0 V时,半导体表面能带弯曲与图 2(a)一致,分别处于积累和平带状态,因此如图 1所示,低频和高频CV曲线在负偏压时相对常规MIS结构的CV曲线不变;当外加电压为1.4 V时,MIS结构的半导体表面处于弱反型态,半导体内部全耗尽。此时低频电容极小值与高频电容极小值近似相等,而由于物理限制,耗尽层无法继续扩展,因此低频和高频电容极小值为

|

(5) |

如图 1所示,当硅膜厚度小于Wdm时,低频和高频CV曲线的极小值随着硅膜厚度的减小而增大。当外加电压为4 V时,半导体表面处于强反型态,低频电容由绝缘层电容决定,高频电容为电容极小值。

当硅膜厚度小于Ld时,如图 2(c)所示,当外加电压为-4、0 V时,表面分别为积累态,平带状态,此时低频和高频电容分别由绝缘层电容和平带总电容决定,其低频和高频CV曲线相对常规MIS结构不变。当外加电压为1.4 V时,能带相对体内向下弯曲,表面处于耗尽态;而外加电压为4 V时,能带进一步向下弯曲,表面处于弱反型态,可见相对于常规MIS结构而言,推迟了反型。而MIS结构总的平带电容不可能小于电容极小值,因此联立式(4) 和式(5) ,当硅膜厚度小于Ld时,平带电压VFBS和电容极小值相对的电压极小值处,低频和高频电容是一定值。又因半导体层处于全耗尽状态,MIS结构的低频和高频电容极小值由式(5) 决定,即由硅膜厚度决定。因此如图 1所示,低频CV曲线存在一个“平台”,并且随着硅膜厚度的减小而上移,高频电容极小值相应的外加电压向着负偏压移动,并且随着硅膜厚度的减小而增大。

当硅膜厚度小于tinv时,如图 2(d)所示,本征费米能级始终高于费米能级,且呈线性分布,即电场为均匀分布,MIS结构的总电容相当于基板电容器电容,只与绝缘层厚度、硅膜厚度相关,而硅膜厚度相对于绝缘层厚度可以忽略,如图 1所示,其低频和高频电容是个常数,不随外加电压变化而变化。

3 分析与讨论以上讨论的是理想薄硅膜MIS结构的CV特性,没有考虑金属和半导体功函数差及绝缘层中存在电荷等因素的影响。实际中这些因素对薄硅膜MIS结构的低频和高频CV特性均会产生显著的影响。

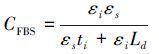

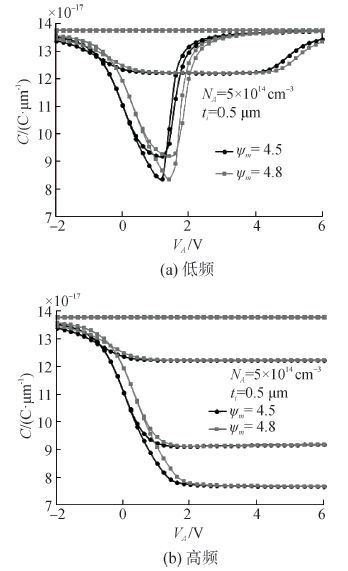

图 3给出了考虑金属与半导体功函数差时,不同硅膜厚度下MIS结构的低频和高频CV特性曲线。其中半导体层掺杂浓度NA为5×1014 cm-3,绝缘层厚度ti为0.5 μm。

|

| 图 3 考虑功函数时不同硅膜厚度下MIS结构的CV特性曲线 |

由图可知,当硅膜厚度大于tinv时,即对于上述4种情况的前3种情况,金属与半导体功函数差对MIS结构CV特性的影响类似,它会引起低频和高频CV曲线平行于电压轴移动,并且随着ψm的减小,即金属与半导体功函数差的减小,低频和高频曲线左移幅度逐渐增大。但当硅膜厚度小于tinv时,该结构的低频和高频CV曲线不随金属功函数的变化而变化,即与金属与半导体功函数差无关。

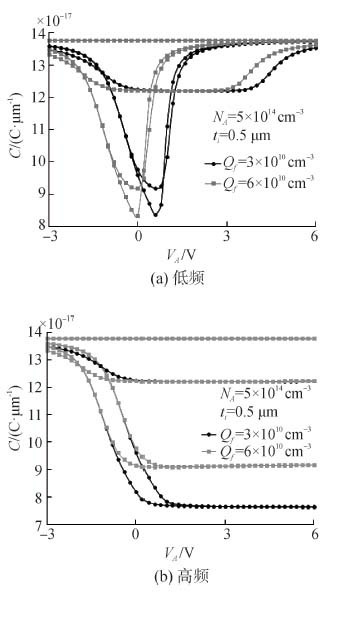

图 4给出了考虑绝缘层固定电荷Qf时,不同硅膜厚度下MIS结构的低频和高频CV特性曲线。

|

| 图 4 考虑绝缘层固定电荷时,不同硅膜厚度下MIS结构的CV特性曲线 |

由图可知,当硅膜厚度大于tinv时,绝缘层固定电荷使得该结构低频和高频CV曲线平行于电压轴向左移动,并且随着Qf的增加,低频和高频曲线左移幅度逐渐增大。但当硅膜厚度小于tinv时,该结构的低频和高频CV曲线不随绝缘层固定电荷的变化而变化,即与绝缘层固定电荷无关。

4 结论本文利用MEDICI对薄硅膜MIS结构的低频和高频CV特性进行了数值模拟,并探讨了其内在机理,而后分析了在金属与半导体功函数差、绝缘层固定电荷等因素的影响下该结构的电容-电压特性。

1) 当MIS结构的硅膜厚度薄于常规的厚度,即分别低于最大耗尽区宽度、德拜长度和反型层厚度时,该结构呈现出不同的CV特性。

2) 当MIS结构的金属与半导体之间存在功函数差或者绝缘层存在固定电荷,且硅膜厚度不低于反型层厚度时,该结构的低频和高频CV曲线平行于电压轴移动;但当硅膜厚度低于反型层厚度时,CV曲线不变,仍是一条直线。

| [1] | SHEU B, OLSTEIN K. Moore's law challenges below 10nm:technology, design, and economic implications[J]. IEEE solid-state circuits magazine, 2015, 7(2): 67-68 DOI:10.1109/MSSC.2015.2418472 |

| [2] | ESTIVILL R, GRENIER A, PRINTEMPS T, et al. 3D atomic scale analysis of CMOS type structures for 14 nm UTBB-SOI technology[J]. Microscopy and microanalysis, 2015, 21(S3): 521-522 DOI:10.1017/S1431927615003402 |

| [3] | BARDON M G, SCHUDDINCK P, RAGHAVAN P, et al. Dimensioning for power and performance under 10nm:the limits of FinFETs scaling[C]//Proceedings of the 2015 International Conference on IC Design & Technology. Leuven, Belgium:IEEE, 2015:1-4. |

| [4] | PAZ B C, ÁVILA-HERRERA F, CERDEIRA A, et al. Double-gate junctionless transistor model including short-channel effects[J]. Semiconductor science and technology, 2015, 30(5): 1-11 |

| [5] | TRIVEDI V P, FOSSUM J G. Nanoscale FD/SOI CMOS:thick or thin box[J]. IEEE electron device letters, 2005, 26(1): 26-28 DOI:10.1109/LED.2004.839624 |

| [6] | GNANI E, GNUDI A, REGGIANI S, et al. Physical model of the junctionless UTB SOI-FET[J]. IEEE transactions on electron devices, 2012, 59(4): 941-948 DOI:10.1109/TED.2011.2182353 |

| [7] | YU Xiao, KANG Jian, TAKENAKA M, et al. Experimental study on carrier transport properties in extremely-thin body Ge-on-insulator (GOI) p-MOSFETs with GOI thickness down to 2 nm[C]//Proceedings of the IEEE International Electron Devices Meeting. Washington, DC:IEEE, 2015:2.2.1-2.2.4. |

| [8] | LEE Y J, CHO T C, KAO K H, et al. A novel junctionless FinFET structure with sub-5nm shell doping profile by molecular monolayer doping and microwave annealing[C]//Proceedings of the 2014 IEEE International Electron Devices Meeting. San Francisco, CA, USA:IEEE, 2014:32.7.1-32.7.4. |

| [9] | SRIVASTAVA V M. Capacitance-voltage measurement for characterization of a metal-gate MOS process[J]. International journal of recent trends in engineering, 2009, 1(4): 4-7 |

| [10] | SZE S M, NG K K. Physics of semiconductor devices[M]. New York: Wiley, 2015: 197-240. |