2. Nanjing HaoShiKang Petroleum Equipment Co., Ltd., Nanjing 210000, China

当前,ARM9/11和Cortex-A8/A9处理器已经成为RISC指令系统CPU市场上的绝对主流,适用于智能手机、硬盘驱动器、数字电视和机顶盒等领域,并且正向PC和服务器芯片市场的主宰者英特尔发起挑战。高速PCB技术已经成为此类电子产品设计的重要环节,伴随的时序、噪声、电磁干扰等是电路板或封装设计的主要困难,能否解决这些信号完整性问题直接影响到整个设计是否可以稳定工作。虽然很多工程师在这方面有丰富的经验,但是出于技术保密,往往很少有人分享自己的研究成果。本设计使用PADS电路设计软件绘制以三星公司的嵌入式处理器S3C6410为核心的高速PCB电路板,阐述系统设计中削弱和消除干扰的解决方法,完成PCB设计、制板、调试。

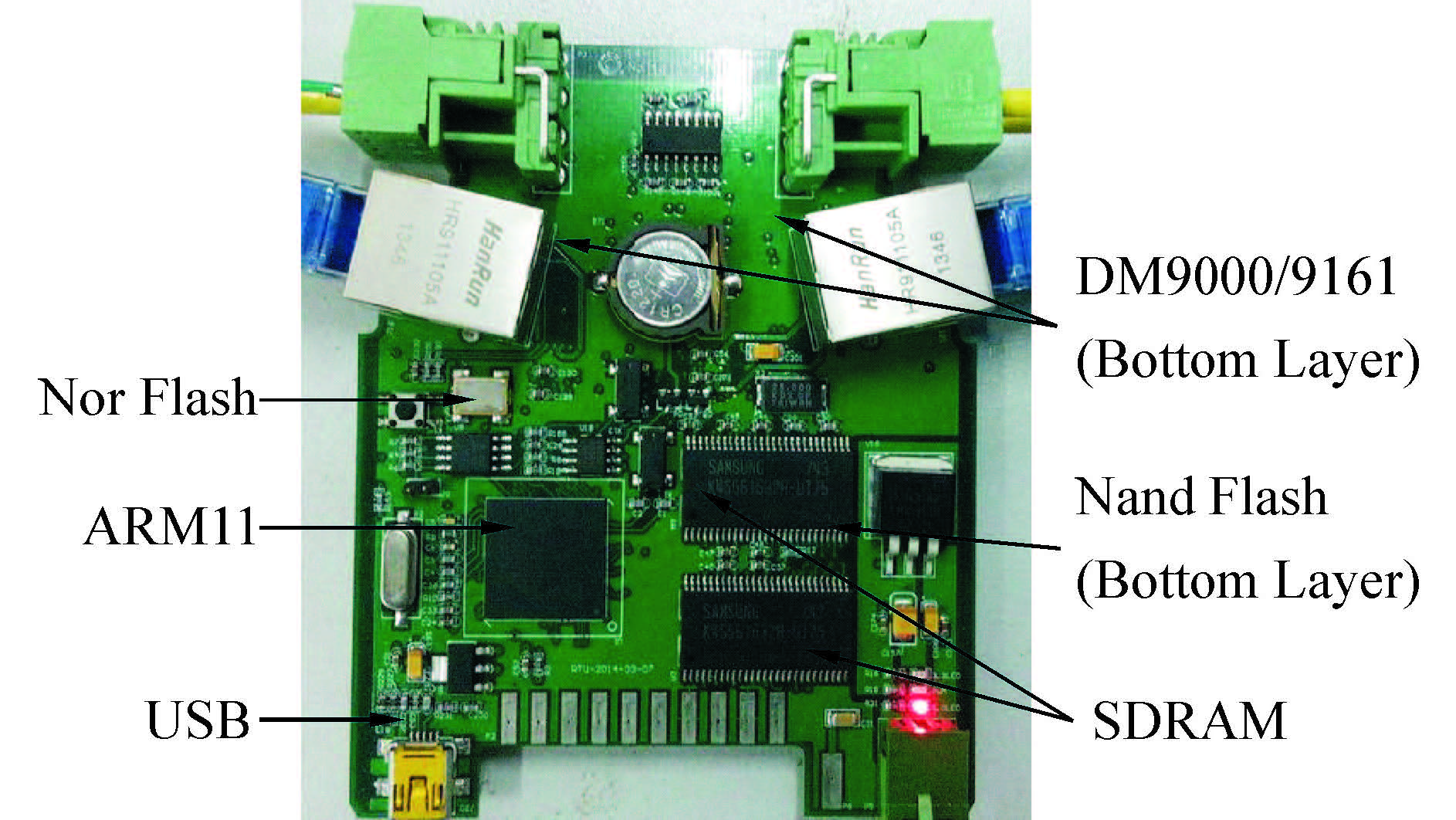

1 系统设计系统硬件主要由嵌入式处理器S3C6410、FLASH、SDRAM、USB2.0、CAN、UART、网络控制器等组成,主要应用于油气水井状态的远程监控。以Linux内核和Jffs2文件系统为软件支持平台,应用嵌入式开发技术和网络编程技术,支持IPv4/IPv6双栈网络通信协议。自主完成高速核心电路板设计后,考虑到系统的稳定性,做了全面的测试。外部传感器设备通过RS485、CAN总线接入系统进行通讯,以ModBus-TCP协议与ModBus-ASCII协议转换通讯测试网络层的可靠性。系统硬件电路板如图 1所示。

|

| 图 1 系统硬件电路板 |

其中,S3C6410的子系统ARM1176JZF-S具有JAVA加速引擎,具备超高速先进的AMBA总线架构,操作速率达到667 MHz,FLASH的传输速率是160 MHz,SDRAM的通信速率高达200 MHz,USB2.0支持高速480 Mb/s片上收发,DM9161/DM9000是百兆网络控制器[1]。

2 信号完整性在高速数字系统中,集成电路的开关速度很快,信号完整性已经成为高速信号印制电路板设计必须考虑的问题,它将决定信号在电路中以正确的时序和电压做出响应的能力[2]。如果电路中的信号能够以要求的时序、保持时间、电压幅度到达IC,则该电路具有较好的信号完整性。反之,信号就会出现反射、振铃、串扰和电磁兼容性等问题。

该系统板级ARM11与外设的通信速率在66~480 MHz,这一频率在电视、调频广播、移动电话等通信波段内,这就意味着这些频谱重叠的信号会相互产生电磁辐射干扰。要“补救”EMI(Electromagnetic Interference,电磁干扰)问题,除了做好产品屏蔽外,PCB的布局、布线设计也要采取滤波、接地措施,通过屏蔽、滤波和接地等方式将干扰源隔离及增强敏感电路的抗干扰能力[1, 2]。

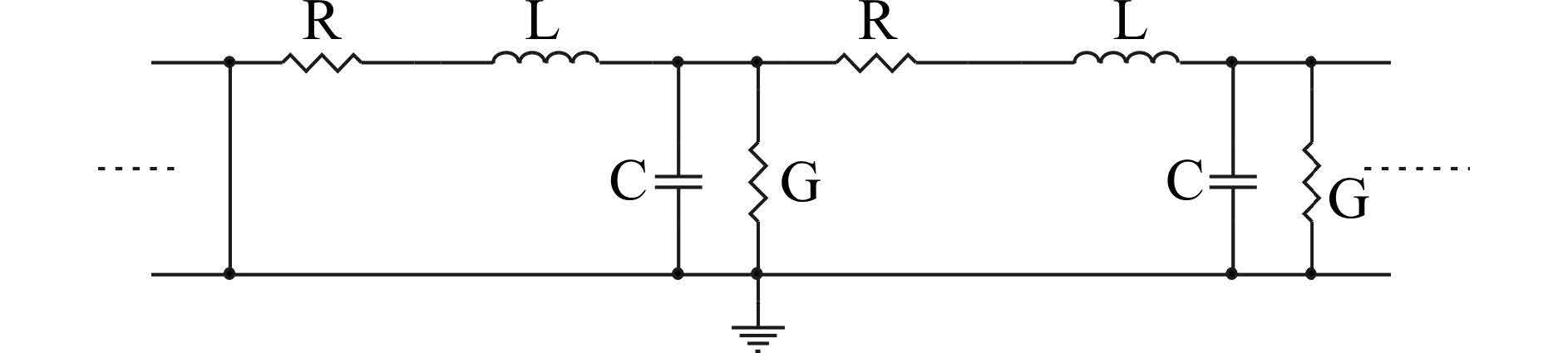

3 特征阻抗传输线上任何一处瞬时电流与电压比例都恒定的特性,称之为传输线的“特征阻抗”,它是影响信号传输质量的一个重要因素。当传输线的特征阻抗与负载和元器件I/O接头阻抗不匹配时,信号会有一部分能量沿着传输线反射回去,导致信号波形发生畸变。然而,不论传输线是均匀的还是非均匀的,信号在传输过程中都会有所损耗,带损耗的传输线可以用n节RLC集总电路模型来近似,如图 2所示。

|

| 图 2 有损传输线RLC电路模型 |

任何信号都可以分解为直流分量和交流分量2部分,此时微带线线的传输阻抗为

|

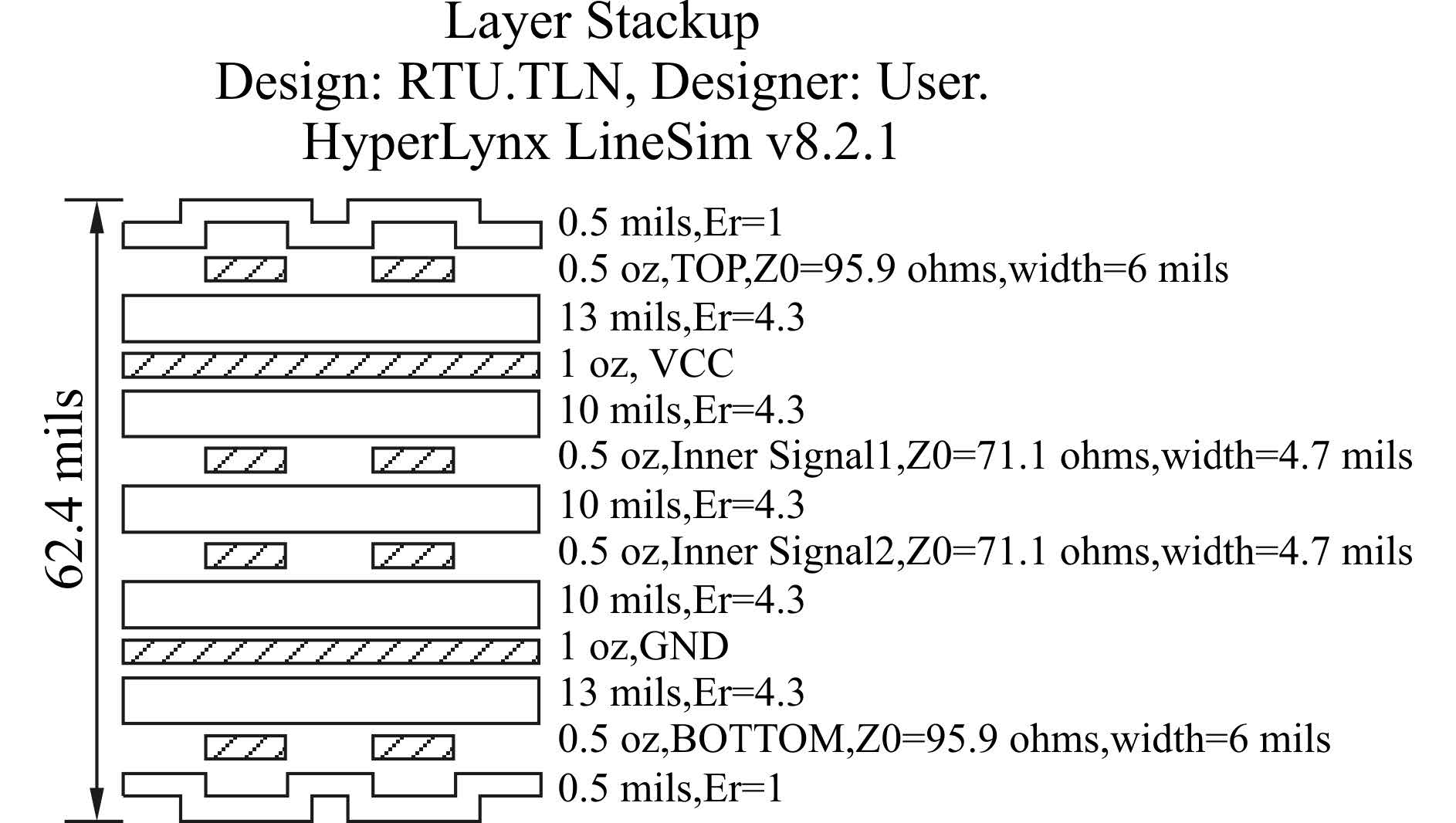

| 图 3 高速PCB叠层分布 |

在高速PCB设计中,信号路径的间距、线宽、线长和返回路径的具体结构将直接造成地弹和电磁干扰等问题。Hyper Lynx具有干扰图表分析功能,其LineSim模块可以在布线前对关键网络进行仿真,优化当前电路的PCB叠层结构和布线阻抗,在PCB设计之前制定高速网络的布线约束规则。

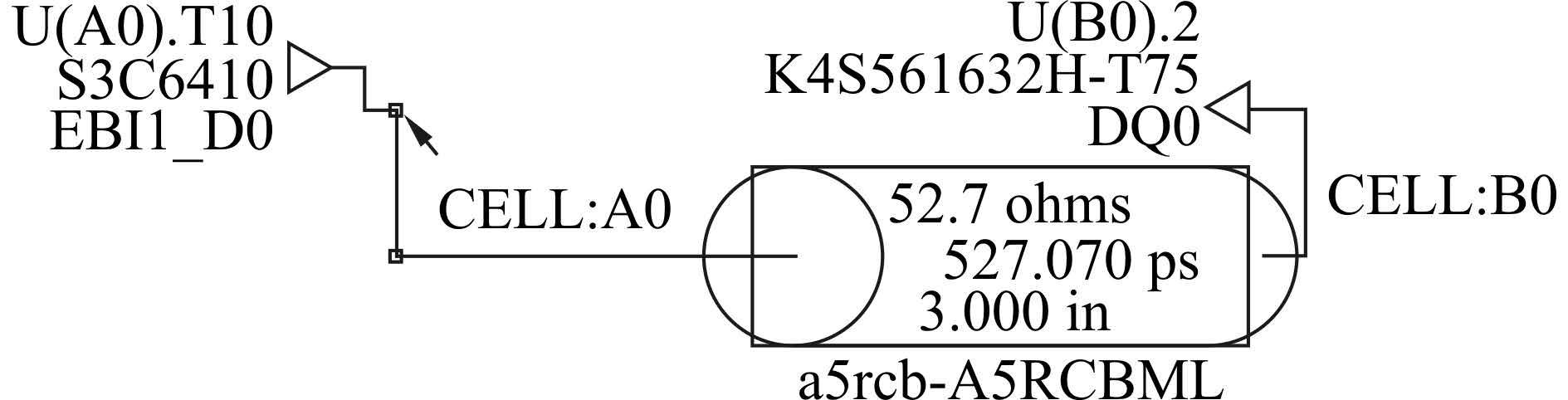

4.1 反射抑制单一网络的PCB布线长度和宽度的变化表现为传输线特征阻抗突变,出现反射和振荡噪声源,引发信号过冲或下冲,使整个系统产生误触发。如图 4是选取ARM11和SDRAM的关键信号线EBIO_D0-DQ0的LineSim原理图。

|

| 图 4 LineSim原理 |

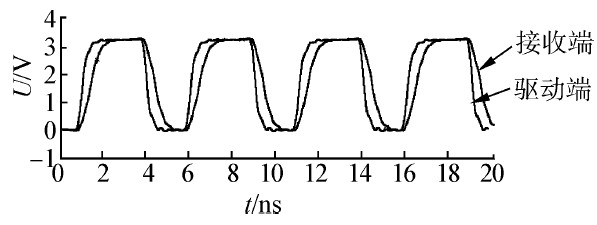

指派S3C6410的EBIO_D0管脚为驱动端,K4S561632H的DQ0管脚为接收端,传输线类型选择带状线,线宽4.7 mil,线长3 in,驱动端输入200 MHz激励源,如图 5所示为默认配置的“what-if”仿真结果。

|

| 图 5 传输线的反射仿真 |

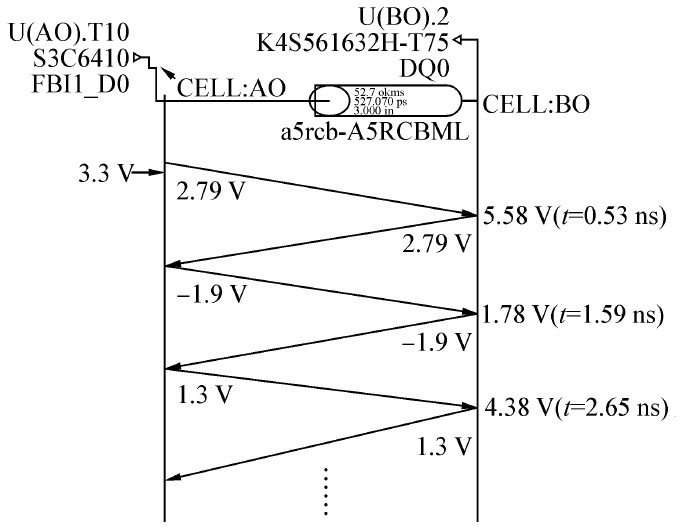

观察驱动端和接收端的电压波形有很大的振铃现象,显然不能设计这样拓扑的一根走线,否则将导致高频设计的失败,而且这样的波形将会引起很强的电磁辐射。驱动端的电压是3.3 V,I/O内阻是9.6 Ω,则实际进入延迟0.53 ns的52.7 Ω传输线的电压是2.79 V,这就是沿驱动端输入的初始电压。由于传输线末端是开路,0.53 ns后末端产生2.79 V反射信号,接收端的电压为5.58 V,如此继续发生多次反射,造成接收端电压波动,可以用反射图来表示,如图 6所示。

|

| 图 6 系统反射演示 |

实际上,传输延迟是由电场和磁场建立的快慢决定的,与传输线的长度及其周围介质的介电常数有关[3]。这些场的传播和相互作用可以用麦克斯韦方程来描述,只要电磁场在变化,形成的铰链电磁场就会向外传播,传输线的时延tD由下式得到:

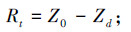

对于时序复杂,要求又很高的设计,需要遵循规则走线长度延迟不能超过速率的1/6,使用介电常数为4.3的FR-4板材,由式(1)得信号延迟是5.79 in/ns。查看驱动端IBIS文件中上升沿的时间为0.431 1/0.302 1 ns(大约1.4 ns),所以布线最大长度为1/6×1.4×5.79=1.35 in,通过不断试验,得到振铃较小的布线长度为0.35 in,但是仍然不能完全解决由于传输阻抗突变引起的过冲和下冲现象,振铃是由于驱动端内阻小于传输线的特征阻抗引起的,可以通过适当的端接方法减小[4]。串联端接法就是在驱动端或者接收端串接一个电阻,此电阻的最优值计算公式为

|

| 图 7 传输线端接后的反射仿真 |

串扰是指有害信号从一个网络转移到相邻的网络。不同网络间都存在容性耦合和感性耦合,给有害噪声从一个网络到达另一个网络提供了串扰路径 [1]。

网络之间的噪声容限通常占信号电压摆幅的15%,其中大约5%是与串扰有关的,若信号幅度是3.3 V,所以分配的最大串扰为165 mV,这是最大可容许的串扰噪声[5]。

在高速PCB电路中通过前面的仿真,制定了布线的长度、宽度等约束,要保证总线上的相互串扰不超过容限值,还要添加合适的布线约束条件。在LineSim原理图中配置三条关键信号线EBIO_D0-DQ0、EBIO_D1-DQ1、EBIO_D2-DQ2,与电源层和地层距离分别为10 mil和20 mil,线宽4.7 mil,间距10 mil,耦合布线长度0.35in,仿真结果如图 8所示。

|

| 图 8 LineSim串扰仿真 |

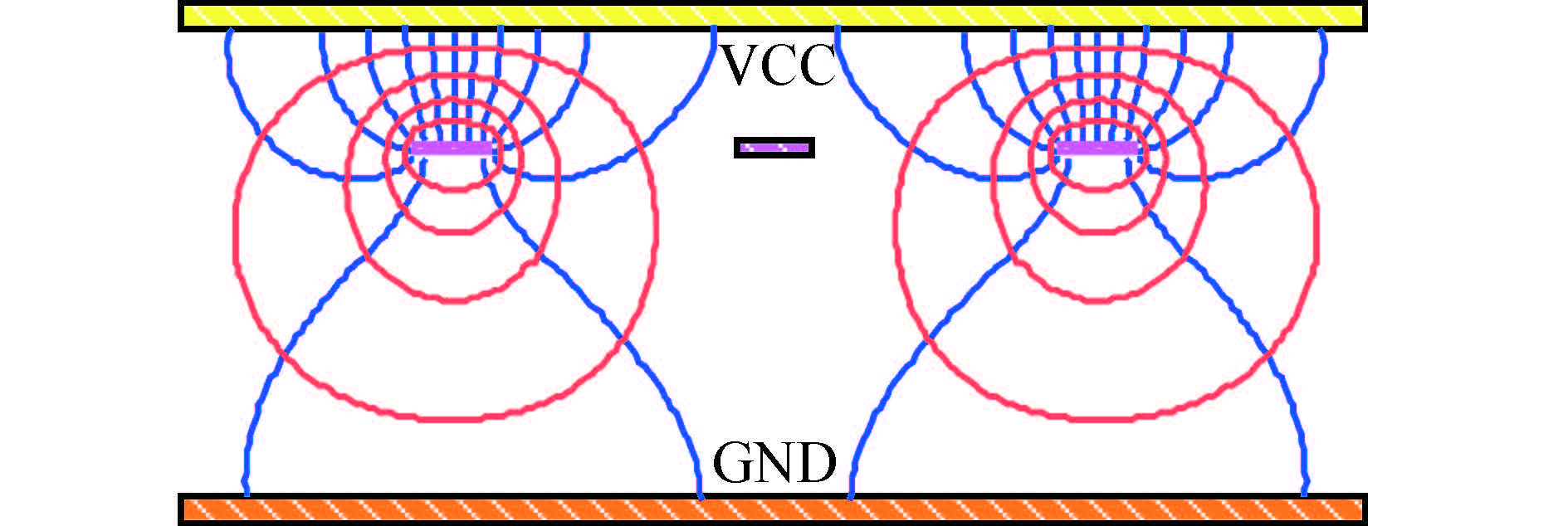

图中深色线代表关键信号线之间的电场线,浅色线代表磁场线,可见,串扰是容性耦合和感性耦合噪声的叠加[6]。理论上,增加三条带状线之间的间距可以减小串扰噪声,但是线间距的增大也增加了布线面积,因此,在不影响电路板尺寸的前提下,除了尽可能增大线间距,信号层也要尽量靠近参考平面,提供最近的返回路径。调整线间距为15 mil,内层带状线与电源层和地层距离分别为8 mil和18 mil,仿真波形如图 9所示。

|

| 图 9 调整后的LineSim串扰仿真 |

通过反射和串扰分析,确定的PCB布线规则为:线宽4.7 mil;线间距15 mil;走线长度0.35 in;串接电阻43.1 Ω;带状线与电源层和地层间距8 mil和18 mil。

5 电源完整性设计在混合模式系统中,电源噪声(power supply noise,PSN)包括数字电路的开关噪声(SSN)对模拟电路的危害越来越多,电源/地的分布在高速PCB设计中显得越发重要,因此必须提供高度可靠的混合系统设计。如图 10所示为该嵌入式电路系统的电源分布图,其中不同电源网络间距大于30 mil。

|

| 图 10 电源分布模型 |

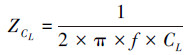

由于PCB感性电容CL的存在,实际电源分布系统的阻抗ZCL为

在直流或低频系统中,由于PCB感性电容的存在,阻抗成为不确定因素,因此只有寄生电阻起到作用。参照以上公式可知,加宽或者增厚电源走线的铜层能减小寄生电阻,从而起到减小电源分布系统的压降。通常允许的压降门阀是正常电压的5%,如图 11所示是该系统3.3 VD电源网络的分布情况。

|

| 图 11 系统3.3 VD电源网络分布图 |

综合分析6个层面的电源完整性,压降最大为0.4 mV,接近于0.012%,最大的电流密度为3.9 mA/mil2,这个值是可以的,一般电流密度大于50 mA/mil2会使电路板温度上升,对正在运行的关键元器件和传输线造成干扰。增加铜皮的宽度可有效降低电流密度,降低PCB板温度[7]。

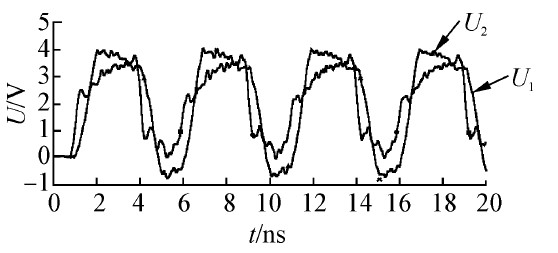

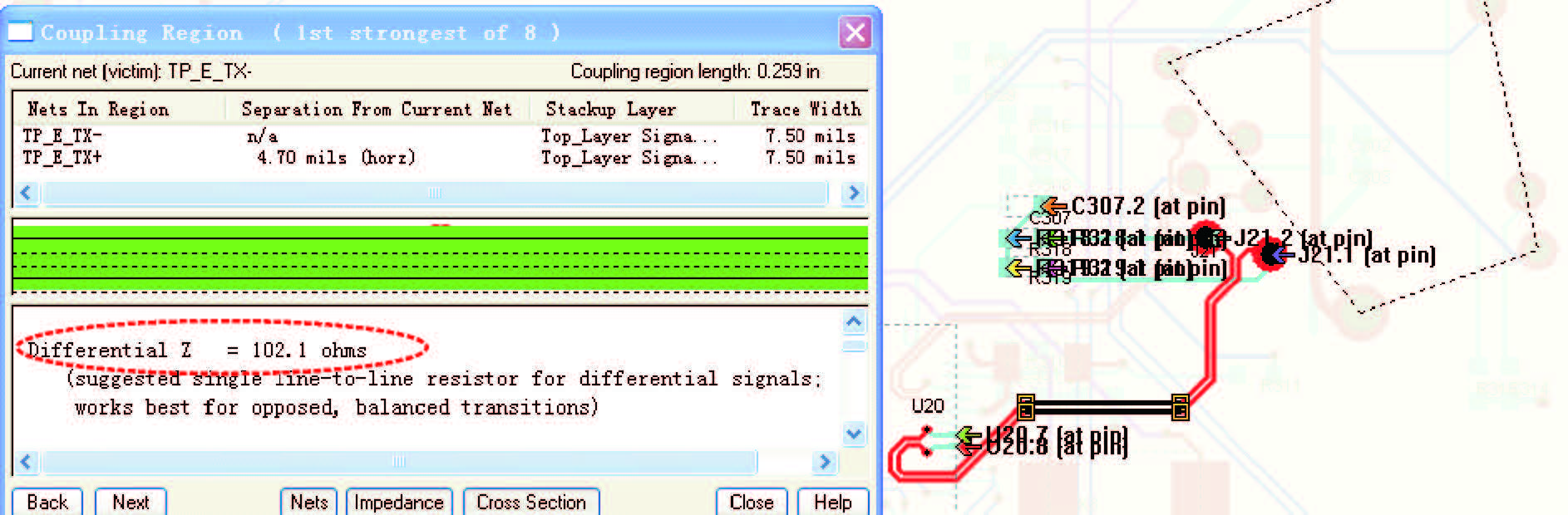

6 板级PCB仿真布线完成后,通过HyperLynx软件对整板PCB进行电磁兼容分析和仿真,再根据结果调整布局布线,改善PCB的电磁兼容性。在ARM11核心电路板的设计中,SDRAM的所有单端总线要求等长布线,为了让DM9000和DM9161网络控制器能够自适应100 Mb/s的通信速率,差分总线要求等长等间距布线,差分阻抗必须始终在(100±5)Ω。

6.1 SDRAM单端总线的设计串扰是产生时延的重要因素,在实际设计过程中,会遇到元器件管脚密度过大和布线空间不足等弊端,使用板级BoardSim进行后仿真是必要的。如图 12是对布线后的网络EBI_D1进行串扰仿真的结果。

|

| 图 12 SDRAM总线串扰仿真 |

两条被标示的虚线网络EBI_D0和EBI_D2的串扰强度超过165 mV,是对EBI_D1的攻击网络,查看耦合区域,是由于部分蛇形线间距太小。很明显,增大布线间距可以解决问题。然而攻击网络产生强干扰的原因很有可能是端接的电阻不适合实际布线的属性,没有达到阻抗匹配的效果。当前设计的串接电阻是43.1 Ω,提供200 MHz的激励,观察网络EBI_D1的仿真波形,如图 13所示。

|

| 图 13 BoardSim EBI_D1的仿真 |

将EBI_D0、EBI_D1、EBI_D1串接电阻修改为46.9 Ω,再次运行仿真,此时入侵网络和受害网络上的串扰波形如图 14所示,信号质量有所改善。

|

| 图 14 调整端接阻值后对EBI_D1的仿真 |

差分对是指一对存在耦合的传输线,差分信号利用这2个输出驱动来传输,一根携带信号,另一根携带它的互补信号,有用信号就是这2条传输线上的电压差,得到的信号是任何一个单端信号的2倍,所以,差分信号的信噪比较高[8]。

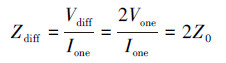

差分信号对EMI和串扰具有很强的抑制能力。2条差分线非常靠近,它们之间会相互耦合,外部噪声也会相同程度地耦合到差分对中的传输线上,由于差分信号的每条传输线对外的辐射是幅度相等而方向相反的,相互抵消后,对外的EMI辐射也会减小[9]。本设计中的网络控制器DM9000和DM9161都有2对高速差分总线: TX+ 、TX-和RX+、RX-,要求差分阻抗为100 Ω,根据阻抗的定义,差分信号的阻抗为

|

| 图 15 网络控制器差分阻抗仿真 |

本文设计的基于ARM11的远程网络通信双栈协议转接板,经过长时间多方面的测试,均能够稳定运行,发送和返回数据无误。把bootloader、内核和文件系统下载到设计好的PCB板,PC机连接ARM11的调试串口,给电路板上电,在终端用ifconfig eth0命令查看电路板的IP地址为192.168.1.10,用ping命令与IP地址为192.168.1.66的Redhat虚拟机进行数据通信,在Redhat平台用Wireshark工具监控网络通信数据包丢失率为0。说明利用HyperLynx仿真工具能够有效地辅助完成高速PCB的设计,对反射、串扰、EMI和差分总线匹配控制等影响信号完整性问题有明显的抑制效果。

| [1] | BOGATIN E.信号完整性分析[M].李玉山,李丽平,译.北京:电子工业出版社,2006:6-127. |

| [2] | 邵鹏.信号/电源完整性仿真分析与实践[M].北京:电子工业出版社,2013:90. |

| [3] | 曾峰,巩海洪,陈洪霞.PADS 9.0高速电路PCB设计与应用[M].北京:电子工业出版社,2010:347-400. |

| [4] | 周润景,景晓松,赵俊奇.OrCAD & PADS高速电路板设计与仿真[M].北京:电子工业出版社,2007:531. |

| [5] | 姜宏丰.高速PCB电路中噪声抑制的分析与研究[D].西安:西安电子科技大学,2014:12-15. |

| [6] | 李颖宏,罗勇.PCB设计中同步开关噪声问题分析[J].电讯技术,2012,52(3):395-399. |

| [7] | TANG Zhanghong.Hotspot detection by improved adaptive finite element method and its application in high-speed PCB and IC package design[J].IEEE transactions on components,packaging and manufacturing technology,2012,2(2):1659-1665. |

| [8] | 满宇航,魏金军,马永光.配网自动化仿真系统智能重合器与分段器设计[J].电力科学与工程,2012,27(12):40-44. |

| [9] | 倪胜.ARM11高速电路设计与仿真[D].武汉:华中师范大学,2012:16-17. |

| [10] | 朱亚地.高速PCB信号反射及串扰仿真分析[D].西安:西安电子科技大学,2012:30-32. |

| [11] | 李程贵,张学谦,马德华,等.基于ARM9的智能家居网关的设计[J].科技创新导报,2011(15):20. |