近年来,随着各行各业对监控范围、监控点数、监控质量、监控场景的要求越来越高,未来的监控系统必须能提供更多的功能才能满足应用需求[1, 2]。而全景监控就是在这一背景下发展起来的一项新技术。

本文从监控需求的角度出发,研究了一种基于FPGA的定点360°全景监控系统的设计方案[3]。设计在FPGA内部采用双NIOS II软核架构来完成全景视频数据的采集和网络传输,以实现远程网络监控。同时,借助于FPGA内部丰富的硬件资源,实现了视频数据的本地VGA播放。在一片FPGA内使用2个CPU核,并结合VHDL编写的硬件模块,实现高速并行处理,大大提高了系统的工作效率。

1 系统总体设计

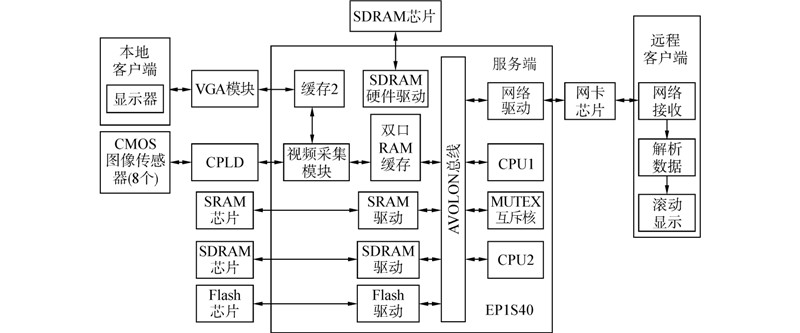

本文所提出的全景监控系统主要包括3大部分:8个CMOS图像传感器与CPLD连接的硬件设计、FPGA监控服务端、PC监控客户端。设计主要基于Altera公司提供的开发板,该开发板的核心芯片为Stratix系列的EP1S40型号的FPGA。设计总体框图如图 1所示。由于设计中采用的8个CMOS图像传感器为并行8 bit数据输出,接收所需要的IO口较多,因此为了节省FPGA的IO口资源,在FPGA和图像传感器之间加入了一片CPLD,型号为EPM1270,先对8个摄像头采集的视频数据进行并转串处理,然后再送给FPGA。

|

| 图 1 系统总体设计框图 |

由图 1可以看出,视频数据进入FPGA之后进行了2种处理:1)通过SDRAM缓存送给由ADV7123和VGA接口构成的VGA模块,可以直接外接CRT显示器进行播放,也就是本地常规监控,该部分所有模块均采用VHDL语言编写[4, 5]。2)通过2个双口RAM进行乒乓缓存,再送给由2个NIOS II软核和相应外设构成的SOPC系统,其中CPU1主要负责视频数据接收和存储,CPU2中移植嵌入式操作系统μC/OS-II负责读取缓存数据并进行网络传输[6]。该部分中的SRAM、SDRAM、FLASH控制器直接调用IP核进行驱动,其中SDRAM和FLASH存储系统程序和相关系统数据,SRAM作为图像数据的存储,利用MUTEX互斥核协调2个CPU对该资源的共享和控制。远程客户端采用PC机接收视频数据并进行全景视频滚动实时播放。

2 全景视频采集和处理 2.1 全景视频采集总体设计

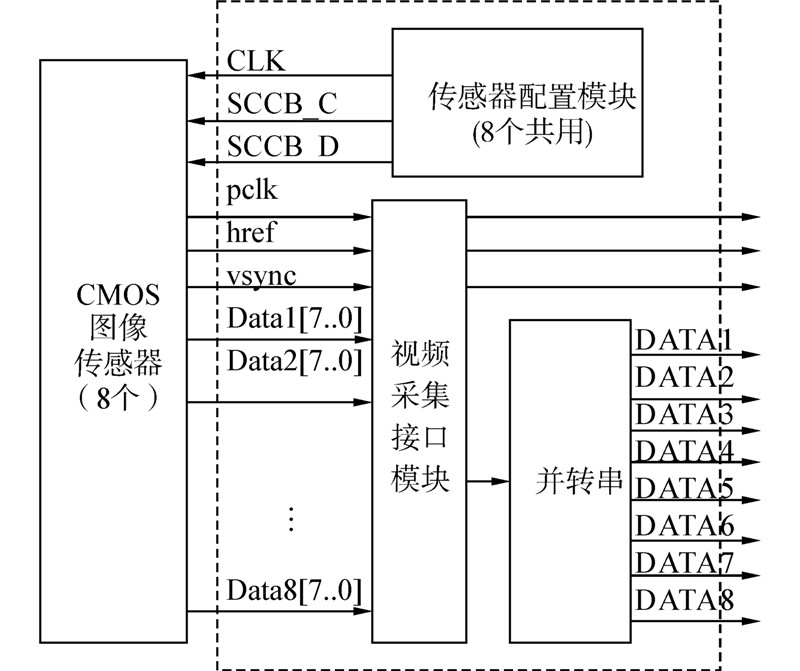

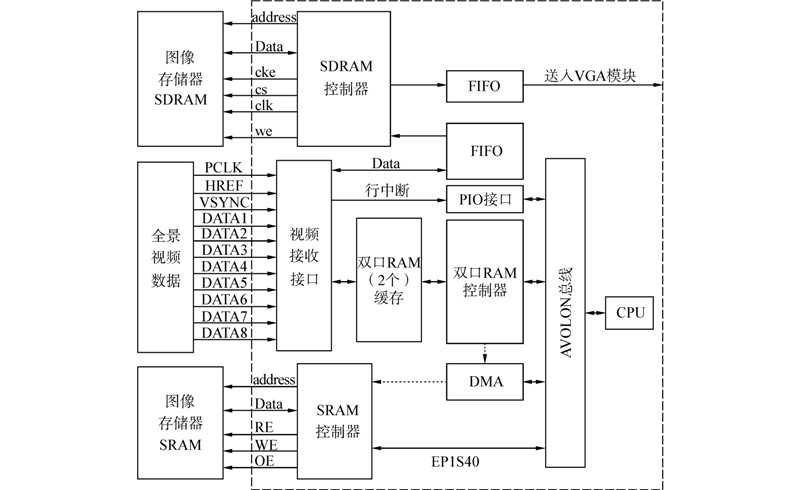

8个CMOS图像传感器与CPLD的硬件结构图如图 2所示,可以看出,CPLD主要控制IO口输出SCCB时序同时初始化8个CMOS图像传感器OV9650,初始化完毕之后,开始接收视频数据并对其进行并转串处理,之后和OV9650输出的一组行同步信号HREF、帧同步信号VSYNC和像素时钟PCLK同时送给FPGA。在FPGA内的硬件结构图如图 3所示。由图 3可以看出,视频数据经过CPLD预处理输入FPGA之后,采用2种方式存储。一种直接通过异步FIFO存入SDRAM,然后又通过异步FIFO即可送入VGA模块进行本地播放,该处采用异步FIFO是为了实现跨时钟处理数据。另一种采用SOPC系统,先在行同步信号HREF有效时将全景视频数据的第一行存入第1个RAM,在下一个HREF有效时将下一行视频数据存入第2个RAM,与此同时,CPU通过PIO接口捕获中断并将第1个RAM中的视频数据存入外部SRAM,等待下一个中断再将第2个RAM中的视频数据存入SRAM,如此乒乓操作再读取缓存直到存储完一整幅全景图像。

|

| 图 2 CPLD与图像传感器的设计框图 |

|

| 图 3 FPGA内部硬件设计框图 |

2.2 图像传感器

该设计采用美国OmniVision公司生产的CMOS图像传感器OV9650,其最高分辨率可达到1 280 pix×1 024 pix,支持YUV和RGB输出格式。本设计采用分辨率640 pix×480 pix,YUV422格式输出。

OV9650通过SCCB接口配置内部各个寄存器来控制图像输出模式,SCCB总线类似I2C串行总线,是OmniVision公司定义的一套串行总线标准。设计采用CPLD的IO口模拟串行时钟线SCCB_C和串行数据线SCCB_D对OV9650进行配置。部分寄存器含义如表 1所示。

| 寄存器名称 | 取值含义描述 |

| COM7 | 视频帧格式选择:VGA、QVGA等 |

| TSLB | YUV输出顺序选择 |

| COM15 | 像素值取值范围 |

| AECHM | 曝光值设定 |

| CLKRC | 内部时钟设置 |

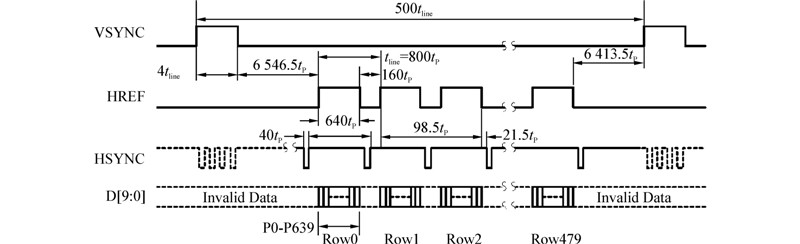

OV9650正确配置之后即可输出视频数据,其输出时序图如图 4所示。

|

| 图 4 视频数据输出时序图 |

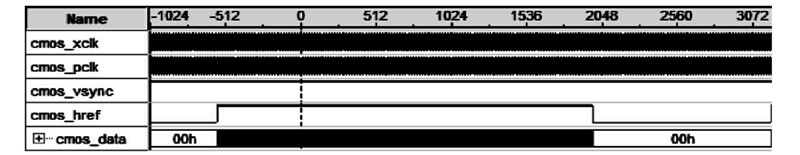

图 4是OmniVision公司给出的VGA模式输出时序图,本设计中采用YUV422像素格式输出,每个像素有16 bit数据,设计的图像采集接口就是在HREF和VSYNC有效时接收数据,其仿真波形如图 5所示。

|

| 图 5 视频输出仿真波形 |

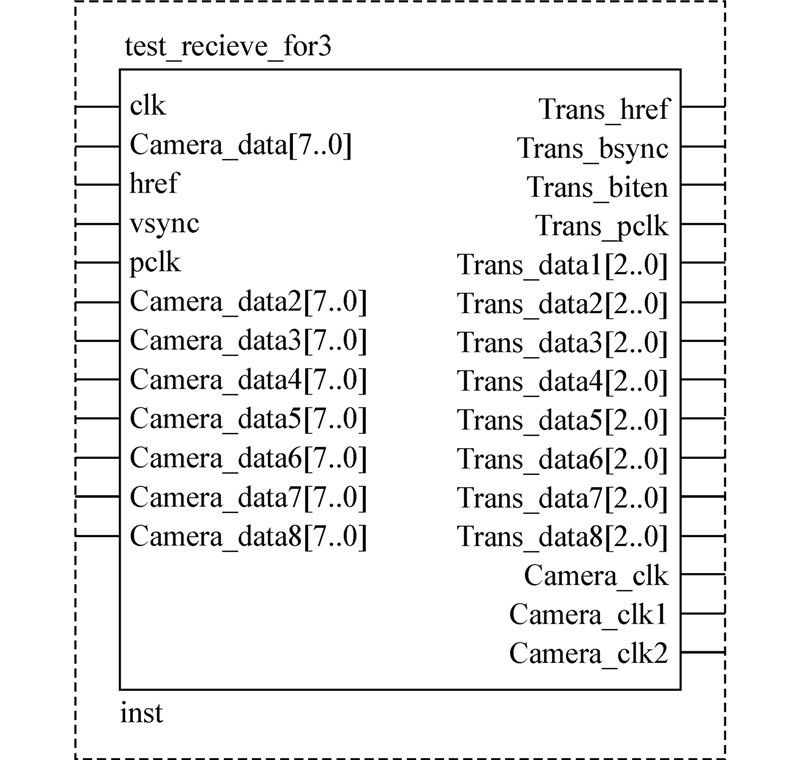

8路视频数据进入CPLD之后进行并转串,其模块如图 6所示。经过并转串即可连同VSYNC、HREF和CMOS_CLK输入到FPGA进行进一步处理。

|

| 图 6 并转串模块 |

2.4 视频数据缓存 2.4.1 SRAM缓存

视频数据送入FPGA之后分成2路处理,一路配合基于NIOS II的SOPC系统完成远程监控功能,该部分前端采用2个双口RAM对视频数据进行乒乓缓存,其模块如图 7所示。然后SOPC系统通过定制的双口RAM控制器对外部2个双口RAM进行乒乓读取并存储到外部SRAM中相应的内存区间。

|

| 图 7 前端缓存模块 |

2.4.2 SDRAM缓存

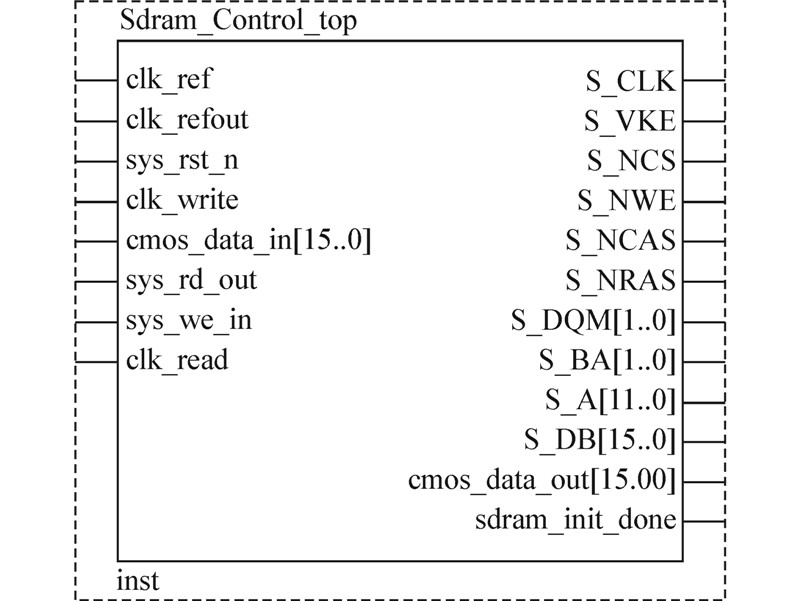

为了实现本地常规监控,在视频数据进入FPGA之后分出一路存入SDRAM中。其具体模块如图 8所示。

|

| 图 8 SDRAM控制模块 |

本设计中SDRAM工作频率为100 MHz,由于其他模块不能达到这么高的速度,因此设计采用添加异步FIFO来实现不同时钟域数据的处理。同时,结合SDRAM特殊的物理结构,其含有4个Bank存储区,因此在存储视频数据时也可采用乒乓操作,以提高系统的资源利用率,如图 9所示。

|

| 图 9 SDRAM乒乓操作 |

3 远程监控的实现 3.1 网络传输

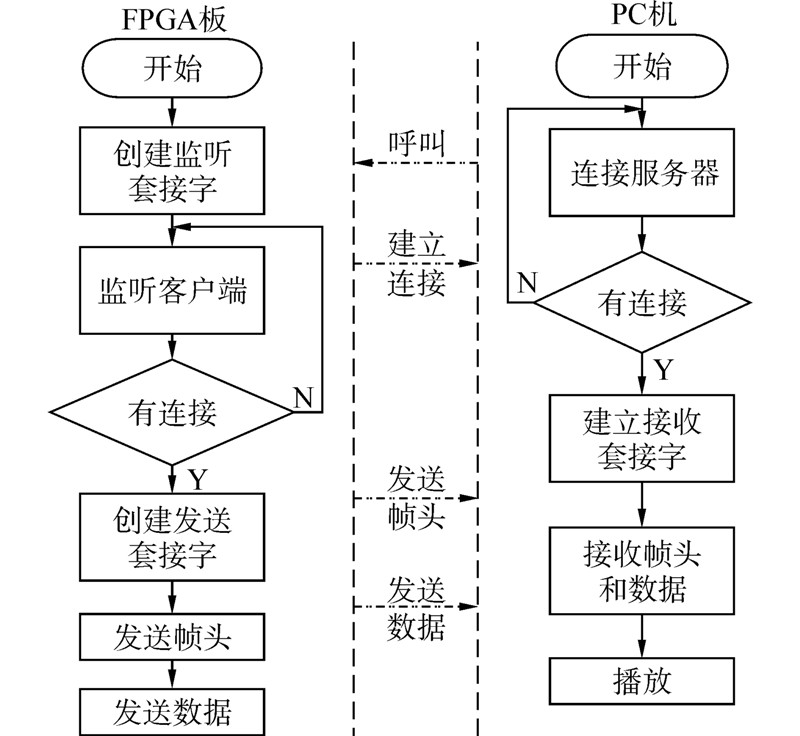

由图 1可以知道,该系统采用了基于双NIOS II软核的SOPC系统,在其中一个CPU中移植支持LWIP协议的μC/OS-II内核[7],在此内核中采用SOCKET编程[8, 9],将存储在SRAM中的视频数据进行网络传输。如图 10为监控服务端和客户端的通信模式流程图。

|

| 图 10 FPGA和PC机的程序流程图 |

3.2 远程监控测试

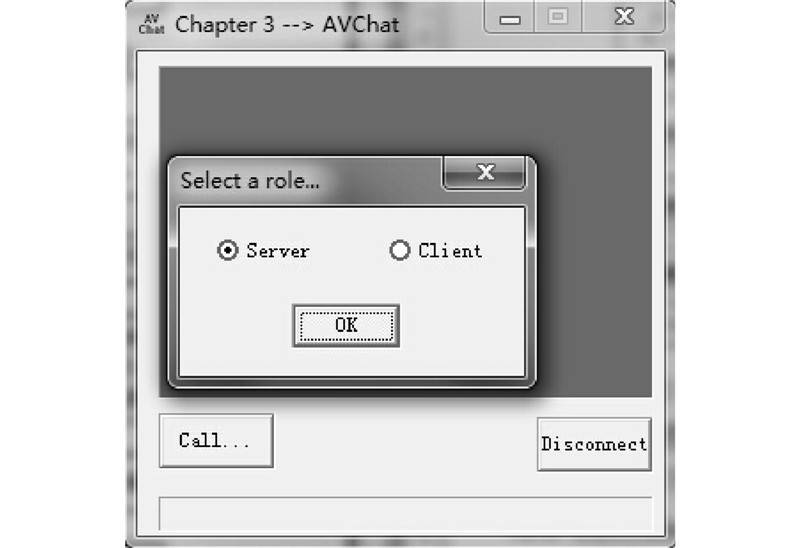

PC机客户端选择Visual C++ 6.0为开发环境,并结合Directshow强大的流媒体处理能力,开发出视频接收应用程序,如图 11所示。至于如何利用Directshow进行应用程序开发参见文献[10]。

|

| 图 11 接收应用程序效果 |

PC机与FPGA建立连接后即开始接收视频数据并实时播放。本设计采用的播放方式为滚动式播放,即将采集的360°全景视频看成是一维的,宽度为640 pix×8 pix,高度为480 pixels,从左到右滚动播放,测试效果图如图 12所示。

|

| 图 12 远程监控测试 |

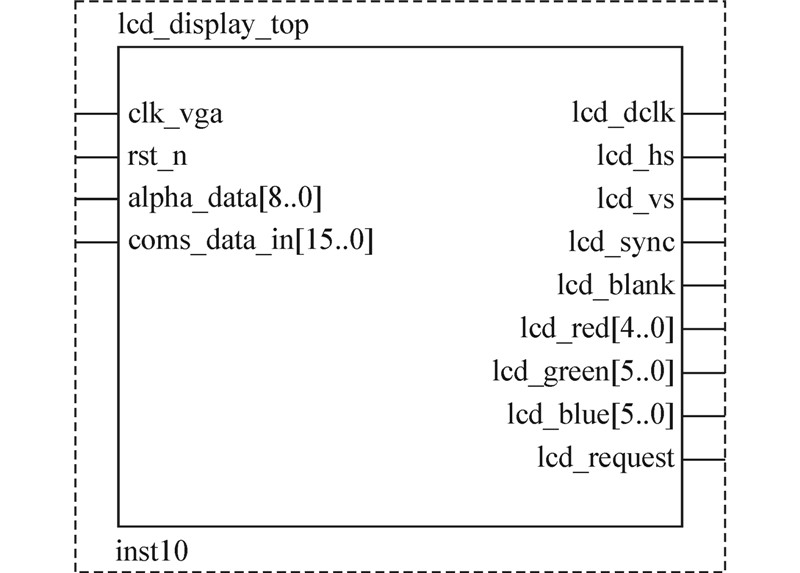

4 本地监控的实现 4.1 YUV422转RGB565

由于CMOS图像传感器输出的视频数据格式为YUV422,而VGA播放需要的是RGB格式数据,因此在存入SDRAM之前要进行数据转换[11]。设计转换思路为流水线处理,先将YUV422转成YUV444,再将YUV444转成RGB888,再转成RGB565,均由VHDL语言编写,其生成顶层模块如图 13所示。

|

| 图 13 YUV422转RGB565顶层模块 |

4.2 VGA控制器

VGA支持多种分辨率,不同分辨率有不同的时序,本设计采用640*480@60 Hz下的VGA分辨率[12]。结合该分辨率下的VGA时序,采用VHDL语言编写的VGA控制器模块如图 14所示。视频数据经由SDRAM缓存之后即送入该控制器。

|

| 图 14 VGA控制器 |

由于VGA接口只有3根数据线,即R、G、B模拟输出,若直接输入最多只能显示8种颜色,因此设计使用了视频转换芯片ADV7123,该芯片具有3通道10位DAC接口,转换速度达到140 MHz。本设计将ADV7123低位接地即可实现RGB565真彩数据的转换。

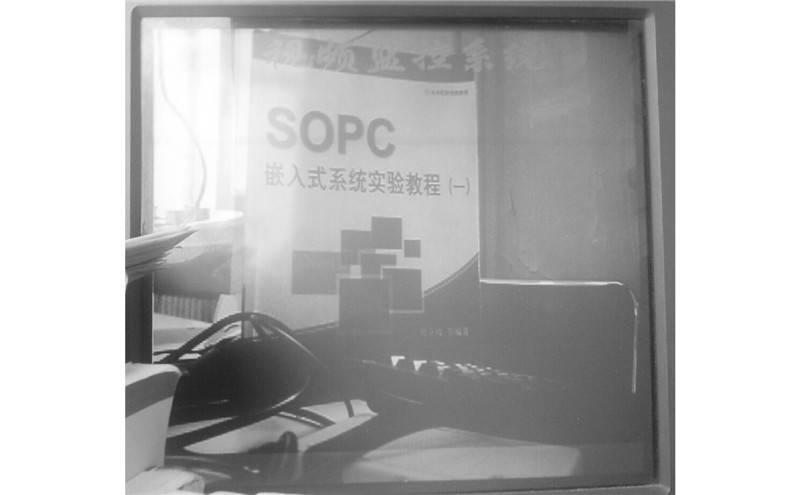

4.3 本地监控测试

视频数据经过ADV7123转换成真彩数据之后,利用任一台有VGA接口的显示器接上即可播放。设计中由于SDRAM存储空间有限,每次只能存储一个摄像头的数据,因此在播放时采用了按键选择功能,即通过按键来控制8个中任意一个摄像头的当前显示。测试效果如图 15所示。

|

| 图 15 本地VGA播放效果 |

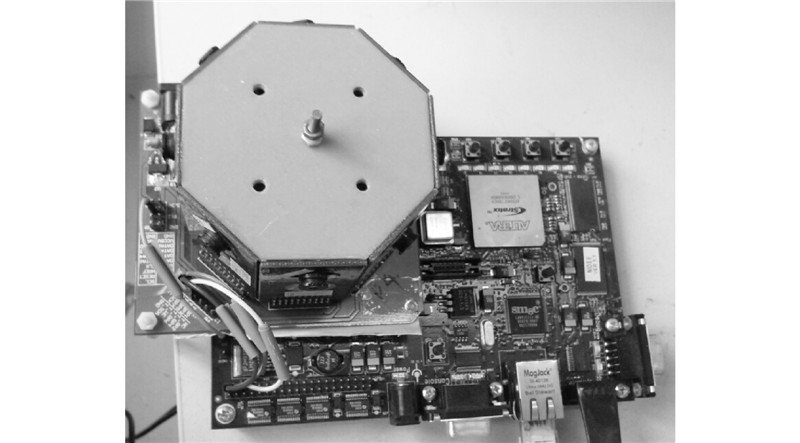

本文所设计的基于FPGA的全景监控系统实物如图 16所示。

|

| 图 16 全景监控系统实物 |

5 结束语 5 结束语

系统给出了全景视频数据及其网络传输的一种实现方案,采用的基于双NIOS II架构的SOPC并行处理方法具有稳定性高、处理效率高等优点。设计充分利用FPGA内部资源,同时实现了远程监控和本地常规监控,实验结果表明该系统具有良好的监控效果和监控质量。

| [1] | 田振华. 视频监控发展与趋势[J]. 中国公共安全, 2013 (19): 108-109. |

| [2] | 李立仁, 李少军, 刘忠领. 智能视频监控技术综述[J]. 中国安防, 2009(10): 90-95. |

| [3] | 肖潇, 杨国光. 全景成像技术的现状和进展[J]. 光学仪器,2007(4): 84-89. |

| [4] | 吴蓬勃, 张启民, 王朝阳, 等. 基于FPGA的VGA图像控制器设计[J]. 东北电力大学学报, 2006(4): 89-92. |

| [5] | 熊文彬, 蒋泉, 曲建军, 等. 基于FPGA实现的视频显示系统[J]. 液晶与显示, 2011, 26(1): 92-95. |

| [6] | ALTERA. Using MicroC/OS- II RTOS with the Nios II Processor Turorial [EB/OL]. [2014-09-20]. https:// www.altera.com. |

| [7] | 周立功. SOPC嵌入式系统实验教程[M]. 北京: 北京航空航天大学出版社, 2006: 16-176. |

| [8] | 焦铬, 易小波, 李仁发. 基于嵌入式Internet的远程视频监控系统设计[J]. 计算机技术与发展, 2009(5): 176-179. |

| [9] | 韩秋凤, 肖政宏. 嵌入式远程视频监控系统的设计与实现[J]. 湖南文理学院学报: 自然科学版, 2005(3): 72-74, 77. |

| [10] | 路其明. DirectShow开发指南[M]. 北京: 清华大学出版社, 2003: 16-108. |

| [11] | 邵丹, 韩家伟. YUV与RGB之间的转换[J]. 长春大学学报, 2004(4): 51-53. |

| [12] | 郑美芳, 高晓蓉, 王黎, 等. 基于FPGA的VGA时序彩条信号实现[J]. 现代电子技术, 2009(14): 90-92. |