2. University of Chinese Academy of Sciences, Beijing 100049, China

高速大面阵图像传感系统目前具有广泛的应用前景。在工程科技领域,工程人员利用高速相机记录汽车碰撞瞬间各部位的变化以及人体模型的受力情况,从而分析和改进汽车设计的薄弱环节。在体育竞技领域,裁判利用高速相机记录运动员的技术特点,有针对性的改进训练方法[1]。在天文科学领域,科学家利用大面阵高速CMOS探测器实现天文导星观测。为了实现大面阵高速图像获取功能,要求系统具有很高的传输带宽,高带宽往往伴随着数据传输速率和时钟频率的提高,信号的上升沿和下降沿的变陡,信号完整性的问题逐渐突出[2]。近年来,一些学者对信号完整性的理论进行了研究。堵军等[3]研究了信号完整性问题中的反射、串扰和电源系统的的完整性产生原理,并总结出了相应的设计规则。周路等[4]从理论上分析并得出上升或下降时间是造成反射、串扰、同步开关噪声及电磁干扰等信号完整性问题的根本原因这一结论,并通过仿真进行了验证。张吉等[5]分析了串扰的产生、串扰对信号的影响等,然后通过理论分析得出串扰的控制和减弱方法。针对该系统设计中关键信号的信号完整性开展仿真分析研究对于提高硬件设计成功率并降低系统开发风险具有十分重要的工程应用价值。

1 信号完整性的含义和影响

信号完整性指的是在高速电子产品设计中由互连线引起的所有问题,它主要研究互连线与数字信号的电压电流波形相互作用时其电气特性参数如何影响产品的性能[6]。本文从反射和串扰两方面来考虑信号完整性可能引入的后果。

信号在传播过程中,如果瞬时阻抗发生突变,则信号中有一部分能量会向源端方向反射,另一部分则继续向前传播。在阻抗突变处的电压连续,故反射电压与原信号电压叠加后等于继续向前传播的电压,即向前传播的电压与原信号相比产生失真。如果向源端传播的反射信号在传播过程中同样遇到了阻抗不连续的情况,则反射信号会再一次产生反射,最终由信号的多次反射而产生了“振铃”现象。

串扰是指当信号在传输线上传播时,相邻的信号之间由于电磁场的相互耦合,一根传输线上的信号能量耦合到另一根传输线上而产生的噪声电压。一般用两个相邻导体之间的互容Cm和互感Lm来描述串扰模型[7]。串扰分为前向串扰和后向串扰,前向串扰是指和攻击信号传输方向一致的串扰信号,后向串扰是指和攻击信号传输方向相反的串扰信号。

2 系统组成和信号完整性要求 2.1 系统组成

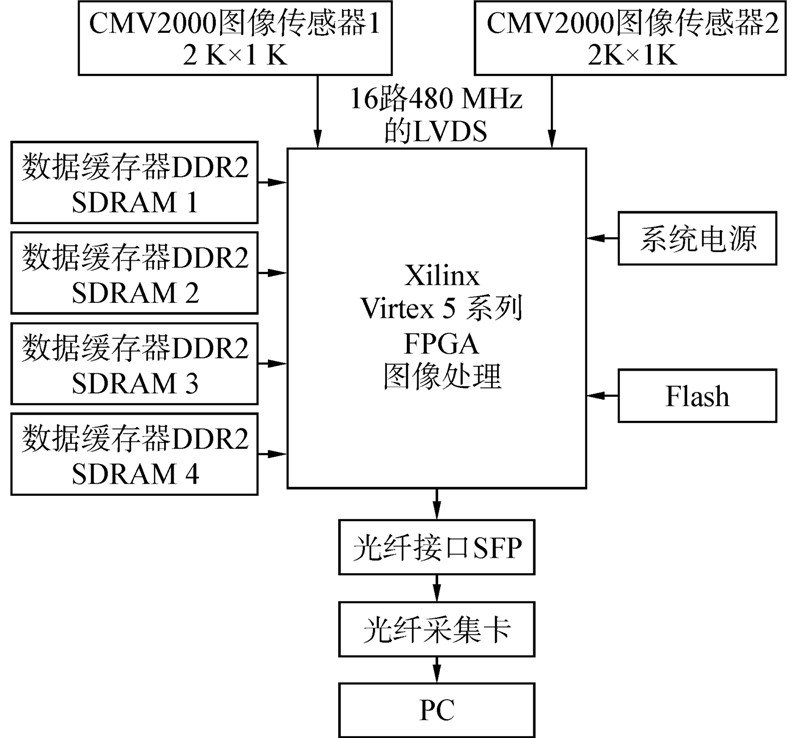

CMV2000探测器的图像读出接口为16路速率为480 Mbit/s的低电压差分信号(low-voltage differential signal,LVDS),当两片CMV2000同时输出时,数据瞬时带宽达到1.92 GB。系统选用Xilinx公司型号为XC5VSX240T的FPGA作为图像采集和处理的控制核心,由于FPGA内部的RAM资源有限,要对数据进行缓存,必须外接缓存器。系统选用4片Micro公司型号为MT47H64M16,速率为533 Mbit/s的16位DDR2 SDRAM两两一组,组成2组32位的缓存器,每组缓存器的带宽超过2 GB,可以满足探测器瞬时带宽的要求。系统硬件简化连接框图如图 1所示。

|

| 图 1 系统硬件简化连接框图 |

2.2 信号完整性与初步分析要求

DDR2 SDRAM技术文档规定,MT47H64M16数据总线引脚所允许的最大上冲电压为VDDQ+0.5 V,最大下冲电压为VSSQ-0.5 V,其中VDDQ是其数据总线供电电压(1.8 V),VSSQ为其数据总线参考地电压(0 V)。应该确保信号反射引起的上冲和下冲在-0.5~2.3 V之内,数据总线引脚上的电压不能超出这个范围。数据总线的高电平门限电压为VREF+0.25 V,低电平门限电压为VREF-0.25 V,其中VREF为数据总线的参考电平(0.9 V)。应该确保噪声和串扰电压叠加到信号线上之后,不会影响到门限电压对高低电平的判断,即低电平叠加噪声和串扰之后,其峰值不会大于0.65 V,高电平叠加噪声和串扰之后,其峰值不会小于1.15 V。

根据所选FPGA的相关技术文档,得知FPGA与DDR2 SDRAM数据总线相连的引脚电平类型为SSTL18-II,该类型电平所允许的最大上冲电压为VCCO+0.3 V,最大下冲电压为-0.3 V,其中VCCO是FPGA针对SSTL18-II电平引脚的驱动电压(1.8 V)。因此要确保输入到FPGA引脚的电压在-0.3~2.1 V。SSTL18-II高电平门限电压为VREF+0.125 V,低电平电压门限为VREF-0.125 V,其中VREF是参考电平(0.9 V)。应该确保噪声和串扰叠加之后不会对高低电平的判断造成影响。即低电平叠加噪声和串扰之后,其峰值不会大于0.775 V,高电平叠加噪声和串扰之后,其峰值不会小于1.025 V。

3 信号完整性仿真

3.1 仿真模型

为了进行后续仿真,首先要将MT47H64M16和XC5VSX240T的仿真模型与印制电路板(printed circuit board,PCB)中的器件相对应,然后提取DDR2 SDRAM的数据线与FPGA相连的实际拓扑结构。Cadence公司仿真工具使用的器件模型是DML模型,并且提供了将其他模型如IBIS模型、HSPICE模型、ESPICE模型等转换为DML模型的工具Model Integrity。由于SPICE模型会涉及芯片设计的细节,且仿真时间较长,故目前使用比较多的是IBIS模型,IBIS模型不会像SPICE模型一样存在版权问题,而且在保证精度的基础上仿真速度比SPICE模型更快[8]。MT47H64M16的IBIS模型可从Micron公司官网上下载,XC5VSX240T的IBIS模型可以通过Xilinx公司的ISE软件生成,根据不同的管脚设置生成不同的模型。

3.2 仿真流程

印刷电路板的仿真分析是一个反馈调节的过程。对电路板上关键信号进行必要的仿真,根据仿真结果来调整设计参数,直到仿真结果满足器件和系统的指标要求。文中着重对系统中FPGA和DDR2 SDRAM数据线的互联进行反射和串扰仿真,仿真流程如图 2所示。

|

| 图 2 仿真流程图 |

3.3 不使用匹配方式时的反射仿真

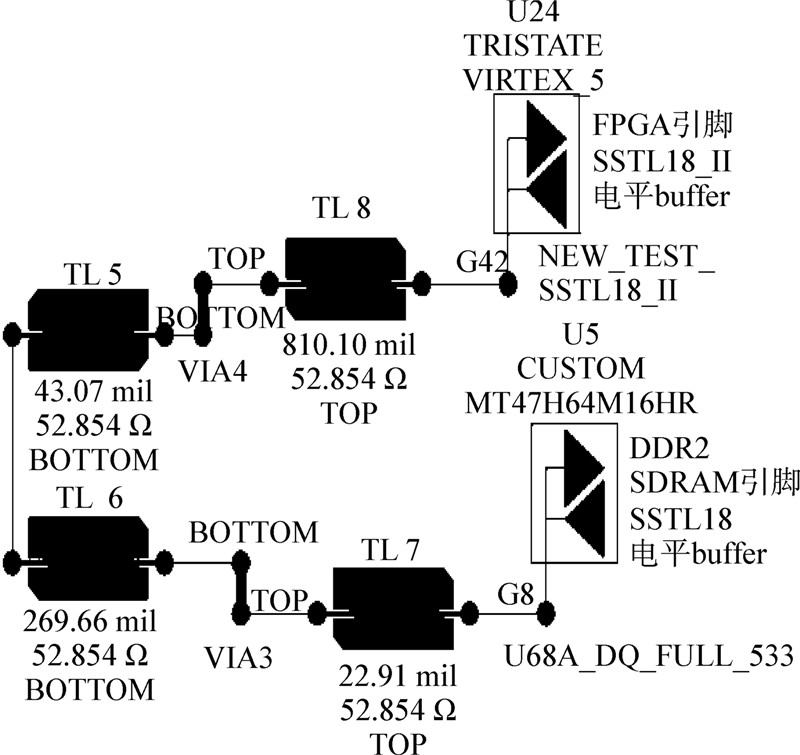

在进行阻抗匹配设计时,总是首先考虑在不做匹配的情况下设计是否满足要求,尽可能地减少外围器件数量或降低设计难度。从PCB中提取出来的无匹配的单一数据线拓扑结构如图 3所示。

|

| 图 3 无匹配时提取到的拓扑结构 |

其中TL5、TL6、TL7、TL8为传输线模型,VIA3、VIA4为过孔模型,U5和U24分别为 DDR2 SDRAM数据线管脚和与其相连的FPGA管脚的缓冲器模型。传输线以微带线的形式走在顶层和底层,线宽为8 mil,顶层和底层到与之相邻的地层的材料均选用FR4,厚度为5 mil,软件计算出来的走线阻抗约为53 Ω。

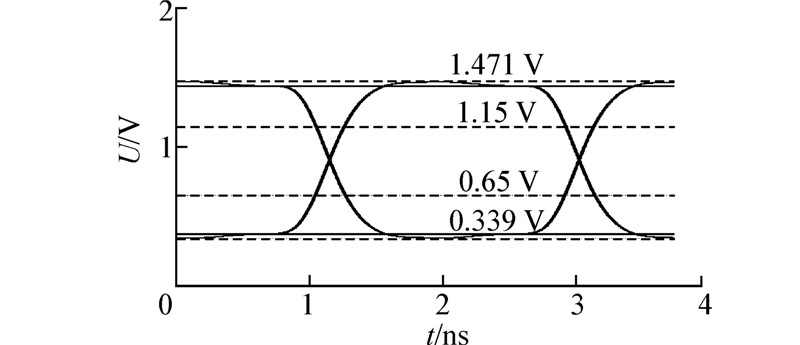

在FPGA管脚缓冲器模型上加533 Mbit/s的随机数据激励(模拟DDR2 SDRAM的写操作),在DDR2 SDRAM数据线管脚缓冲器端得到的信号波形眼图如图 4所示。

|

| 图 4 无匹配时写时序的数据总线波形眼图 |

由图 4的仿真结果可知,DDR2 SDRAM写操作时数据线波形的最大上冲电压为2.505 V,最大下冲电压为-0.67 V。其上冲电压和下冲电压都超过了DDR2 SDRAM数据线管脚所允许的最大电压值。

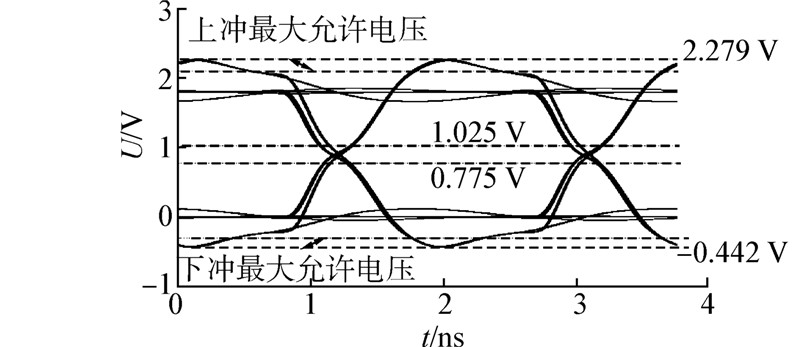

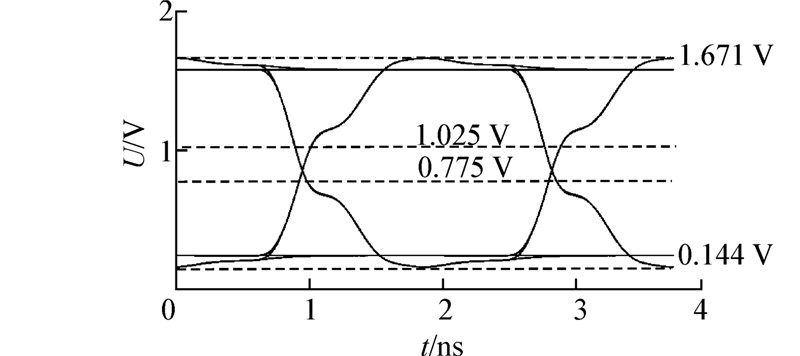

在DDR2 SDRAM数据线管脚的缓冲器模型上加533 Mbit/s的随机数据激励(模拟DDR2 SDRAM的读操作),在FPGA管脚缓冲器端得到的信号波形眼图如图 5所示。

|

| 图 5 无匹配时读时序的数据总线波形眼图 |

由图 5的仿真结果可知,DDR2 SDRAM写操作时数据线波形的最大上冲为2.279 V,最大下冲为-0.442 V,其上冲电压和下冲电压都超过了FPGA数据线管脚所允许的最大电压值。

3.4 采用DDR2 SDRAM和FPGA片上电阻匹配时的反射仿真

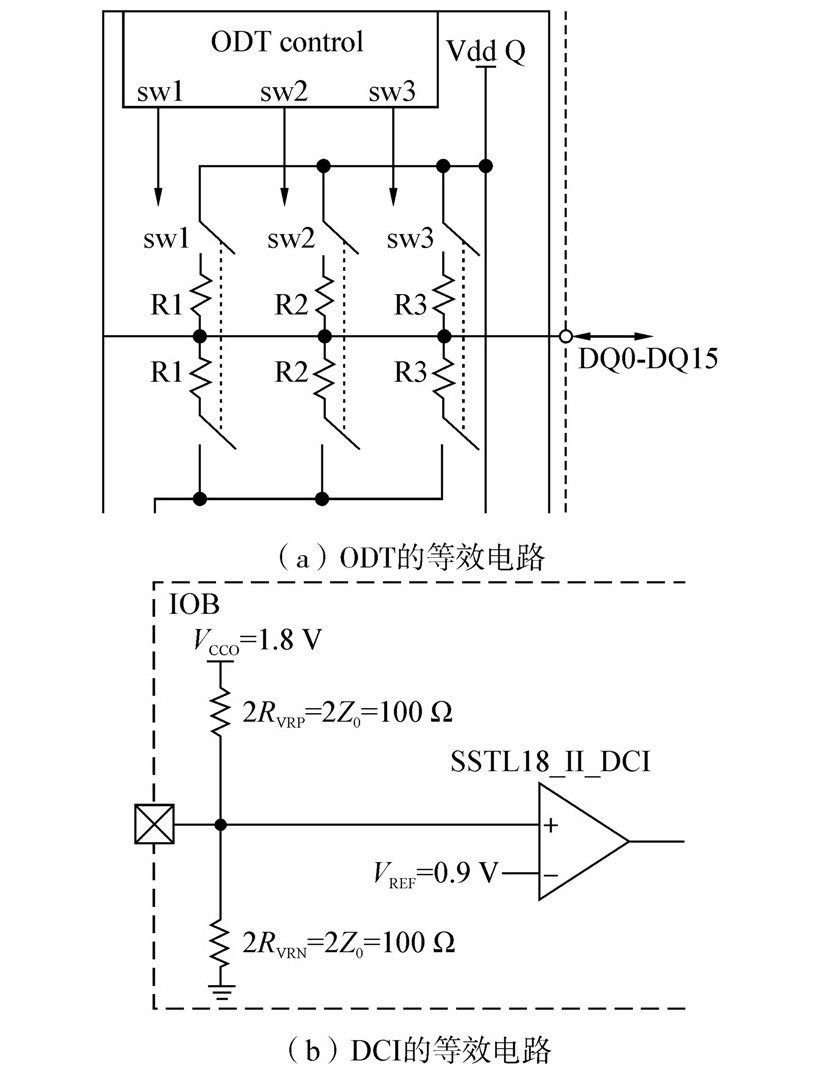

DDR2 SDRAM比上一代的动态存储器芯片DDR SDRAM具有的优势之一是其数据线DQ和数据采样时钟线DQS都具有ODT功能,省去了DDR2 SDRAM作为接收器时的终端匹配电阻,匹配电阻的阻值可在50、75、150 Ω之中选择。而Virtex5系列FPGA的DCI技术也使FPGA在作为接收器时省去了终端匹配电阻。

ODT技术和DCI技术使用内部集成电阻代替外部的终端电阻,不仅有助于减小PCB尺寸,降低成本,而且由于印刷版上没有了连接匹配电阻所需要的分支电路,最大限度地减少了分支线的干扰,减小了信号反射幅度,大大提高了传输信号的质量[9]。ODT与DCI的等效电路如图 6所示。

|

| 图 6 ODT与DCI的等效电路 |

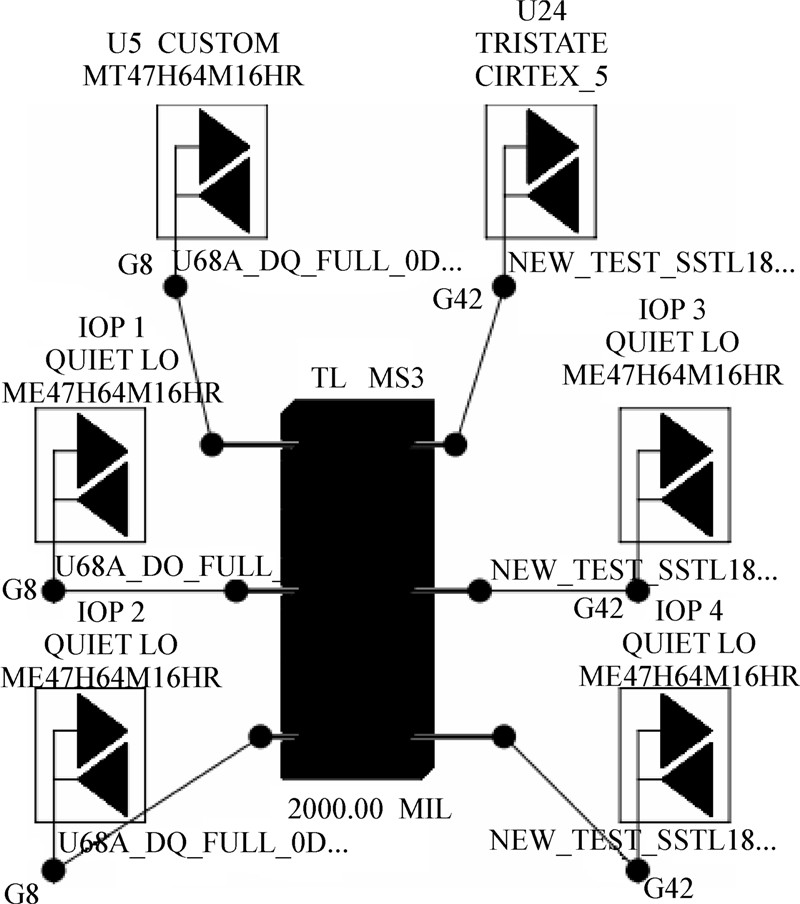

选用带DCI功能的FPGA管脚缓冲器模型和带ODT功能的DDR2 SDRAM管脚缓冲器模型,提取到的单一数据线的拓扑如图 7所示。其中TL13、TL14、TL15、TL16为传输线模型,VIA7、VIA8为过孔模型,U5和U24分别DDR2 SDRAM和FPGA的管脚缓冲器模型,其他条件均与图 3仿真时中使用的参数一致。

|

| 图 7 ODT和DCI匹配时提取到的拓扑结构 |

为FPGA管脚加上533 Mbit/s的随机数据激励,另一端的电平类型选择为三态(模拟DDR2 SDRAM的写操作)。为DDR2 SDRAM管脚加上533Mbit/s的随机数据激励,另一端的电平类型选择为三态(模拟DDR2 SDRAM的读操作)。得到的写时序和读时序的信号眼图分别如图 8、9所示。

|

| 图 8 ODT和DCI匹配时写时序的数据总线波形眼图 |

|

| 图 9 ODT和DCI匹配时读时序的数据总线波形眼图 |

由图 8、9的结果可以看到,使用了带ODT和DCI技术的缓冲器模型之后,读和写时序的信号眼图的上冲和下冲都比不使用此技术进行匹配时小,且都在DDR2 SDRAM和 FPGA对上冲和下冲的要求之内。

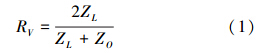

在实际PCB生产中,导线的宽度、厚度,绝缘材料的介电常数和厚度的微小变化都会引起特性阻抗发生变化,而由于工艺限制,这些参数在制造时都有一定的误差,导致实际传输线的阻抗与理想情况下阻抗不一致,因此在对阻抗匹配结果分析时要留一定的裕量。目前民用PCB的阻抗控制误差一般在10%以内。设DDR2 SDRAM的ODT功能内部匹配电阻等效为ZL,传输线的特征阻抗为ZO,当以低电平稳定电压作为参考零电位时,上冲电压与高电平稳定电压之比为[10]

图 8中上冲电压的值为1.471 V,高低电平稳定电压之差约为1.1 V,故考虑了阻抗误差的情况下上冲电压最大值约为1.471+1.1×5%=1.526 V。同样可得下冲电压的最小值约为0.284 V,上冲和下冲均在DDR2 SDRAM的数据线管脚电平要求之内。图 9中考虑了阻抗误差的情况下上冲电压最大值约为1.737 V,最小下冲电压约为0.077 V,也在FPGA的管脚电平要求之内。

3.5 串扰仿真

PCB上走线串扰的大小跟2根互相耦合的走线的线距、耦合长度、信号的上升沿和下降沿斜率等有关[11]。一般为了使走线之间的串扰降低到可以忽略的程度,走线需要遵循“3W原则”(两根相邻走线中心的间距至少为3倍的走线宽度[12])。但是随着目前高密度小型化集成板的应用以及成本的考虑,使走线之间的距离满足“3W原则”实际上很难实现,此时对PCB做布线后的串扰仿真就显得尤为重要,可以确保在不遵循“3W原则”的情况下走线之间的串扰不会严重到影响信号的完整性。

在系统中由于考虑了探测器安装和电路板外壳制作等因素,对PCB板的尺寸有一定要求,PCB板不能绘制的足够大来满足所有走线之间的“3W原则”,而且由于DDR2 SDRAM大量的数据线和地址线都要汇集到FPGA同一侧密集的管脚上,因此高密度紧耦合的走线不可避免。

系统中DDR2 SDRAM数据线走线的最大长度小于2 000 mil,走线宽度为8 mil,最小的走线间距为8 mil,走线类型为微带线,信号速率为533 Mbit/s。因此对3根2 000 mil耦合长度的微带线在信号速率为533 Mbit/s情况下进行仿真。为了观察不同线间距对串扰的影响,分别对8、12、16、20、24 mil间距的情况下进行串扰仿真。仿真模型如图 10所示,其中U5、IOP1和IOP2是MT47H64M16带ODT功能的数据线引脚缓冲器模型,U24、IOP3和IOP4是FPGA的SSTL18_II_DCI类型电平的缓冲器模型。TL_MS3是3根长度为2 000 mil的互相耦合的微带线模型。其中中间的微带线为受干扰线,两边的微带线为干扰线。

|

| 图 10 3根微带线线串扰仿真模型 |

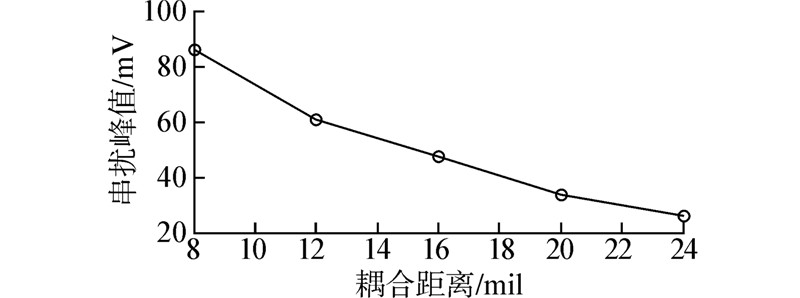

信号由FPGA向DDR2 SDRAM的2根数据线传输时(等效于DDR2 SDRAM的写操作),在2根数据线中间的另一根线上靠近DDR2 SDRAM端产生的串扰仿真数据如图 11所示。

|

| 图 11 DDR2 SDRAM写操作时的串扰数据波形 |

由图 8可得,在DDR2 SDRAM写操作时,高电平的稳定电压值约为1 450 mV,低电平的稳定电压值约为370 mV,即高电平噪声容限为1 450-1 150=300 mV,低电平的噪声容限为650-370 =280 mV。当两线之间的间距为 8 mil时,串扰的峰值约为86 mV,在信号的噪声容限之内。且随着两线间距的增加,串扰逐渐减小,在满足“3W”原则的情况下,串扰只有50 mV左右,远小于噪声容限。

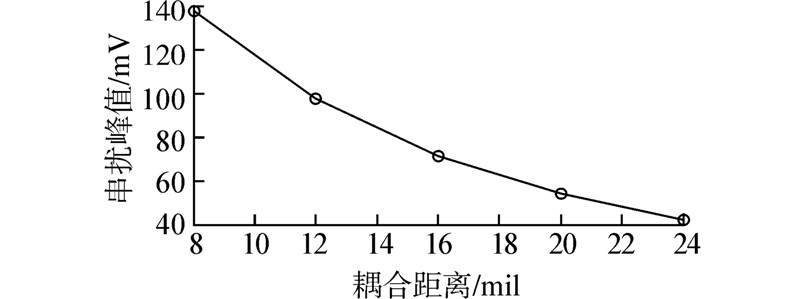

信号由DDR2 SDRAM的2根数据线向FPGA传输时(等效于DDR2 SDRAM的读操作),在2根数据线中间的另一根线上靠近FPGA端产生的串扰仿真数据如图 12所示。

|

| 图 12 DDR2 SDRAM读操作时的串扰数据波形 |

由图 9可得,在DDR2 SDRAM读操作时,FPGA端高电平的稳定电压值约为1 580 mV,低电平的稳定电压值约为250 mV,则高电平噪声容限为1 580-1 025=555 mV,低电平的噪声容限为775-250=525 mV。当2线之间的间距为8 mil时,串扰的峰值为137 mV,远小于信号的噪声容限。

4 结束语

本文针对高速大面阵图像传感系统中信号速率为533 Mbit/s、带宽为2 GB的技术要求,由FPGA驱动读写的DDR2 SDRAM数据线进行了反射和串扰两方面的信号完整性仿真分析。通过仿真结果闭环控制对设计进行了必要的修改,最终使关键部分的指标满足了信号完整性的要求,为良好的系统设计提供了有力保障。

本文所提出的信号完整性仿真方法在信号频率小于1 GHz的情况下具有普遍适用性,从仿真模型的转换、建立、拓扑结构的提取、信号设置,到仿真结果的分析和反馈,是一套完整的高速信号仿真流程,为处理相似的问题提供了解决思路和解决途径。但是针对更高频率的信号完整性问题,需要考虑三维空间中的电磁场仿真,借助Ansoft HFSS等软件来实现,本文中并未讨论三维空间电磁场引入问题的解决思路,因此本文提出的仿真方法在这种场合中不再适用,可作为下一步研究的方向。

| [1] | 刘哲. 基于FPGA的高速数字工业相机系统设计与实现[D]. 北京: 中国科学院大学工程管理与信息技术学院, 2013: 15-20. |

| [2] | 杨古月, 张昕. DM6446与DDR2接口的信号完整性研究[J]. 应用科技, 2013, 40(4): 42-45. |

| [3] | 堵军, 高辉, 张益平. 电路设计中的信号完整性分析和研究[J]. 电子与封装, 2013(8): 25-29. |

| [4] | 周路, 贾宝富. 信号上升或下降时间对高速电路信号完整性影响的研究[J]. 现代电子技术, 2011(6): 69-73, 77. |

| [5] | 张吉, 刘煜, 杨福彪. 高速数字信号完整性之串扰分析与控制[J]. 工业控制计算机, 2009(5): 13-14, 16. |

| [6] | BOGATIN E. 信号完整性分析[M]. 李玉山,等译. 北京:电子工业出版社, 2005: 52-60. |

| [7] | 李莉, 李卫兵, 王学刚, 等. 二平行传输线间的串扰分析[J]. 电波科学学报, 2001(2): 271-274, 282. |

| [8] | 徐文波, 保长先, 王健. IBIS模型的信号完整性研究与仿真应用[J]. 机电工程, 2011(1): 123-126. |

| [9] | 夏佩群, 占腊民. DDR2存储系统动态匹配技术的研究[J]. 舰船电子工程, 2009(4): 119-122. |

| [10] | 孙宇贞. 高速电路的信号完整性分析[J]. 电子技术应用, 2005(3): 73-76. |

| [11] | 郑常斌, 张丹, 黎淑兰, 等. PCB上两平行微带线的串扰分析[J]. 安全与电磁兼容, 2007(3): 73-76. |

| [12] | 陈俊秀. 浅析印制电路板上走线间的串扰问题[J]. 科技信息: 科学·教研, 2008(13): 411-412. |