频率合成器是通信、雷达、仪器仪表、空间电子设备和电视等现代电子系统的心脏,其好坏直接影响电子系统的性能指标。锁相环频率合成(PLL)和直接数字频率合成(direct digital frequency synthesis,DDS或DDFS)是目前产生频率源的2种主要技术。DDS代表了频率合成领域新兴的发展方向。由于它具有相位连续、频率分辨率高、频率切换速度快和数字化实现,体积小、功耗低等优点,在频率源的设计中得到了广泛应用。目前实现DDS的技术方案主要有2种:一是采用高性能DDS 芯片的解决方案;二是基于FPGA 技术实现DDS的方案。文中提出了MATLAB与FPGA交互的方法,在FPGA设计与实现之前,首先进行电路的MATLAB仿真,用于验证整个FPGA电路的工作过程及输出结果是否满足要求。

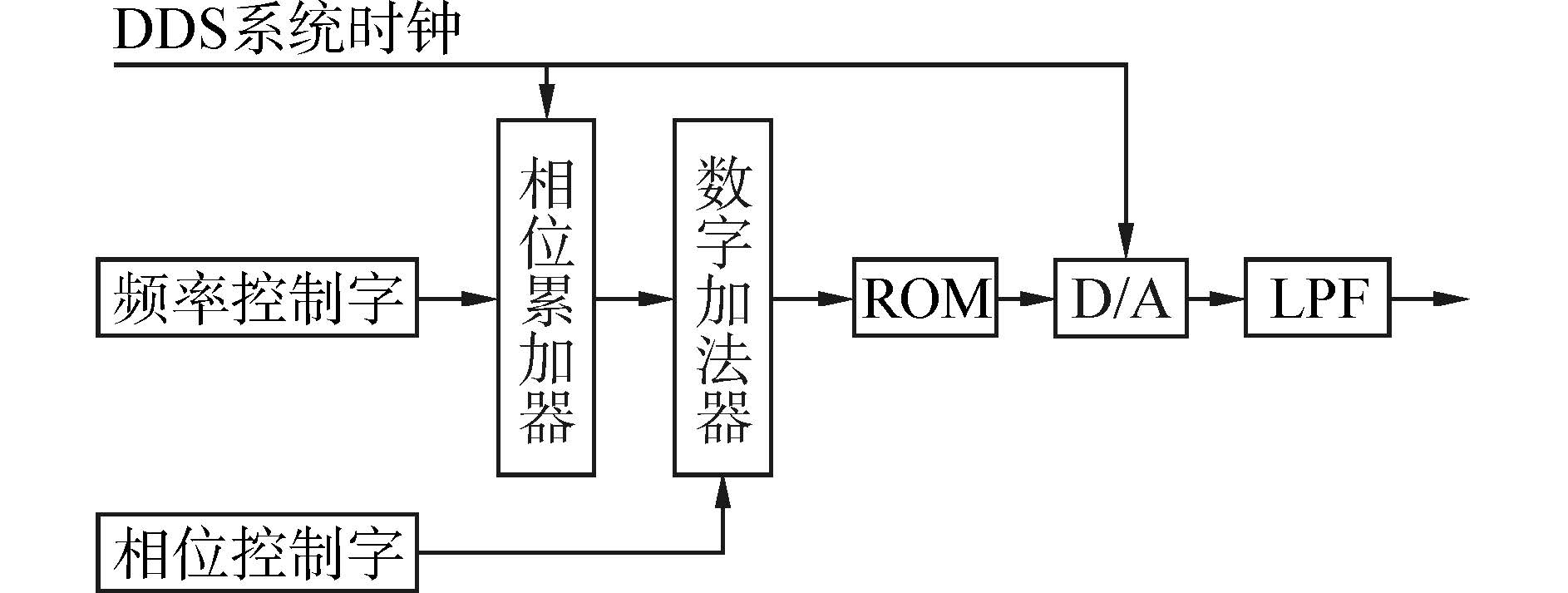

1 DDS的基本原理DDS的基本工作原理是利用采样定理,通过查表法产生波形。其基本工作原理如图 1所示。

|

| 图 1 DDS基本工作原理框图 |

由图可以看出,DDS主要由相位累加器、正弦查表ROM、D/A和低通滤波器LPF几个基本单元组成。相位累加器在每个时钟周期内累加上由频率控制字K设定的相位增量;累加的相位量在ROM中进行查表,得到数字正弦采样值;然后通过D/A变换为数字阶梯波;最后,经过低通滤波器LPF实现平滑输出。具体工作原理介绍如下:

设相位累加器的字长为N,则其共有2N个状态。在每个时钟周期内,相位累加器的输出就增加一个步长的相位增量(频率控制字K),当相位累加到满量程时便产生一次溢出,完成一个周期信号的输出。DDS输出信号的频率与时钟频率之间的关系为

fout=Kf0 /2N

这样就可以通过改变频率控制字K来改变输出频率。从原理中可以看出,DDS能产生的最小频率为f0/2N,这个频率被称为是DDS的分辨率。提高相位累加器的位数可以产生更小频率的信号,提高频率的分辨率。根据采样定理,最高的基波合成频率为foutmax=f0/2

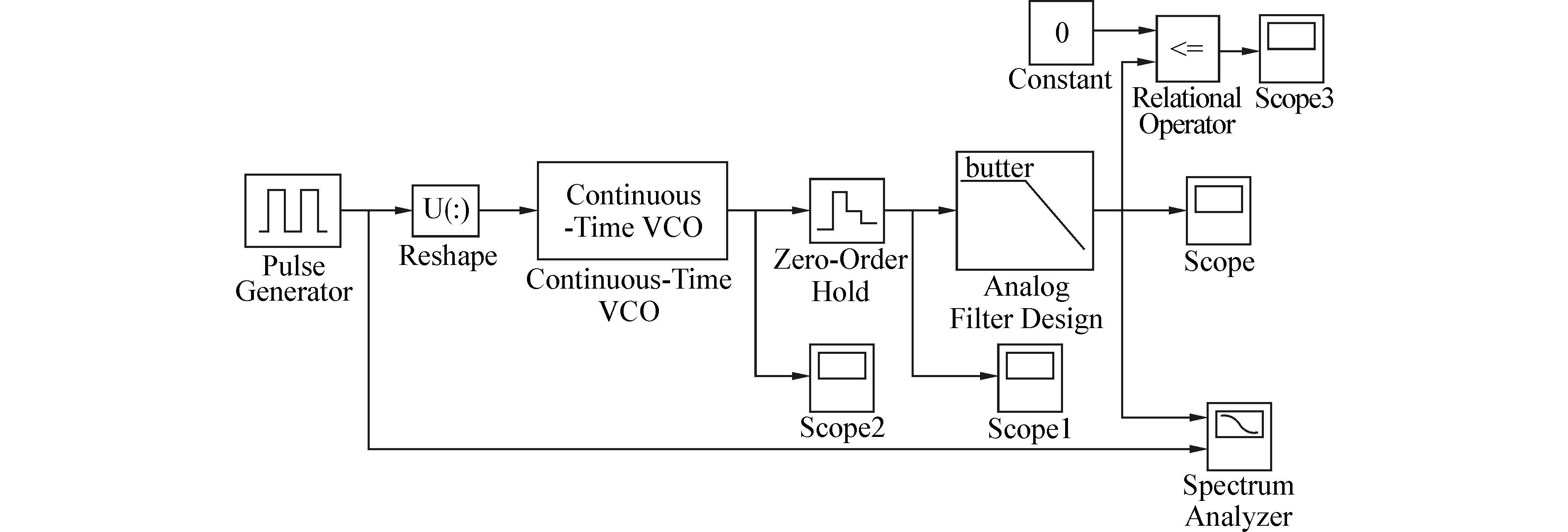

这说明了在DDS中参考时钟频率总是比基波合成频率高的原因。 2 系统设计首先,根据DDS的基本原理,搭建DDS仿真模块,如图 2所示。

|

| 图 2 DDS仿真模块 |

图 2中,Pulse Generator模块为系统提供稳定的时钟信号;Reshape模块完成数据类型及向量维数的转换;Continuous Time-VCO 模块实现DDS功能,产生频率变化的载波,设置输出信号幅度为1 V,输出频率为10 200 kHz,,输出信号灵敏度为0.25 Hz/V,初始相位为0;zero-order Hold模块完成采样保持,采样时间设为1/120 000 000 s。LPF:Analog Filter Design模块用于实现数字阶梯波平滑输出为正弦波波形,滤波器的阶数设为8,截止频率为120 000 000π rad/s.

3 仿真结果DDS仿真模块波形如2图所示,系统仿真是由MATLAB7.8.0 (R2009a)软件实现的。

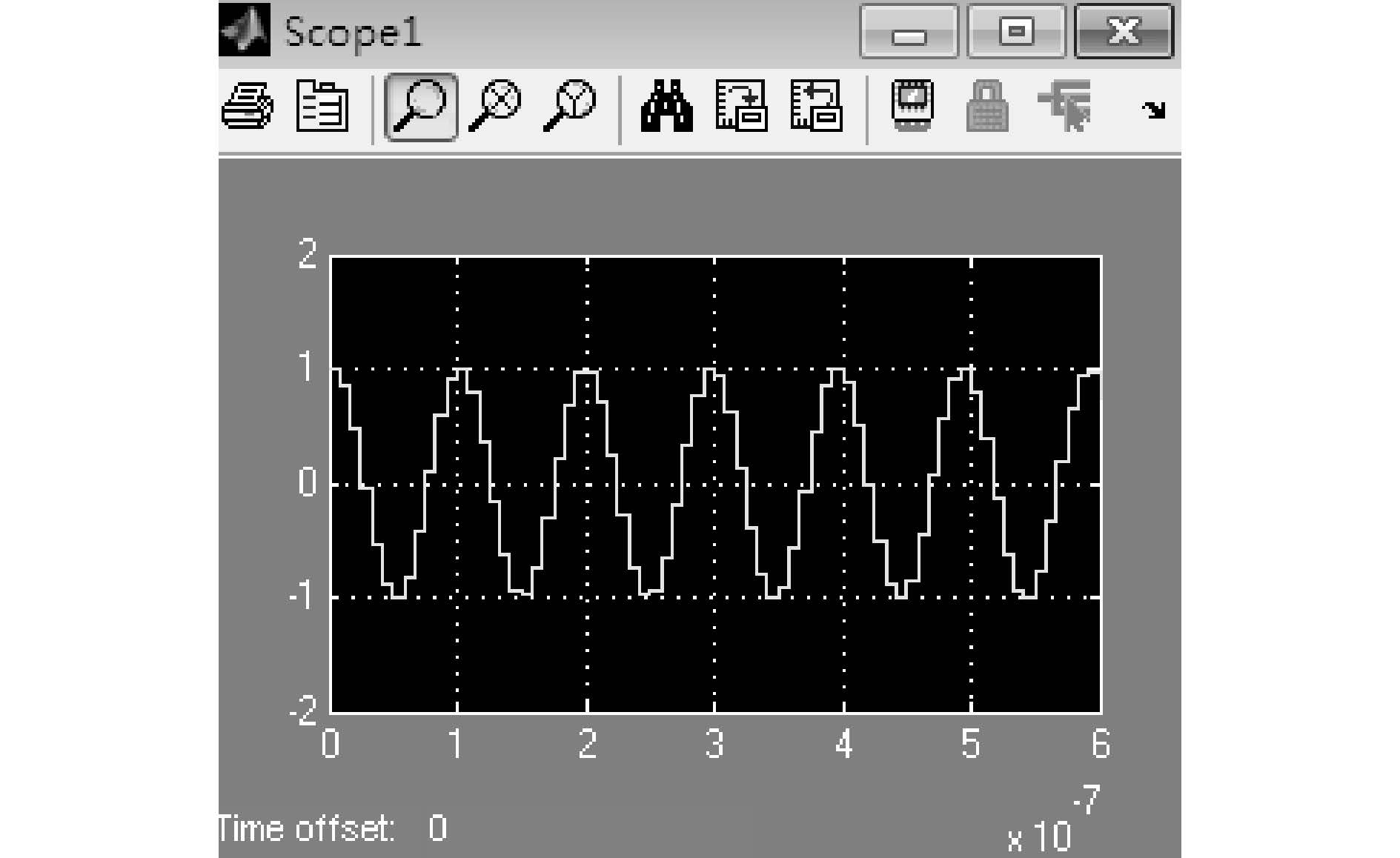

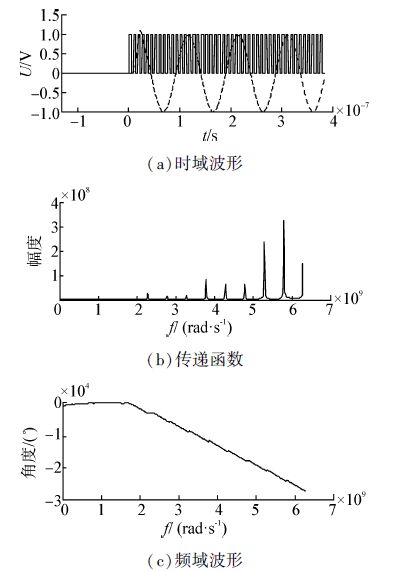

图 3显示的是DDS合成器输出正弦波波形,其频率为10 200 000 Hz;图 4显示的是经过零阶采样保持模块zero-order Hold后的输出波形,为一周期性的数字阶梯波;图 5显示的是数字阶梯波经过低通滤波器模块Analog Filter Design平滑输出后的输出波形,为正弦波波形;图 6显示的是经过方波转换模块Relational Operator后的输出波形,为方波波形;图 7显示的是DDS单通道输出信号频谱图。

|

| 图 3 DDS合成器输出正弦波波形 |

|

| 图 4 输出数字阶梯波波形 |

|

| 图 5 输出正弦波波形 |

|

| 图 6 输出方波波形 |

|

| 图 7 DDS单通道输出信号频谱 |

分析阶梯波的频谱组成:由于巴特沃斯滤波器在通带以内幅频曲线的幅度最平坦,由通带到阻带衰减陡度较缓,截止频率以后的衰减速率为6×106 dB/倍频程,相频特性非线性,滤波效果较好。所以应当选取截止频率比较低的低通滤波器使得平滑效果较好,但选取的截止频率又必须保证输出信号能够顺利通过。根据采样定理,输出信号的频率最大值为fout= f0/2,故选择最佳截止频率为f0 /2,能够保证对于不同的频率控制字K,电路都能正常工作。在此仿真模块的基础上,根据实际需要还可以在做出一些改进。比如,改变ROM存储的幅度值,可以实现锯齿波和三角波等不同类型信号的输出;增加移相的子模块,可以研究如何用DDS实现调频信号发生器;增加用于截短二进制码的子模块和频谱分析子模块,观测各级控制字的截短对DDS输出相位舍位噪声和有限字长效应噪声带来的影响。在 DDS仿真模块 中,由于ROM相对昂贵,所以ROM的字节数往往小于2N。这意味着相位输出的低N-(K+2)有效位不会在合成频率中使用,从而产生一个相位量化误差。

但是,DDS合成器在跳频处没有杂散幅度和频率成分。利用现有的最新技术,这种合成器的切换时间可以做到小于1 μs,当产生小的频率步进时,这也是最便宜的一种方法。

现在这种合成器输出的带内杂散信号电平在1~2 MHz时为-50 dBc。这就需要一个分频器来提供必要的滤波以满足更严格的需求,它也会更进一步地减小输出频率和输出频率的范围。但它在设计高频快速切换频率合成中仍起着重要作用。依现在的经验来看,人们相信在不远的将来可以用同样的性能得到5~25 MHz的频率。

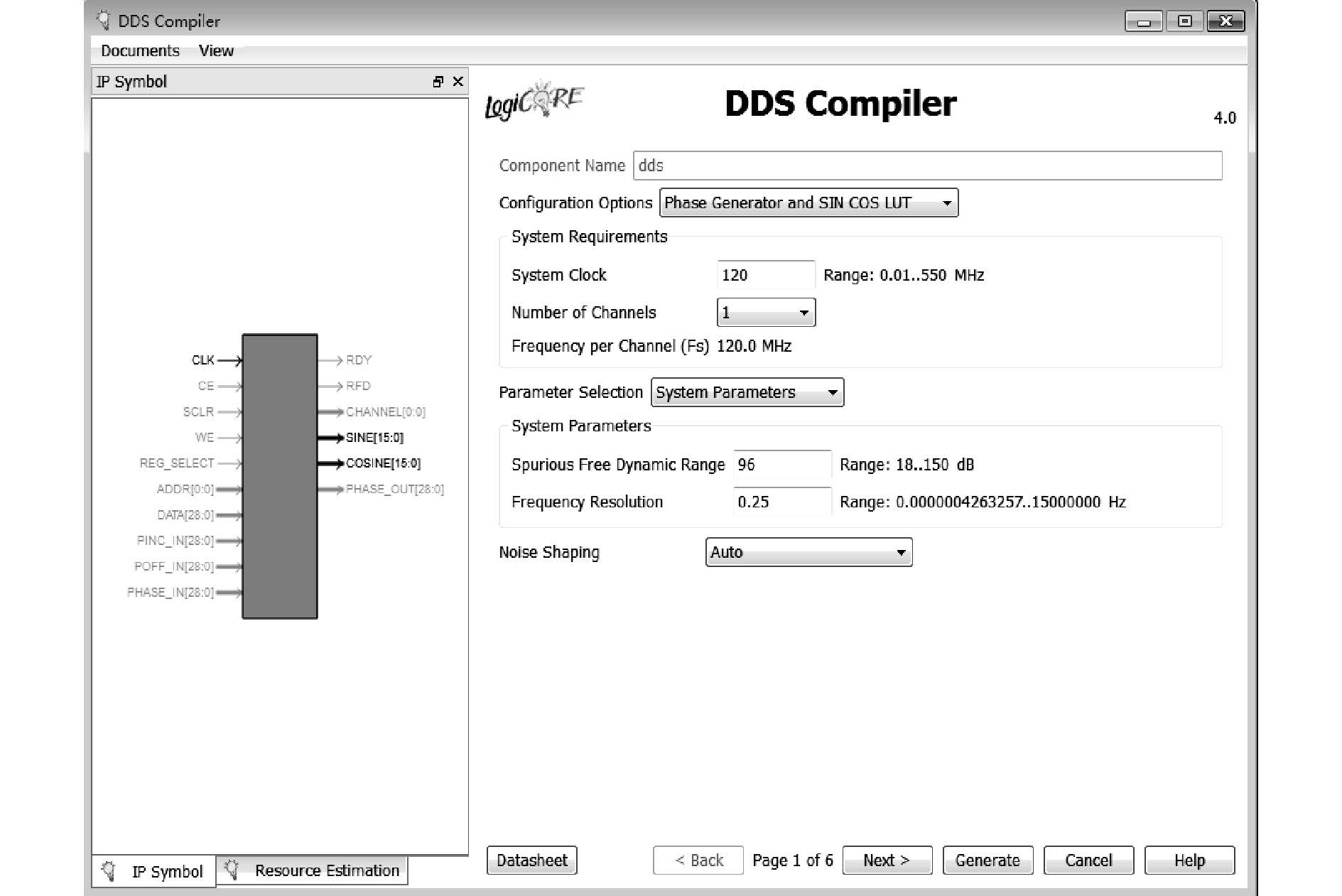

4 DDS的设计与实现DDS技术的实现依赖于高速、高性能的数字器件。FPGA技术的出现,使得频率合成器的实现更加容易。Xilinx 公司作为世界上最大的 FPGA/CPLD 生产商之一,多年来一直占据行业领先的地位。Xilinx 的 FPGA/CPLD 具有高性能、高集成度和高性价比的优点,而且它还提供了功能全面的开发工具和丰富的IP核、宏功能等。ISE(intergrated synthesis environment)是Xilinx FPGA/CPLD 的综合性集成设计平台,利用该平台可完成从设计输入、仿真、逻辑综合、布局布线与实现、时序分析、程序下载与配置、功耗分析等整个FPGA/CPLD 的开发过程,其最新版本为ISE14.7 Suit系列。ISE 13.1提供了十分易于使用的DDS核DDS Compiler v4.0。DDS核实例化后,即可以使用。在IP核生成界面依次单击“View by Function→Digital Signal Processing→Modulation→DDS Compiler v4.0”,即可进入DDS核参数设置界面,如图 8所示。

|

| 图 8 DDS核参数配置界面 |

DDS的设计比较简单,直接采用ISE提供的DDS核即可。设计者需要确定的主要参数有DDS相位累加字位宽(频率字位宽) BDDS 、驱动时钟频率 fCLK 、输出数据位宽A等参数。环路中,DDS的输出数据位数A通常与输入数据位数 Bdata 相同,即 A=Bdata 。当然,DDS的输出数据位数也可以根据实际情况进行调整,DDS的输出数据位数越多,则本地振荡器输出信号的旁瓣抑制比(spurious free dynamic range,SFDR)性能越好,系统所耗费的硬件资源也越多。DDS的旁瓣抑制满足A/D转换的字长效应,输出波形的位宽每增加1 bit,其旁瓣抑制比就提升6 dB。即FPGA内部的任何一点信号,每多用1 bit,其信噪比提升6 dB。DDS的驱动时钟频率 fCLK 通常与输入数据采样速率 fs 相同,即 fCLK=fs 。相位累加字位宽不仅影响到整个环路的总增益,更重要的是直接决定了更新频率字所能达到的频率分辨率,工程上通常需要频率分辨率小于1 Hz。其中频率字Δ θ 、输出频率fout、频率字位宽 BDDS 之间的关系为

fout=fCLK×Δθ/2BDDS

这样就可以通过改变频率控制字 Δθ 来改变输出频率。从原理中可以看出,DDS所能产生的最小频率为

fout=fCLK/2BDDS

这个频率被称为是DDS的分辨率。显然,增加频率字位数 BDDS ,可以产生更小频率的信号,提高频率的分辨率。在设计整个载波同步环路时,环路的总增益是一个非常重要的参数,而其中DDS的增益 KDDS 为

KDDS=2πTDDSfCLK/2BDDS

式中 TDDS 为DDS频率字更新周期。显然,频率字位数越多,DDS的增益越小;频率字更新周期越长,DDS增益越大。假设DDS相位累加字位宽(频率字位宽) BDDS =29,系统时钟频率 fCLK =32 MHz,要求输出6 MHz的频率,则可计算出DDS的初始频率字(相位增量)为Δθ=2BDDSout/CLK=229×6/32=100 663 296

即Δ θ =(00112015010720150107201501072015010720150107)2DDS的频率分辨率为

Δf=fCLK/2BDDS=32×106/229=0.059 6 Hz

利用DDS核产生正弦和余弦信号,要求频率分辨率Δ f=0.25 Hz ,旁瓣抑制比(动态无杂散范围)大于96 dB,量化相位误差 φ=±π/4 rad/s ,fout=10.2 MHz 。为便于在FPGA电路板上观察显示结果,将输入的10.2 MHz信号进行10 200 000分频处理,驱动电路板上的LED灯显示。FPGA目标芯片为Virtex5系列的xc5vlx30-3 ff324。假设系统时钟频率为 fCLK=120 MHz 。

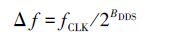

根据DDS的原理,DDS的频率分辨率:

从而

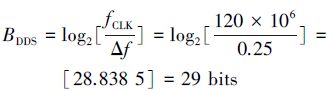

由于DDS的旁瓣抑制为6 dB/bits,因此

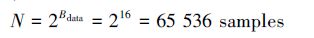

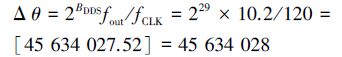

这样,ROM的深度N为

即产生数据宽度为16 bits,深度为65 536 samples的ROM。

相位字(相位偏移) POFF 为

因为要求产生10.2 MHz的频率信号,即 fout =10.2 MHz,所以可以求得频率字Δθ为

即BDDS=(00010101110000101000111101011)2

如果,频率字PINC可编程,则输出频率在DDS运行过程中可以调整

例如 fout =8.2 MHz,可以求得新的频率字Δ θ 为

这时,可通过修改下面相关参数来实现,具体方法如下:

WE:写频率/相位字允许信号,当需要在运行过程中修改频率/相位时,选择此信号;

REG_SELECT:频率/相位寄存器选择信号,为0表示写频率字,为1表示写相位字,此信号只有当频率/相位字均可编程时才有效;

DATA:频率/相位字输入数据,其位数与频率字位宽BDDS相同。

根据DDS设计要求,DDS IP核的驱动时钟频率为120 MHz,频率分辨率=0.25 Hz,SFDR=96 dB,输出频率为10.2 MHz,详见图 8DDS核参数设置界面。

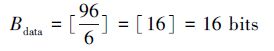

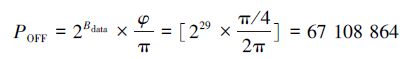

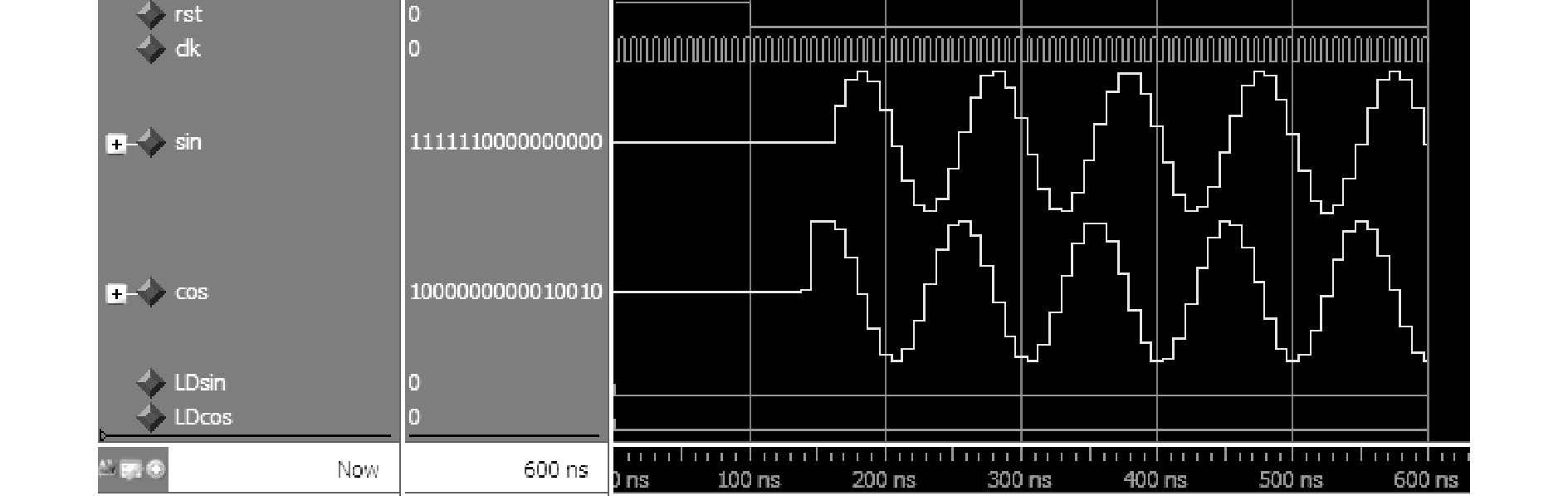

图 9为系统设计在Xilinx ISE开发平台下实现后的仿真波形。系统仿真是由Modelsim10.1a软件实现的。从Modelsim 10.1a的波形界面中虽然能查看信号的仿真波形,但想要对数据进行进一步详细分析,比如查看信号的频谱等,就显得无能为力了。这一部分工作正好用MATLAB软件来完成,DDS单通道输出信号频谱如图 9所示。

|

| 图 9 DDS仿真波形 |

FPGA实现后,可以在ISE界面十分方便地查看到整个系统所占用的硬件资源及最高系统运算速度。其中,Slice Registers(寄存器资源)使用了251个,占1%;Slice LUTs(查找表资源)使用了290个,占1%;BlockRAM/FIFO使用了2个,占6%;BUFG/BUFGCTRLs(全局时钟资源)使用了1个,占3%。Minimum period:1.927ns{1} (Maximum frequency:518.941 MHz)最高系统时钟频率可达518.941 MHz,显然满足设计实例中要求的120 MHz。FPGA实现后,可以看到电路板上2个LED灯均以1 Hz的频率闪烁。

5 结束语DDS技术是一种具有广泛应用前景的频率合成技术。由于具有相位连续、频率分辨率高、频率切换速度快和数字化实现,体积小、功耗低等优点,DDS在通信、雷达、仪器仪表等很多领域得到了广泛的应用。但是由于DDS本身输出频率低、输出杂散大等局限性,它一般都与其他技术相结合来实现频率更高的频率合成器。在FPGA实现中,通常采用ISE工具提供的DDS核来实现。DDS的旁瓣抑制满足A/D转换的字长效应,输出波形的位宽每增加1 bit,其旁瓣抑制比就提升6 dB。当SFDR的需求高于80 dB时,建议开启噪声抑制功能。DDS的输出数据位数越多,输出信号的旁瓣抑制比性能越好,系统所耗费的硬件资源也就越多。

| [2] | MANASSEWITSCH V. 频率合成原理与设计[M]. 何松柏,宋亚梅,鲍景富,等译. 北京: 电子工业出版社, 2008: 300-360. |

| [3] | 杨路刚, 刘宏波, 李丽华. Simulink在“频率合成”课程自主性实验中的应用[J]. 电气电子教学学报, 2010, 32(3): 71-74. |

| [4] | 杜勇. 数字通信同步技术的MATLAB与FPGA实现[M]. 北京: 电子工业出版社, 2013: 55-68. |

| [5] | 赵刚. 扩频通信系统实用仿真技术[M]. 北京: 国防工业出版社, 2009: 30-63. |

| [6] | 钞锋, 邱迎锋, 牛萌. 直接数字频率合成在软件无线电中的应用[J]. 微计算机信息, 2007, 23(8): 187-190. |

| [7] | 李琳, 张尔杨. 直接数字频率合成技术及其应用[J]. 电声技术, 1999(9): 33-36. |

| [8] | Xilinx IP核数据手册. DDSCompiler v4.0[EB/OL]. [2014-03-09]. www.Xilinx.com. |