近年来,NAND闪存已成为主流存储介质,在智能手机、个人电脑和大型数据中心中得到广泛应用[1-4]。随着制造工艺的进步,闪存单元的封装尺寸逐渐缩小。一方面,闪存单元中存储的比特数成倍增加;另一方面,闪存内部相邻单元寄生耦合电容效应变大,单元间干扰(cell-to-cell interference, CCI)增强,导致数据存储可靠性降低[5-6]。与此同时,编程次数和保持时间的增加引发随机电报噪声(random telegraph noise)和可持久性噪声(retention noise),降低了闪存的使用寿命。

关于以上噪声带来的信道检测可靠性下降问题,国内外学者提出了一些解决方案[6-8]。针对单元间干扰,Peng等[5]提出CSAD和NIA-CSAD检测策略;Dong等[7]分析了单元间干扰信道模型,并用熵函数来近似求出两种状态分布重叠区的读取参考电压。上述工作需要估计出最优读取参考电压,该方法依赖闪存信道精准的先验信息(相邻单元先验信息、编程和擦除次数、保持时间等相关参数)。为减少对信道先验信息的依赖,文献[8]提出了循环神经网络(recurrent neural network, RNN)检测器。该检测器在未知信道先验信息下能减少噪声对信道可靠性的影响,但是该实验只分析了持久性噪声,没有考虑单元间干扰的影响,并且RNN检测器复杂度较高,被激活会占用大量的系统空闲时间。在实际场景中,闪存信道会同时存在随机电报噪声、可持久性噪声和单元间干扰。信道噪声随保持时间变化,对阈值电压分布扭曲的影响是很难预测的。当前,深度学习技术迅速发展,在信道检测与估计中都表现出优越的性能[7-12]。本文提出的卷积神经网络(convolutional neural networks, CNN)可以从良好的数据集中学习闪存信道难以预测的变化,并能有效检测闪存单元状态。与现有的大多数检测技术相比,该方法不依赖于精确的信道模型。本文的贡献主要分为3个方面:

1)通过相关文献对闪存信道特征的测试,可知相邻单元会受到编程单元的干扰[7-9]。基于闪存相邻单元间特征,本文先在二维坐标下分析了相邻单元编程后阈值电压的相关性,这种相关性表现为相邻单元阈值电压和受干扰单元阈值电压越大,受干扰单元阈值电压越往右偏移。文献[13]揭示了CNN在相关噪声信道中表现出较好的特征提取效果,所以本文挑选CNN网络来检测NAND闪存单元状态。

2)实验采用以随机电报噪声、可持久性噪声和单元间干扰为主要噪声源的闪存信道[9],生成受干扰单元和相邻单元的阈值电压序列,组成二维训练数据集。低密度奇偶校验(low-density parity-check, LDPC)解码的单元状态通过独热编码数据预处理作为数据集标签。已训练好的CNN检测器在没有任何信道先验信息下可以直接输出闪存信道的硬判决信息(单元存储状态)和软判决信息(闪存单元属于某种状态的后验概率)。假设信道模型已知,熵函数求解出电压分布相邻状态分布的重叠区间。在重叠区间中用穷举搜索法找到的最优阈值作为性能对比标杆,下面称之为最优阈值检测器(optimal threshold detector)。计算机仿真结果显示:本文提出的CNN检测器与最优阈值检测器对比,在信道先验信息未知时,能有效提升闪存信道的检测性能。

3)与现有的RNN检测器[8]相比,分析了两者的浮点运算数(floating-point operations, FLOPs),单层CNN网络复杂度显著小于单层RNN网络。因此,CNN检测器被激活所需的系统空闲时间比RNN要少得多。

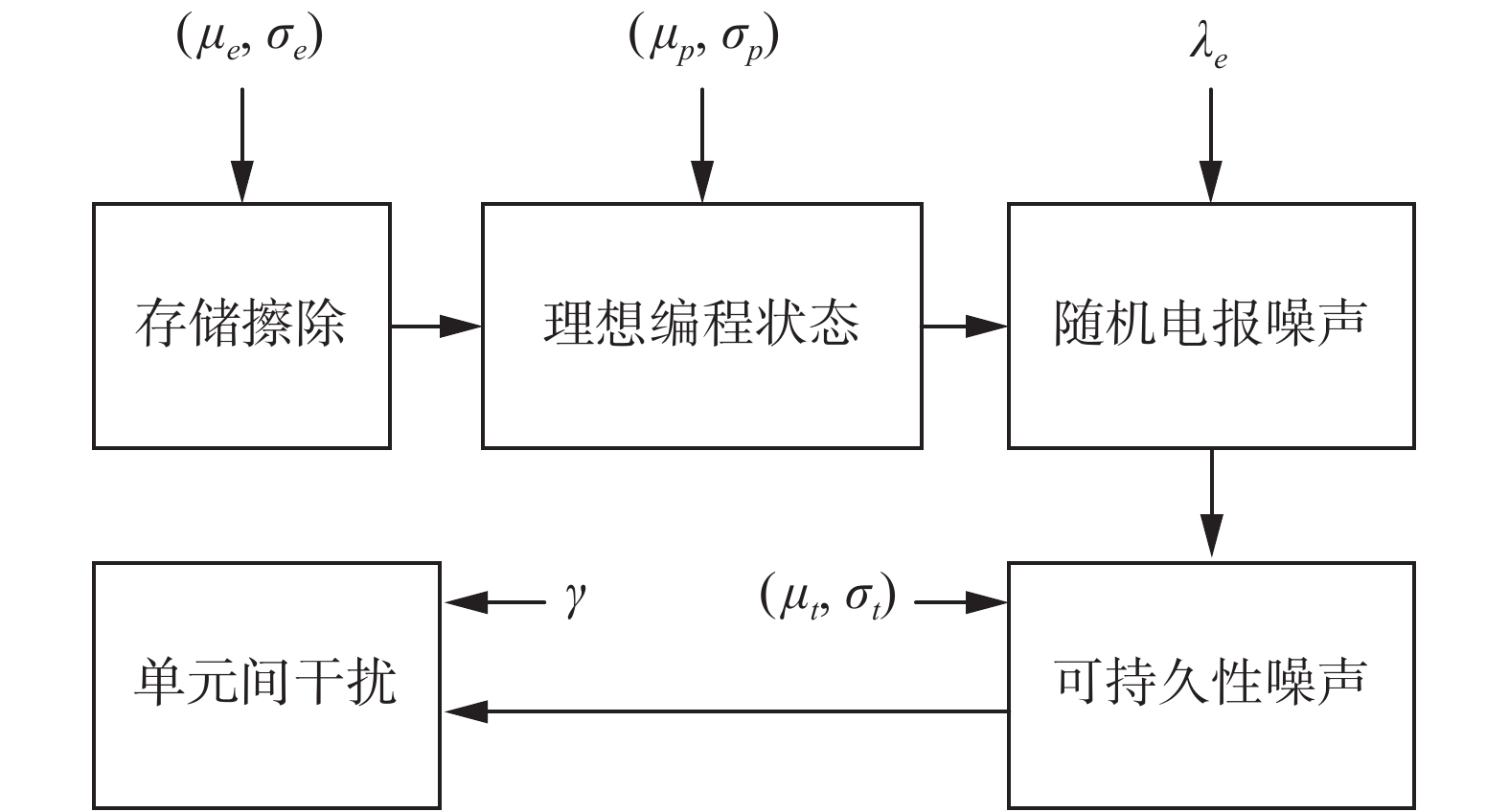

1 闪存信道系统闪存信道系统模型如图1所示,数据先通过擦除与编程操作写入闪存中,随后经过的干扰包括随机电报噪声、可持久性噪声和单元间干扰。

|

Download:

|

| 图 1 MLC闪存信道模型 Fig. 1 MLC flash channel model | |

在NAND闪存中,字线(word-line)由擦除状态单元和编程状态单元组成[14]。对于MLC型的闪存单元,可以存储2比特位,并将存储类型表示为4个不同的状态:11、10、01和00。11是擦除状态,其余的是编程状态。

在编程之前,必须擦除闪存单元中的数据。擦除单元的阈值电压符合高斯分布[8],该分布为

| $ {p_e}(x) = \frac{1}{{{\sigma _e}\sqrt {2{\text{π}}} }}\exp \left( - \frac{{{{(x - {\mu _e})}^2}}}{{2\sigma _e^2}}\right) $ | (1) |

式中:σe和μe分别是被擦除单元阈值电压分布的标准差和平均值。

在编程操作中,闪存控制器会向浮栅注入一定量的电荷。编程状态的阈值电压也服从高斯分布[14]:

| $ {p_p}(x) = \frac{1}{{{\sigma _p}\sqrt {2{\text{π}}} }}\exp \left( - \frac{{{{(x - {\mu _p})}^2}}}{{2\sigma _p^2}}\right) $ | (2) |

式中:σp和μp分别是被编程单元阈值电压分布的标准差和平均值。

1.2 随机电报噪声编程和擦除次数会损坏浮栅晶体管隧道的氧化物,引起闪存单元阈值电压随机波动。因此,随机电报噪声采用类高斯分布建模为

| $ {p_r}(x) = \frac{1}{{2{\lambda _e}}}\exp \left( - \frac{{\left| x \right|}}{{{\lambda _e}}}\right) $ | (3) |

式中:

可持久性噪声是由编程单元中电荷泄漏引起的阈值电压分布偏移。可持久性噪声遵循高斯分布[15]:

| $ {p_t}(x) = \frac{1}{{{\sigma _t}\sqrt {2{\text{π}}} }}\exp \left( - \frac{{{{(x - {\mu _t})}^2}}}{{2\sigma _t^2}}\right) $ | (4) |

平均值μt和标准差σt由式(5)、(6)给出[16]:

| $ {\mu _t} = \mathop {\Delta V}\nolimits_t \left[ {{A_t}{{({\rm{PE}})}^{{a_i}}} + {B_t}{{({\rm{PE}})}^{{a_0}}}} \right] \cdot \log (1 + T) $ | (5) |

| $ {\sigma _t} = 0.5\left| {{\mu _t}} \right| $ | (6) |

式中:

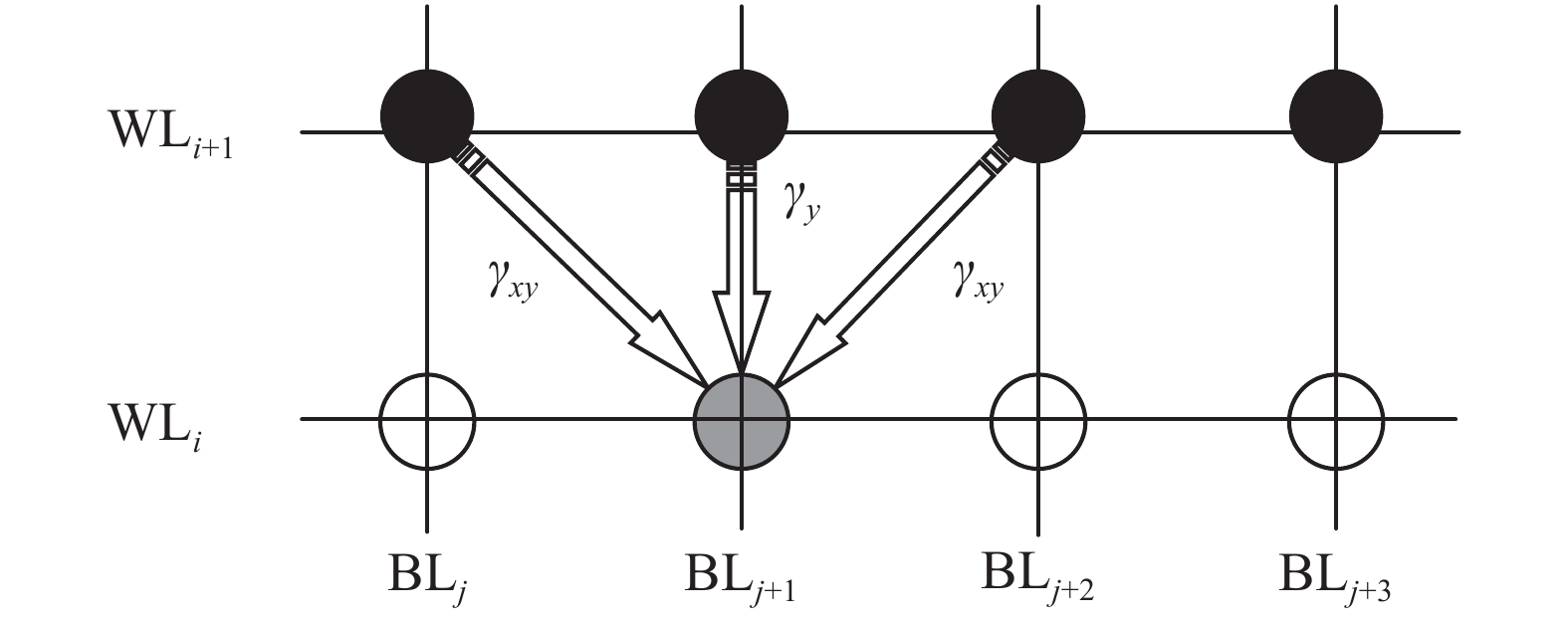

单元间干扰是闪存信道中主要噪声之一[17]。编程单元阈值电压的变化会影响相邻单元的阈值电压。由单元间干扰引起的受干扰单元的总阈值电压影响强度计算公式为[17]

| $ F = \sum\limits_k {\left( {\Delta {V^{(k)}}* {\gamma ^{(k)}}} \right)} $ | (7) |

式中:

|

Download:

|

| 图 2 多电平闪存的阵列结构 Fig. 2 MLC flash memory array structure | |

根据文献[17],pc(k)(x)为单元间干扰的阈值电压分布。在随机电报噪声、单元间干扰和可持久性噪声的干扰下,阈值电压的条件概率分布函数为[18]:

| $ {p^{(k)}}(x) = p_p^{(k)}(x) * p_c^{(k)}(x) * p_r^{(k)}(x) * p_t^{(k)}(x) $ | (8) |

式中:p(k)(x)表示k个状态的阈值电压分布,k∈{11,10,00,01}。为了统计出p(k)(x),需要知道式(5)中保持时间T的大小,然而在实际场景中闪存控制器没有额外的存储空间来记录保持时间[19-20]。

参照文献[8-14],MLC 闪存信道仿真参数的设置如下:μe=0.14,σe=0.25,at =0.62,a0 =0.3,At=0.000035,Bt=0.000235,γy=0.08s,γxy=0.006s。s表示电容耦合强度。

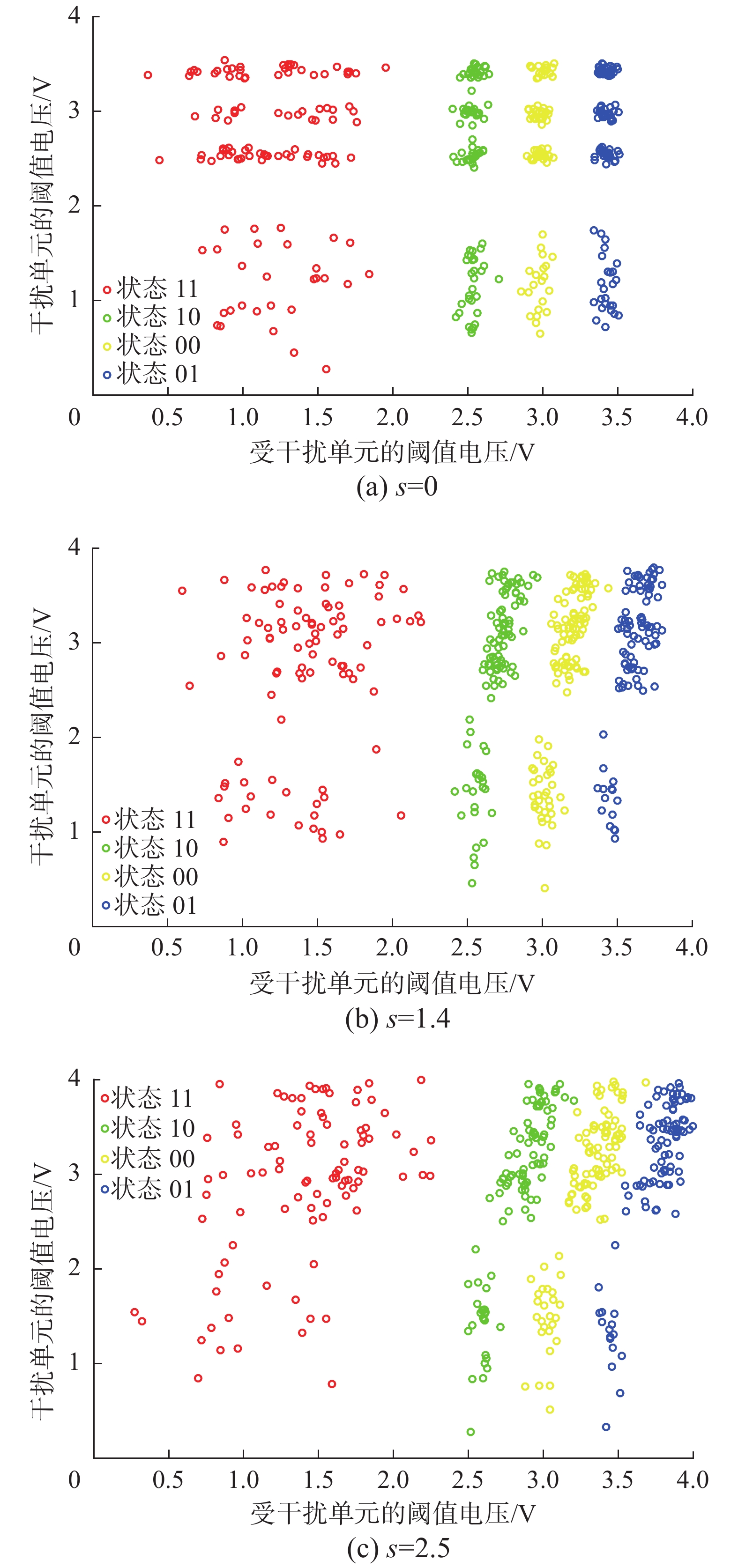

2 CNN检测器的设计 2.1 相关性闪存信道参数设置为:PE次数为1000,保持时间1年,电容耦合强度s分别为0、1.4、2.5。由图3可以发现不同状态的受干扰单元不是交错呈现,而是与干扰单元的阈值电压具有正相关关系,随着耦合强度增大,受干扰单元的阈值电压向右偏移越明显。这现象显示了单元间的阈值电压具有相关性。当观测的干扰单元越多,这种相关性越明显,但是这种现象难以精确建立数学模型。

|

Download:

|

| 图 3 闪存内部阈值电压相关性分析 Fig. 3 Schematic of the correlation analysis of the internal threshold voltage of flash memory | |

本文的主要工作是将受干扰单元字线和干扰单元字线的阈值电压组成序列,输入到CNN中进行提取特征,再输出闪存单元用于硬判决信息 (单元存储状态)和软判决信息(闪存单元属于某种状态的后验概率)。

假设每个输入序列个数为M(字线长度),每个向量为2维,序列所有阈值电压向量在矩阵V∈

卷积层:本文挑选是一维卷积神经网络,输入序列表示为[V1V2… VM]矩阵,然后使用卷积核做卷积运算:

| $ {{\boldsymbol{I}}_{(1,j)}} = {\rm{RELU}}\left( {{{\boldsymbol{k}}_{(1,j)}} * {\boldsymbol{V}} + {{\boldsymbol{b}}_{(1,j)}}} \right) $ | (9) |

式中:I(1,j)是第一层CNN第j个特征映射;k(1,j)为第j个卷积核;b(1,j)为网络偏置值,挑选的激活函数为整流线性函数(rectified linear unit, RELU)。下一层的卷积操作的输出为

| $ {{\boldsymbol{I}}_{(i,j)}} = {\rm{RELU}}\left( {{k_{(i,j)}} * V + {b_{(i,j)}}} \right) $ | (10) |

式中:I(i,j)是第i层CNN网络第j个特征映射;k(i,j)是第i层CNN网络第j个卷积核。在本工作中卷积网络池化层会丢弃一些重要的特征信息,所以本文的卷积网络由过滤器和全连接组成,并且CNN输出长度也为M。

假设有N个数据样本,对于输入样本i,经过CNN网络提取特征后,形成序列Zi=[Zi1Zi2… ZiM],希望输出每个序列节点所属某种类型的概率,即P(yim=j|Vim)。以MLC为例,其有4种状态,即j∈{VS11,VS10,VS00,VS01},m∈{1,2,…,M}。Softmax函数可以适用于多分类,其输出为

| $ \begin{aligned} {h}_{\theta }({{\boldsymbol{Z}}}_{i})&=\left[\begin{aligned} P({y}_{i}^{1}=11|{{\boldsymbol{Z}}}_{i}^{1},{\boldsymbol{\theta}} )& \cdots P({y}_{i}{}^{M}=11|{{\boldsymbol{Z}}}_{i}{}^{M},{\boldsymbol{\theta}} )\\ P({y}_{i}^{1}=10|{{\boldsymbol{Z}}}_{i}{}^{1},{\boldsymbol{\theta}} )& \cdots P({y}_{i}{}^{M}=10|{{\boldsymbol{Z}}}_{i}{}^{M},{\boldsymbol{\theta}} )\\ P({y}_{i}^{1}=00|{{\boldsymbol{Z}}}_{i}{}^{1},{\boldsymbol{\theta}} )& \cdots P({y}_{i}{}^{M}=00|{{\boldsymbol{Z}}}_{i}{}^{M},{\boldsymbol{\theta}} )\\ P({y}_{i}^{1}=01|{{\boldsymbol{Z}}}_{i}{}^{1},{\boldsymbol{\theta}} )& \cdots P({y}_{i}{}^{M}=01|{{\boldsymbol{Z}}}_{i}{}^{M},{\boldsymbol{\theta}} )\end{aligned}\right]=\\ &\quad\frac{1}{{\displaystyle \sum _{j=1}^{k}{\rm{exp}}({{\boldsymbol{\theta}} }_{j}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{j})}}\left[\begin{aligned}{{\boldsymbol{\theta}} }_{1}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{1}& \cdots {{\boldsymbol{\theta}} }_{1}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}{}^{M}\\ {{\boldsymbol{\theta}} }_{2}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{1}& \cdots {{\boldsymbol{\theta}} }_{2}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{M}\\ {{\boldsymbol{\theta}} }_{3}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{1}& \cdots{{\boldsymbol{\theta}} }_{3}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{M}\\ {{\boldsymbol{\theta}} }_{4}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{1}& \cdots {{\boldsymbol{\theta}} }_{4}^{{\rm{T}}}{{\boldsymbol{Z}}}_{i}^{M}\end{aligned}\right]\end{aligned} $ | (11) |

式中:k= 4;θ1、θ2、θ3、θ4是Softmax函数的权重参数;θ = [θ1 θ2 θ3 θ4]。对于样本i中输入序列元素Vim,属于状态标签类型j的概率为

| $ p(y_i^m = j|{\boldsymbol{Z}}_i^m) = \frac{{\exp ({\boldsymbol{\theta}} _j^{\rm{T}}{\boldsymbol{Z}}_i^m)}}{{\displaystyle\sum\limits_{m = 1}^M {\exp ({\boldsymbol{\theta}} _j^{\rm{T}}{\boldsymbol{Z}}_i^m)} }} $ | (12) |

设计好CNN检测器结构后,要对CNN网络训练,则需要从本地获得训练数据。本文采用均匀量化策略获得闪存单元中的阈值电压数据。量化数量越多检测越精确,但是也会带来读取延迟。如表1,为了权衡闪存单元电压读取延迟和可靠性,选择64-level均匀感知量化,在闪存单元状态的符号错误率(symbol error rate, SER)为0.0033时,读取延迟和可靠性折中。闪存控制器最小的读取单位是字线,则需要设置输入网络的序列长度与字线长度相当。

| 表 1 不同量化区间的SER结果 Tab.1 Simulation of SER in different quantization intervals |

实验需要采集闪存控制器中读出闪存块中每个单元的量化阈值电压和LDPC解码得到的每个单元状态信息。首先,感应和解码出若干组闪存块。其次,获得阈值电压V和状态标签x。其中,闪存单元的阈值电压在区间[Vrefi, Vrefi+1]中被惑知,Vrefi是第i个参考电压,则闪存单元的量化阈值电压

| $ {\boldsymbol{V}} = \frac{{\mathop {\boldsymbol{V}}\nolimits_{{\rm{ref}}}^i + \mathop {\boldsymbol{V}}\nolimits_{{\rm{ref}}}^{i + 1} }}{2} $ | (13) |

对于MLC闪存单元有4种不同的状态{VS11, VS10, VS00, VS01},用独热编码预处理后为

| $ \left\{{{\boldsymbol{V}}}_{S11},{{\boldsymbol{V}}}_{S10},{{\boldsymbol{V}}}_{S00},{{\boldsymbol{V}}}_{S01}\right\}=\left[\left[\begin{array}{l}1\\ 0\\ 0\\ 0\end{array}\right],\left[\begin{array}{l}0\\ 1\\ 0\\ 0\end{array}\right],\left[\begin{array}{l}0\\ 0\\ 1\\ 0\end{array}\right],\left[\begin{array}{l}0\\ 0\\ 0\\ 1\end{array}\right]\right] $ |

对于字线上的闪存单元k,简单来说,当Softmax函数输出的硬信息yk=[1 0 0 0]T时,单元k对应VS11;以此类推,当输出yk=[0 0 0 1]T,对应VS01。当输出软信息时,Softmax函数输出每个单元属于各状态的概率,CNN检测器能自适应地估计出字线中闪存单元状态概率,然后式(14)计算出对数似然比。闪存单元中的比特位bid对应的对数似然比(log-likelihood ratio, LLR)值可以被计算为

| $ \begin{array}{l} L({b_{id}}) = \hfill \mathop {}\nolimits^{} \log \frac{{\displaystyle\sum\limits_{k \in {S_{id}}} {p(y_i^m = k|Z_i^m)} }}{{\displaystyle\sum\limits_{k \in S} {p(y_i^m = k|Z_i^m) - \displaystyle\sum\limits_{k \in {S_{id}}} {p(y_i^m = k|Z_i^m)} } }} \hfill \\ \end{array} $ | (14) |

式中:Sid代表第i个闪存单元中第d比特位为1的状态集。其中,S = { VS11, VS10, VS00, VS01},S1 = {VS11, VS10},S2 = {VS11, VS01}。

4 实验仿真及分析实验仿真在Window 10操作系统下进行,采用Keras深度学习框架。在训练网络之前,假设在实验中信道的保持时间未知,就需要生成失配的验证集来测试已训练好CNN检测器的鲁棒性。定义失配时间公式为

1)闪存控制器找到第i和第i+1字线位置,即图2中的WLi和WLi+1。

2)式(13)量化WLi和WLi+1中每个单元的感应电压。

3)LDPC解码WLi中的信息,若解码成功,将独热编码预处理解码后的状态作为标签。若解码不成功,跳到下一个字线。返回1),直到获取数据集数量满足实验要求。

4)获取的数据集将用于训练CNN检测器。为了提升训练效率,将数据集分成小批量数据,分批训练CNN检测器。

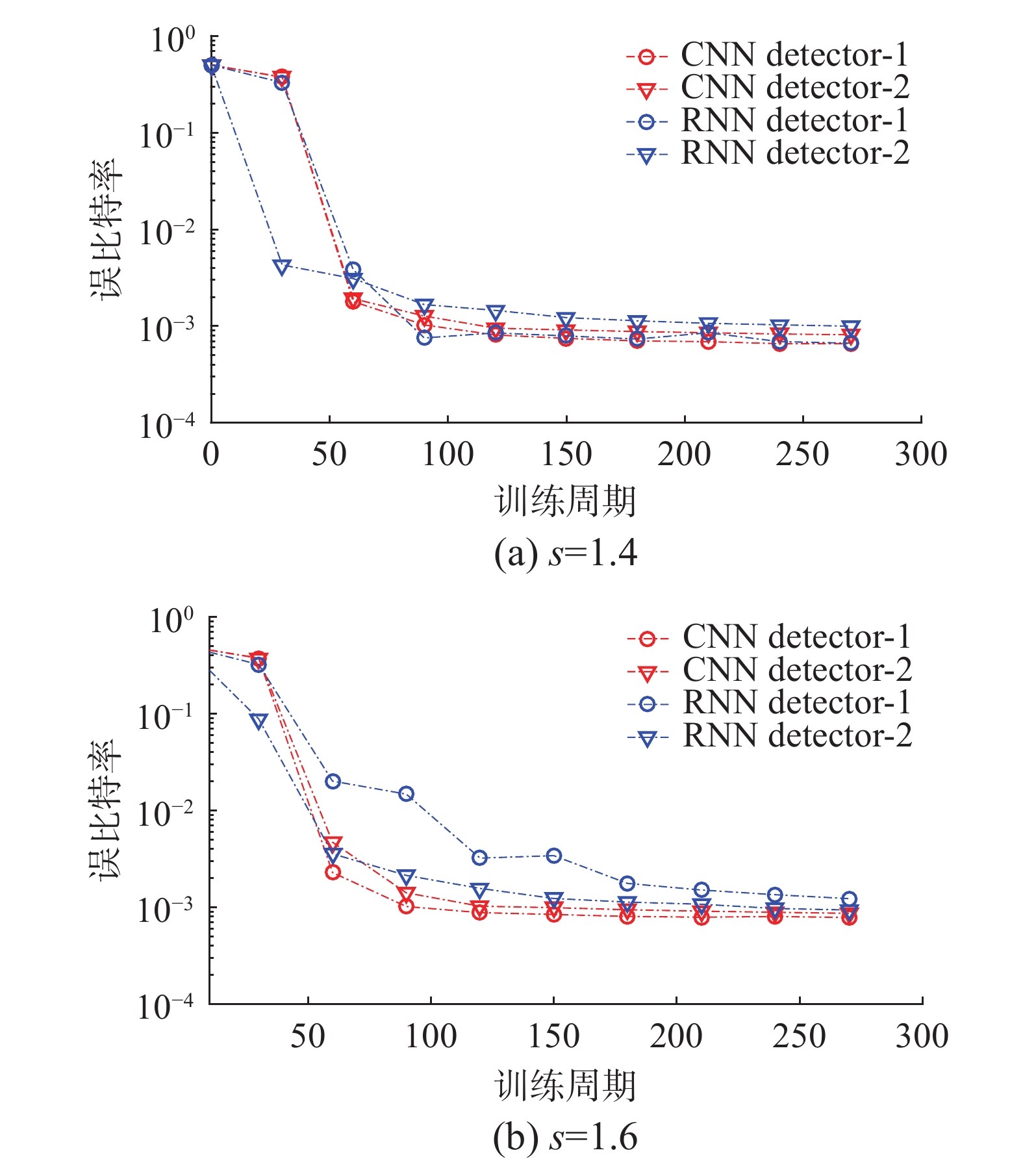

CNN结构由卷积核和特征图组成,可以表示为{L; f1, f2, …, fL; k1, k2, …, kL}。这里的L表示CNN网络层数,f表示卷积核大小,k表示特征图数量。在实验中,通过比较误比特率(bit error rate, BER)和误帧率(frame error rate, FER)来评估系统性能。先进行单层CNN和RNN的复杂度分析,然后用表2设置CNN结构来测试在原始数据和编码数据下的系统性能。

| $ {\text{误比特率}}=\frac{{\text{读取的错误比特数}}}{{\text{读取的总比特数}}} $ |

| $ {\text{误帧率}}=\frac{{\text{读取的错误帧数}}}{{\text{读取的总帧数}}} $ |

| 表 2 CNN实验设置 Tab.2 CNN experimental setup |

对于文献[8]所提出的RNN检测器,在实际的训练过程中会占用大量的时间,计算复杂度高。在理想条件下,通过设置CNN和RNN超参数使两者的复杂度相当,然后对比它们的性能。可是RNN网络要比CNN网络复杂多,在CNN网络中有加法和乘法等线性运算,而RNN网络中有许多的tanh和exp等复杂的非线性运算。为了方便比较,通过统计FLOPs来衡量网络模型的复杂度。FLOPs计算网络模型所有的加法和乘法次数。GRU是RNN网络模型中复杂度最低的网络模型。若设置一个层GRU网络的神经元个数为L,输入数据的维度为D,N表示层数,序列为T。根据文献[21],GRU模型复杂度为

| $ O\left( {\sum\limits_{i = 1}^N {{T_i}{L_i}\left( {6{D_i} + 6{L_i} + 5} \right)} } \right) $ | (15) |

根据文献[22],CNN网络模型复杂度为

| $ O\left( {\sum\limits_{i = 1}^N {2{C_{i - 1}}K_i^2{T_i}{C_i}} } \right) $ | (16) |

式中:Ci表示第i层输出数据的通道数;Ki表示第i层的卷积核大小;Ti为第i层输出的序列。在本文中C0=1,采用的二维阈值电压数据作为输入,则D1=2,K1=(D1,k);用一层CNN网络与一层GRU网络对比复杂度,则C1=1,k为第一层卷积核尺寸。Softmax函数复杂度可以忽略不计。此时,GRU网络模型复杂度为O((6L1+17

|

Download:

|

| 图 4 不同训练周期下RNN检测器和CNN检测器比特错误率比较 Fig. 4 Comparison of the BERs of the RNN and CNN detectors under different training periods | |

为了避免GPU等硬件带来的功耗等问题[8],实验在无GPU环境中进行。表3是在无GPU下参数FLOPs和每个训练周期的耗时统计。随着参数的增加,RNN检测器的FLOPs接近倍数增加,带来的计算消耗和复杂度特别大。从耗时上可以看出,CNN检测器训练周期相当于RNN检测器训练周期的四分之一。MEI提出在系统空闲时间时激活RNN检测器,但是RNN检测器训练耗时长[8]。与RNN检测器相比,CNN检测器被激活占用的系统空闲时间较短。

| 表 3 CNN检测器和RNN检测器参数个数及FLOPs Tab.3 Parameters and FLOPs of the CNN and RNN detectors |

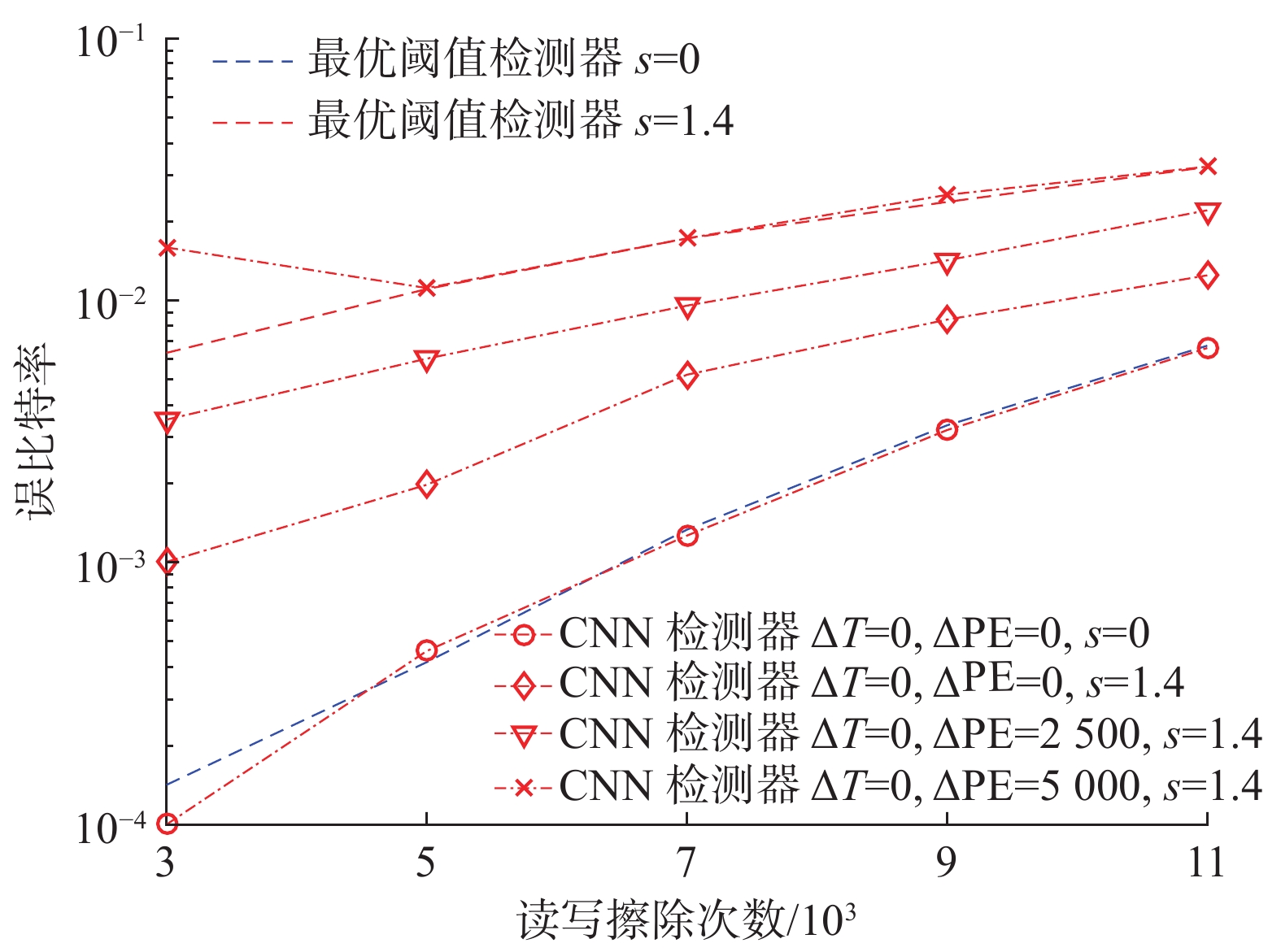

为了更好验证模型检测有效性,LDPC译码器尽可能收集解码后综合值为0的码字数据。实验中选择最优阈值为性能对比标杆。最优阈值检测器通过熵函数得到两种状态分布的重叠区间,然后在重叠区间中找到最优读取参考电压。本文的CNN检测器使用2维数据输入网络。然后,测试了有无单元间干扰下两种检测器误码率对比,s=0时,表示没有单元间干扰的信道;s=1.4时,表示3种噪声同时存在下的信道,并且单元干扰强度为1.4。

如图5所示,在实验环境中有单元间干扰情况下匹配和失配的测试集(

|

Download:

|

| 图 5 失配编程和擦除循环次数比较 Fig. 5 Programming and erase cycles by mismatching data | |

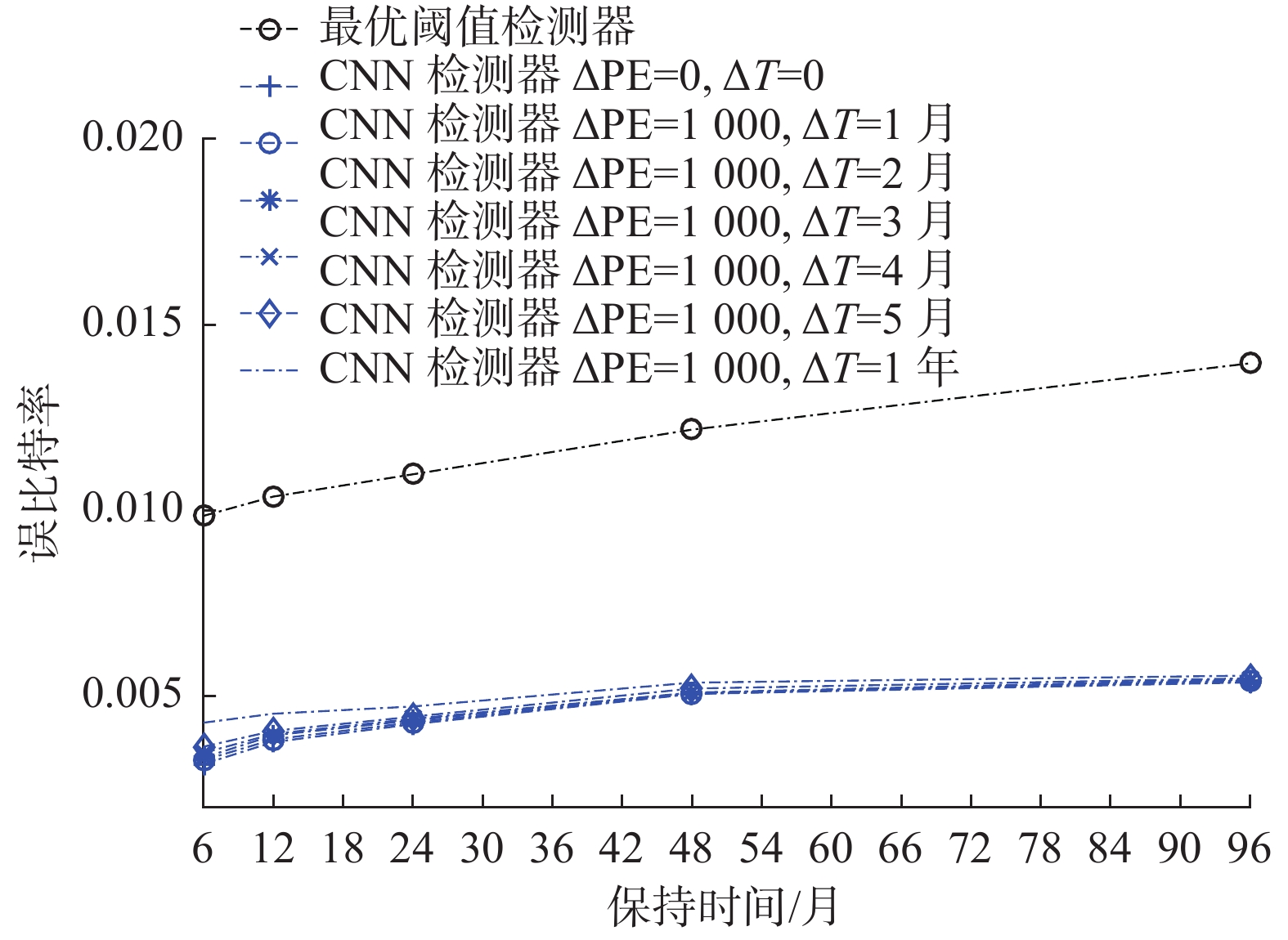

传统保持低误比特率的方法是动态更新读取参考电压。然而在未知信道信息时,闪存控制器很难记录保持时间T。这时就很难通过传统方法获得新读取参考电压。前面的实验结果证明有单元干扰下,CNN检测器优于最优阈值检测器,接下来实验通过对失配编程和擦除循环次数固定为

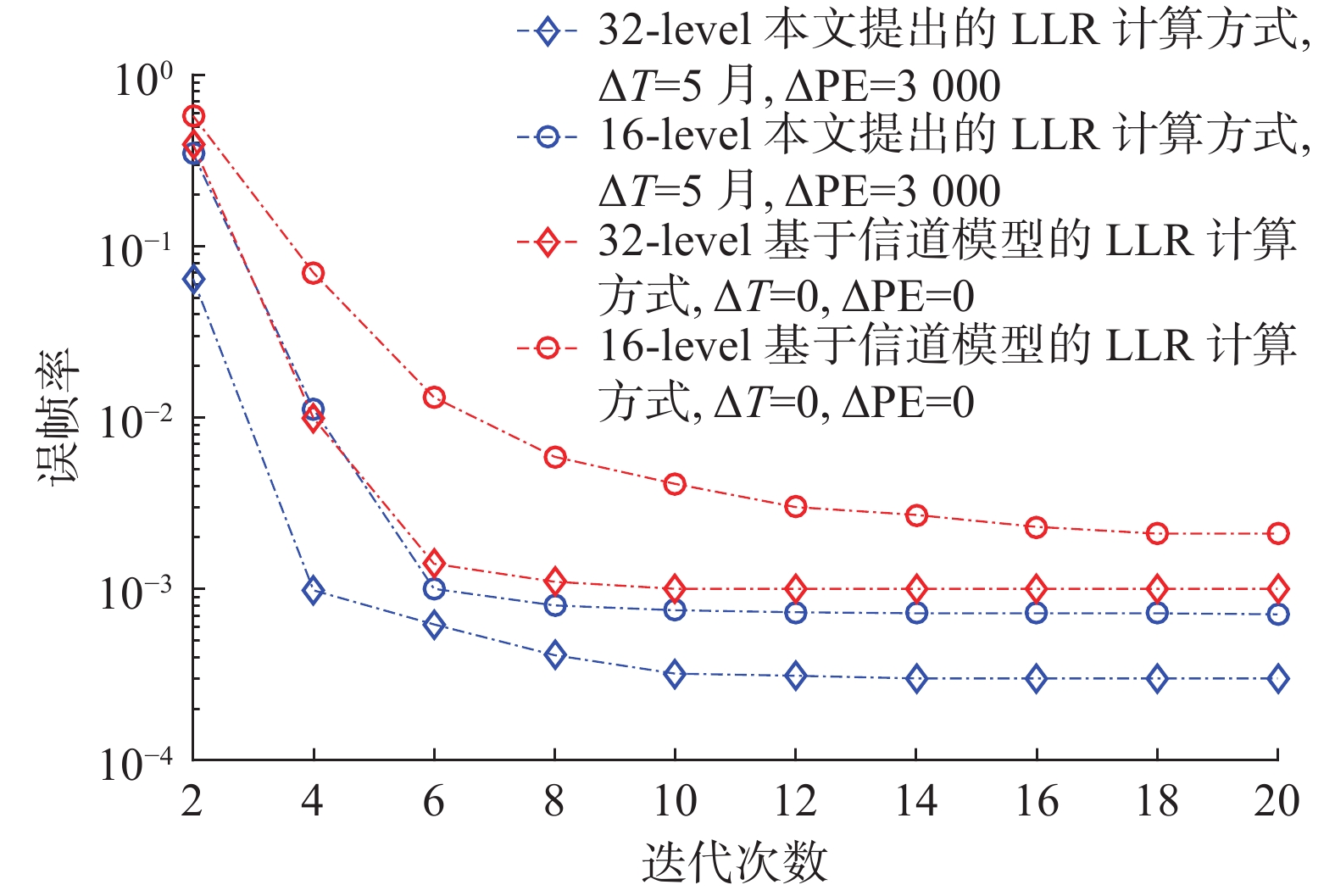

为了分析CNN检测器输出的软信息,实验选择了码率约0.889(2 048, 2304)的LDPC码写入到闪存单元中。在数据集中设置耦合强度因子为s=1.4,保持时间Ttrain=1年和读写次数PEtrain=2000。为了避免验证数产生的读取延迟,实验减少了量化电压的数量,采用16-level和32-level两种均匀量化读取方法。CNN检测器评估出闪存单元软信息,然后通过式(14)计算出LLR值。图7给出了本文提出方法与传统方法计算LLR的系统性能比较。首先,设置0~20最大迭代次数不等。其次,将CNN检测器测试的失配保持时间

|

Download:

|

| 图 6 失配保持时间比较 Fig. 6 Retention time through mismatching data | |

|

Download:

|

| 图 7 最大迭代次数比较 Fig. 7 Comparison of maximum iterations | |

针对NAND闪存存储数据可靠性下降的问题,本文提出CNN检测器,该检测器不依赖于信道先验信息,通过学习相邻单元阈值电压的相关特征,能有效检测NAND闪存单元状态。CNN检测器具有训练周期短、鲁棒性强等特点,能占用较少的系统空闲时间来适应信道变化。CNN检测器还能输出更准确的LLR信息,提升BP译码算法的纠错性能。闪存信道检测在深度学习中可以看作分类问题,因此本文提出的方法也可以应用到TLC、QLC闪存信道中。

| [1] |

范正勤, 韩国军. 多电平闪存信道下阈值电压高效检测算法[J]. 应用科技, 2019, 46(5): 57-62. FAN Zhengqin, HAN Guojun. High-efficiency detection algorithm for threshold voltage in multi-level cell NAND flash memory[J]. Applied science and technology, 2019, 46(5): 57-62. (  0) 0)

|

| [2] |

张旋, 慕建君, 焦晓鹏. 面向MLC闪存的比特翻转译码算法研究[J]. 哈尔滨工程大学学报, 2019, 40(2): 331-337. ZHANG Xuan, MU Jianjun, JIAO Xiaopeng. Improved bit-flipping decoding algorithm for MLC flash memory[J]. Journal of Harbin Engineering University, 2019, 40(2): 331-337. (  0) 0)

|

| [3] |

郑敏华, 韩国军. 融合相邻单元高低页存储可靠性的闪存译码算法[J]. 应用科技, 2020, 47(3): 17-23. ZHENG Minhua, HAN Guojun. An improved decoding algorithm for NAND flash memory fusing the storage reliability of upper and lower pages of adjacent cells[J]. Applied science and technology, 2020, 47(3): 17-23. (  0) 0)

|

| [4] |

LIU Xingcheng, YANG Guojun, CHEN Xuechen. Variable-node-based belief-propagation decoding with message pre-processing for NAND flash memory[J]. IEEE access, 2019, 7: 58638-58653. DOI:10.1109/ACCESS.2019.2914076 ( 0) 0)

|

| [5] |

PENG Zishuai, HE Ruiquan, HAN Guojun, et al. Neighbor-a-posteriori information assisted cell-state adaptive detector for NAND flash memory[J]. IEEE communications letters, 2019, 23(11): 1967-1971. DOI:10.1109/LCOMM.2019.2936342 ( 0) 0)

|

| [6] |

KIM T, KONG G, XI Weiya, et al. Cell-to-cell interference compensation schemes using reduced symbol pattern of interfering cells for MLC NAND flash memory[J]. IEEE transactions on magnetics, 2013, 49(6): 2569-2573. DOI:10.1109/TMAG.2013.2251417 ( 0) 0)

|

| [7] |

DONG Guiqiang, XIE Ningde, ZHANG Tong. On the use of soft-decision error-correction codes in NAND flash memory[J]. IEEE transactions on circuits and systems I:regular papers, 2011, 58(2): 429-439. DOI:10.1109/TCSI.2010.2071990 ( 0) 0)

|

| [8] |

MEI Zhen, CAI Kui, HE Xuan. Deep learning-aided dynamic read thresholds design for multi-level-cell flash memories[J]. IEEE transactions on communications, 2020, 68(5): 2850-2862. DOI:10.1109/TCOMM.2020.2974723 ( 0) 0)

|

| [9] |

FAN Zhengqin, CAI Guofa, HAN Guojun, et al. Cell-state-distribution-assisted threshold voltage detector for NAND flash memory[J]. IEEE communications letters, 2019, 23(4): 576-579. DOI:10.1109/LCOMM.2019.2900677 ( 0) 0)

|

| [10] |

SANDELL M, ISMAIL A. Machine learning for LLR estimation in flash memory with LDPC codes[J]. IEEE transactions on circuits and systems II:express briefs, 2021, 68(2): 792-796. DOI:10.1109/TCSII.2020.3016979 ( 0) 0)

|

| [11] |

CHOE H, JEE J, LIM S C, et al. Machine-learning-based read reference voltage estimation for NAND flash memory systems without knowledge of retention time[J]. IEEE access, 2020, 8: 176416-176429. DOI:10.1109/ACCESS.2020.3026232 ( 0) 0)

|

| [12] |

NAKAMURA T, DEGUCHI Y, TAKEUCHI K. Adaptive artificial neural network-coupled LDPC ECC as universal solution for 3-D and 2-D, charge-trap and floating-gate NAND flash memories[J]. IEEE journal of solid-state circuits, 2019, 54(3): 745-754. DOI:10.1109/JSSC.2018.2884949 ( 0) 0)

|

| [13] |

LIANG Fei, SHEN Cong, WU Feng. An iterative BP-CNN architecture for channel decoding[J]. IEEE journal of selected topics in signal processing, 2018, 12(1): 144-159. DOI:10.1109/JSTSP.2018.2794062 ( 0) 0)

|

| [14] |

ASLAM C A, GUAN Yongliang, CAI Kui. Decision-directed retention-failure recovery with channel update for MLC NAND flash memory[J]. IEEE transactions on circuits and systems I:regular papers, 2018, 65(1): 353-365. DOI:10.1109/TCSI.2017.2714902 ( 0) 0)

|

| [15] |

DONG Guiqiang, XIE Ningde, ZHANG Tong. Enabling NAND flash memory use soft-decision error correction codes at minimal read latency overhead[J]. IEEE transactions on circuits and systems I:regular papers, 2013, 60(9): 2412-2421. DOI:10.1109/TCSI.2013.2244361 ( 0) 0)

|

| [16] |

ASLAM C A, GUAN Yongliang, CAI Kui. Read and write voltage signal optimization for multi-level-cell (MLC) NAND flash memory[J]. IEEE transactions on communications, 2016, 64(4): 1613-1623. DOI:10.1109/TCOMM.2016.2533498 ( 0) 0)

|

| [17] |

DONG Guiqiang, LI Shu, ZHANG Tong. Using data postcompensation and predistortion to tolerate cell-to-cell interference in MLC NAND flash memory[J]. IEEE transactions on circuits and systems I:regular papers, 2010, 57(10): 2718-2728. DOI:10.1109/TCSI.2010.2046966 ( 0) 0)

|

| [18] |

OUYANG Shijie, HAN Guojun, FANG Yi, et al. LLR-distribution-based non-uniform quantization for RBI-MSD algorithm in MLC flash memory[J]. IEEE communications letters, 2018, 22(1): 45-48. DOI:10.1109/LCOMM.2017.2755023 ( 0) 0)

|

| [19] |

CAI Yu, LUO Yixin, HARATSCH E F, et al. Data retention in MLC NAND flash memory: characterization, optimization, and recovery[C]//2015 IEEE 21st International Symposium on High Performance Computer Architecture (HPCA). Burlingame, USA, 2015: 551−563.

( 0) 0)

|

| [20] |

HE Ruiquan, HU Haihua, XIONG Chunru, et al. Artificial neural network assisted error correction for MLC NAND flash memory[J]. Micromachines, 2021, 12(8): 879. DOI:10.3390/mi12080879 ( 0) 0)

|

| [21] |

ZHANG Pengfei, XUE Jianru, LAN Cuiling, et al. EleAtt-RNN: adding attentiveness to neurons in recurrent neural networks[J]. IEEE transactions on image processing, 2020, 29: 1061-1073. DOI:10.1109/TIP.2019.2937724 ( 0) 0)

|

| [22] |

CAO Congzhe, LI Duanshun, FAIR I. Deep learning-based decoding of constrained sequence codes[J]. IEEE journal on selected areas in communications, 2019, 37(11): 2532-2543. DOI:10.1109/JSAC.2019.2933954 ( 0) 0)

|

| [23] |

张旋, 慕建君, 焦晓鹏. 基于错误特征的MLC闪存最小和译码算法[J]. 系统工程与电子技术, 2019, 41(8): 1887-1895. ZHANG Xuan, MU Jianjun, JIAO Xiaopeng. Min-sum decoding algorithm based on error characteristics for MLC flash memory[J]. Systems engineering and electronics, 2019, 41(8): 1887-1895. DOI:10.3969/j.issn.1001-506X.2019.08.29 (  0) 0)

|

| [24] |

张旋, 周乐, 侯爱华. 一种适用于MLC闪存的CCI噪声均衡化算法[J]. 计算机科学, 2018, 45(S1): 541-544. ZHANG Xuan, ZHOU Le, HOU Aihua. CCI noise equalization algorithm for MLC flash memory[J]. Computer science, 2018, 45(S1): 541-544. (  0) 0)

|

2021, Vol. 16

2021, Vol. 16