在一个大型水下系统中,针对不同分系统的特性,通常采用不同的通信协议。串行通信具有抗干扰能力强,传输距离远等特点,适用于需要远距离通信的分系统;MIL-STD-1553B总线在传输方面具有极强的可靠性和实时性,适用于对信号准确性和实时性要求高的惯导及发控分系统[1]。

DSP可以快速处理数据且具有较高的集成性和稳定性,目前已成为控制领域主流的处理芯片[2]。但DSP的片内通信资源有限且固定,会导致系统的可扩展性不强,且若DSP频繁响应中断,也会对其工作的效率产生影响。

FPGA与DSP相比具有以下优点:支持并行操作,可以同时处理多个工作单元,可以实现数据的实时传输[3];FPGA可以通过自身编程实现传统设计中逻辑接口,从而使得外围电路设计的难度大大减小,减少硬件设计难度,且系统的可扩展性得到极大的提高。

本文以DSP芯片作为主处理器,负责应用层的设计以及整个系统运行时信息的调度,采用FPGA作为系统的协处理器,完成对多路RS-422串口信号的采集以及对数据的缓存,同时使用FPGA实现BU61580的功能并根据项目需要对功能进行扩展,完成1553B总线接口模块的设计。

1 系统总体设计主要实现16路串口数据的发送及接收,以及2路1553B数据的发送及接收,后期根据需要可扩展CAN通信及429通信等。在进行设计时,要充分考虑如何实现不同控制芯片之间准确、高速、实时的通信问题。DSP选择TI公司的处理器芯片TMS320F28335,该芯片低成本,高性能,运算能力强、精度高。但该芯片的串口资源只有3个,不满足设计要求,且若采用DSP+BU-61580的结构实现在BC模式下的1553B通信,根据设计要求,系统需要发送大量周期为5ms和10ms的周期信号,若周期信号的发送由DSP控制,则DSP需要频繁响应计时中断,会影响芯片的数据处理速度,且可能造成数据丢失等现象。

为了解决这些问题,选用低功耗型XC7K325T[4]芯片完成对DSP功能的扩展。DSP与FPGA之间通过XINTF总线进行数据交互,从而实现DSP对外围芯片的控制,使得DSP的功能得到最优的发挥[5],XINTF总线包括数据线、地址线及片选线等。

RS422总线接口设计,以FPGA芯片为核心进行搭建。接口驱动芯片均选用ADM2682E,该芯片内有隔离,无需外部隔离处理。通过FPGA实现总线控制器(BC)的功能。使用HI-1573将1553B总线信号转化为FPGA可以处理的3.3V差分信号。

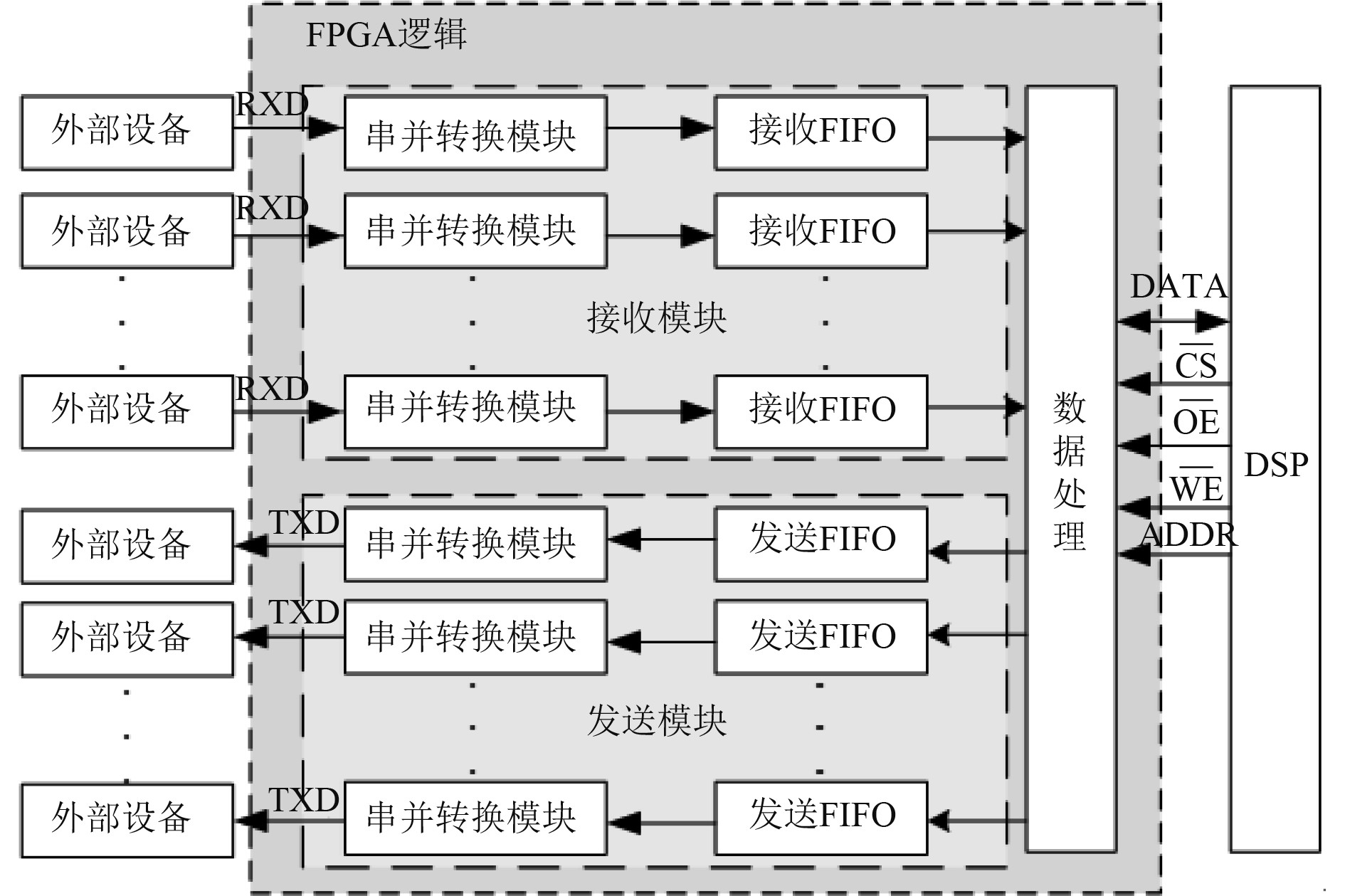

2 FPGA逻辑设计 2.1 多路串口逻辑设计RS422通信电路采用模块化设计。FPGA的功能逻辑如图1所示,从功能上划分为接收模块、发送模块以及数据处理模块。考虑到不同的外部设备对串口通信的要求各不相同,为了提高模块的普遍性,每一路串口通道都具有独立性,可以通过DSP对每一路串口的属性进行分别的设置,也即每一路串口的波特率,数据位,奇偶校验位,停止位等均可以通过编程进行设置。

|

图 1 串口逻辑设计 Fig. 1 Serial port logic design |

|

图 4 示波器抓取周期信号图 Fig. 4 Schematic diagram of Oscilloscope |

1)收发FIFO缓存数据

FIFO一般用于处理高速异步的数据交互和数据缓存。收发FIFO采用8×256的容量,数据位宽度为8位,存储深度为256byte。FIFO_empty作为FIFO是否有数据的标志信号。

2)串并转换FPGA

通过状态机完成将串行数据转换为并行数据的功能。系统上电复位后状态机进入Idle状态,当收到数据时,状态机进入Start状态;检测到串行数据的起始位后状态机进入Receive状态否则退回Idle状态;Receive状态主要进行数据位的接收,不同通道可以接收不同位数的数据位,当循环接收数据位个数满足通道要求后,进入下一个状态[6];若串口协议中有校验位,则进入Parity状态,判断奇偶校验,否则状态机进入Stop bit状态。Stop状态可以进行停止位的接收,当接收的停止位符合要求后,状态机将已转换为并行的数据存入接收FIFO中,并重回Idle状态。

系统上电进行复位后状态机进入Idle状态,当发送FIFO的fifo_empty=’0’时,状态机进入Start状态,否则仍然处于Idle状态;完成起始位的发送后,状态机进入Sample状态,读取FIFO中的数据并进行采样,将数据转换为高低电平后,状态机进入Transmit状态,发送串行数据,并发送停止位;发送完成后进入Stop状态完成整个发送流程。

3)数据处理及与DSP的通信

FPGA为每一路通道分配不同的片选地址,DSP在对通道进行初始化及收发数据时,要根据片选地址找到对应的寄存器并通过总线收发不同地址中的数据,从而进行相应的数据处理。根据系统流程,当需要获取某一路串口的数据时,DSP读取该通道对应的fifo empty状态,若不为空,则DSP从该通道存放数据的寄存器地址中,获取已经过串并转换的数据。反之,若需要发送指令至某一通道时,DSP通过总线将打包好的带帧头帧尾的数据发送至相应的FPGA寄存器,FPGA将数据存入对应通道的发送FIFO,通过串并转换后将FIFO中的数据转为串行码发送至外部设备[7]。

2.2 1553B逻辑设计信息融合系统作为系统的中心,在1553B通信中担任总线控制器(BC)的角色,负责收发数据,同时还需要对整个流程进行调度。根据流程,信息融合系统需要通过发送周期和非周期信号对分系统下发指令并获取分系统的反馈信号。为了提高DSP的工作精度及效率,对于周期信号,DSP只控制信号发送的启停,也即当DSP对FPGA下发了某条周期信号的启动指令后,FPGA自动对该条指令计时,当时间到达周期时,FPGA控制发送指令,直到DSP下发该条指令的停止指令。所以信息融合系统需要完成的工作包括:准确发送命令字和数据字;准确接收数据字和状态字;根据需要在不同时期发送不同周期长度的周期性信号及非周期信号。因此在对信息融合系统的BC功能进行设计时,主要分为以下功能模块:发送模块、接收模块、流程控制模块。

2.2.1 发送、接收模块发送及接收模块包括发送部分、接收部分、超时检测部分等[8]。

发送部分:主要功能是将数据经过曼彻斯特编码后发送,根据解析出的数据字个数开始计数,当数据字个数达到规定值时,发送完毕[9]。发送的数据包括同步头类型、指令字及数据字[10]。

接收部分:BC主要接收状态字和数据字,通过解码状态字判断接收的数据字是否正确。FPGA将收到的数据字放在特定的RAM地址中,根据流程,DSP在特定时间读取RAM地址中的数据字,从而获得分系统反馈的数据和状态。

发送超时检测:为保证总线传输的可靠性,协议规定发送时长超过800 us的信息按超时处理。通过计时器进行超时检测,当接收到指令字的同步头时开始计时,接收到状态字时计时结束,一旦计数值超过800 us,则表示发送超时。

BC模式下接口的响应流程如图2所示。

|

图 2 BC模式下的响应流程 Fig. 2 Response process in BC mode |

信息融合系统在1553B通信中不仅需要完成BC的基本收发功能,还需要对系统运行的整个流程进行调度。具体来说,FPGA通过状态机实现流程控制的主程序。

3 功能验证 3.1 多通道串口板级验证通过CCS软件和串口调试助手可完成串口在线测试。对通道ID为0的通道进行收发测试,该通道采用115 200 bit/s波特率,串口助手向0通道发送5f,f5,01,02,03,04,05,06,07,08,2a,5b时DSP可以收到。反之,DSP通过0通道向外发送数据时,串口助手也可收到数据。其他15路串口也根据对应的串口协议进行测试,数据收发正常。

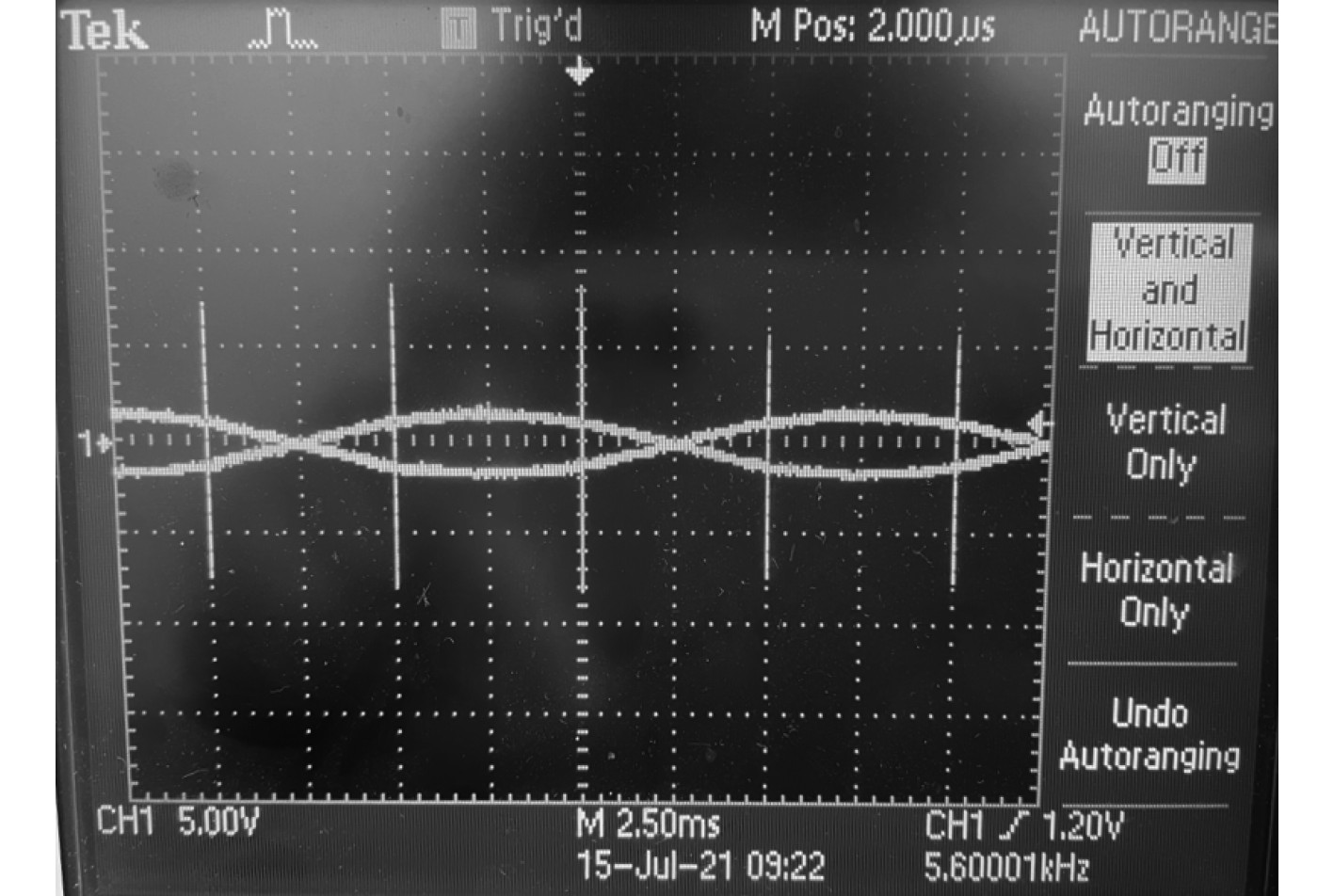

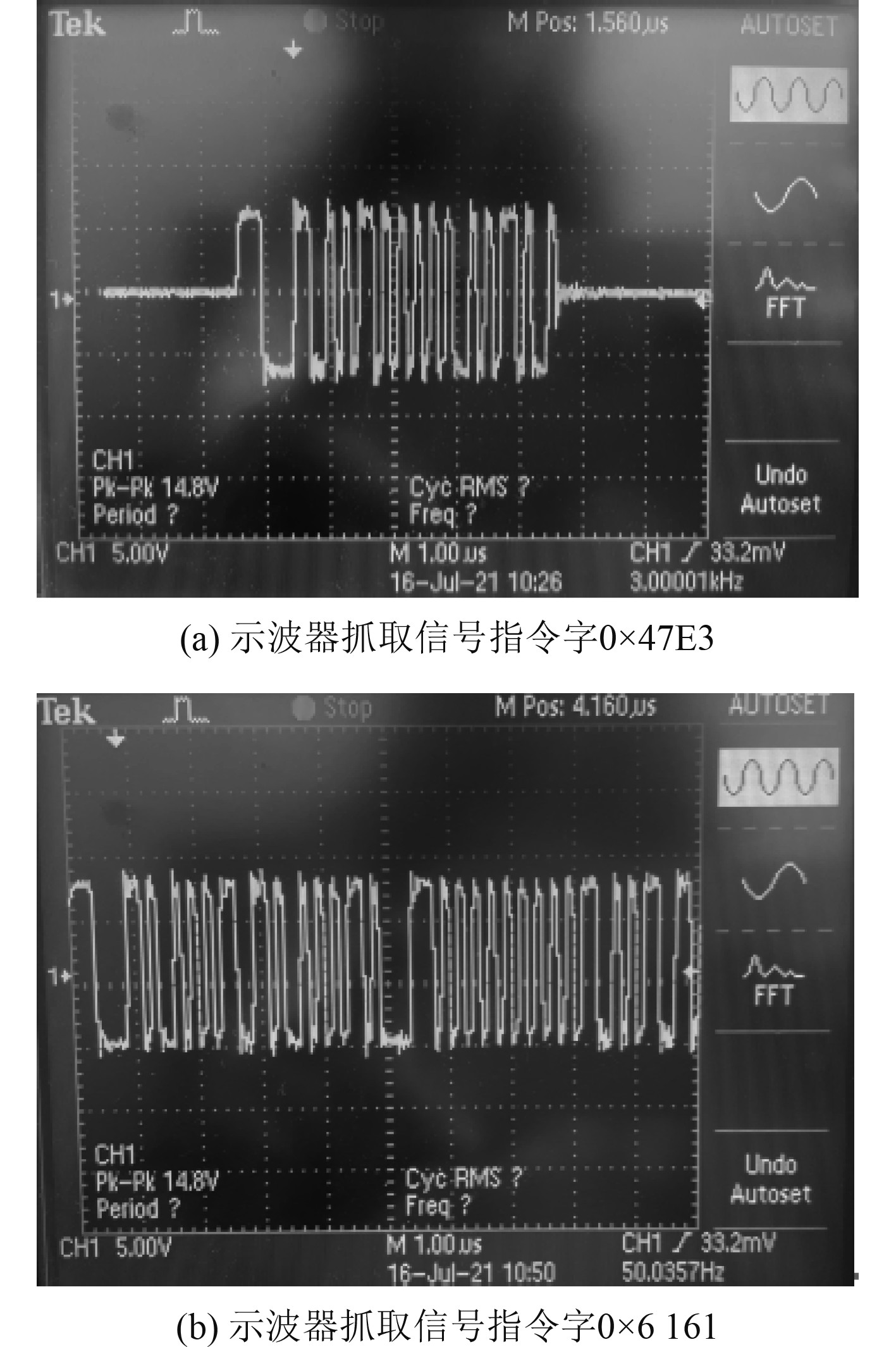

3.2 1553B板级验证 3.2.1 BC发送非周期信号用CCS软件和BM软件完成在线测试,通过示波器观察波形。图3为在BC模式下1553B模块发送信号的波形,可以看出波形良好,受干扰影响小,可以正确进行信号解码。

|

图 3 主波器抓取信号图 Fig. 3 Schematic diagram of oscilloscope |

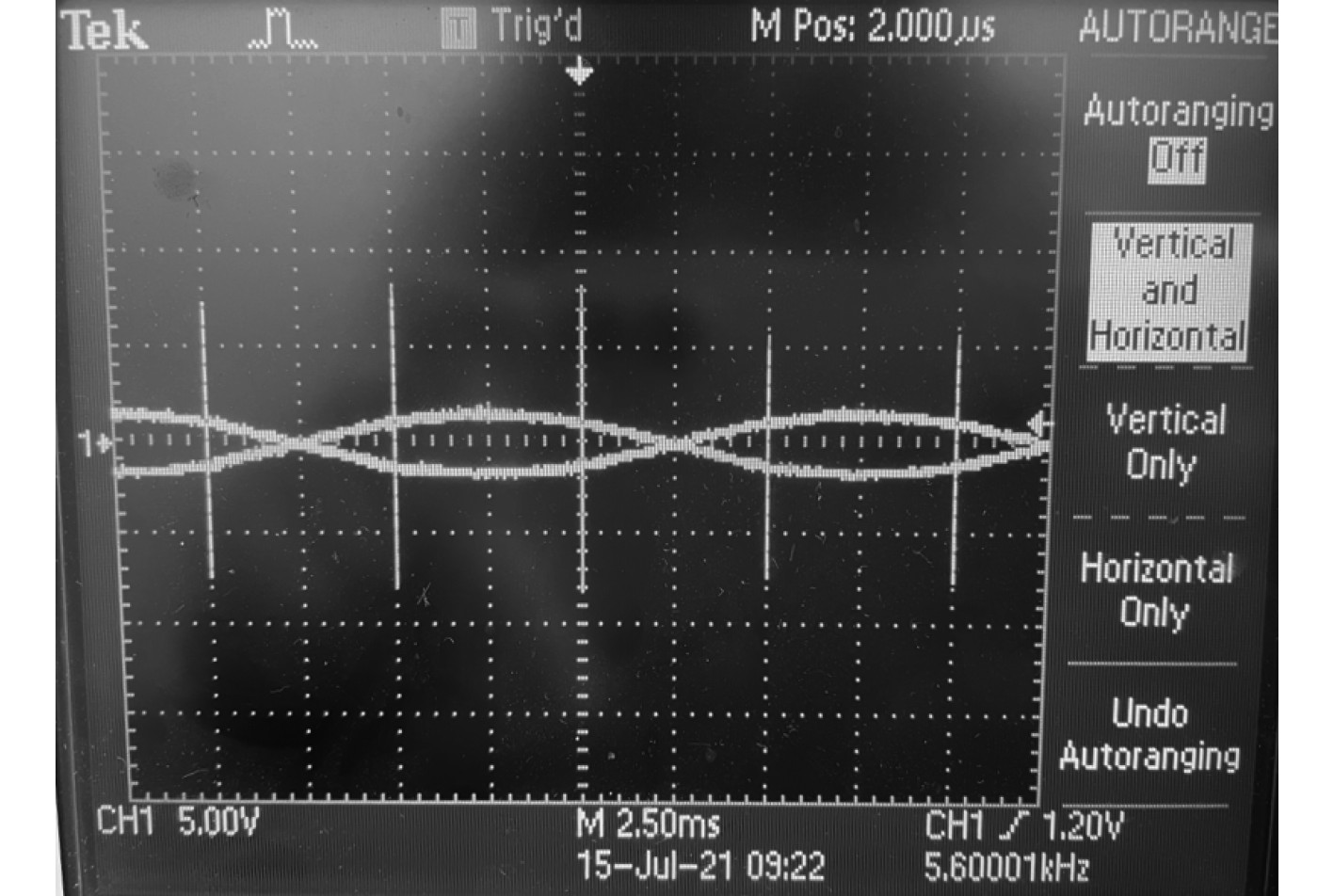

BC向RT发送指令字为0×6 161,数据字为0×0 022的周期消息,周期为5 ms,图4为实测波形图,横坐标每格为2.5 ms。可以看出,周期信号的周期为5 ms。

|

图 4 示波器抓取周期信号图 Fig. 4 Schematic diagram of Oscilloscope |

本文采用DSP+FPGA的设计实现信息融合系统在多通道串口和1553B通信中的应用。有以下特点:1) 灵活性。基于FPGA进行设计,可根据现场流程的改变随时修改程序。2) 扩展性。不用考虑资源限制,可根据需要增减通道,并且根据需求可以增加更多的通信协议。3) 稳定性。模块化的设计,各通道各协议间的工作互不影响,有利于系统的改进和验证。4) 高效性。FPGA采用并行数据传送,便于多通道数据交互。本设计已应用于某大型项目的设备中,经过大量测试和试验,可以稳定满足使用要求。

| [1] |

杨旭, 黄建国, 杨尚明, 等. 基于BU-61580的航空1553B总线RT模式设计[J]. 数字技术与应用, 2012(1): 60-62. YANG Xu, HUANG Jian-guo, YANG Shang-ming, LI li. RT mode design of aviation 1553B bus based on bu-61580[J]. Digital Technology & Application, 2012(1): 60-62. |

| [2] |

王晓惠, 陈艳杰, 曹威. 数字信号处理器的船舶碰撞监控报警系统[J]. 舰船科学技术, 2021, 43(12): 40-42. WANG Xiao-hui, CHEN Yan-jie, CAO Wei. Ship collision monitoring and alarm system based on DSP[J]. Ship Science and Technology, 2021, 43(12): 40-42. |

| [3] |

徐洋洋. 基于FPGA的多通道大容量FIFO设计[J]. 电子测量技术, 2017, 40(8): 193-197. XU Yang-yang. Design of multi-channel FIFO with mass storage facility based on FPGA[J]. Electronic Measurement Technology, 2017, 40(8): 193-197. DOI:10.3969/j.issn.1002-7300.2017.08.043 |

| [4] |

韩刚, 蔡旭. 虚拟同步发电机输出阻抗建模与弱电网适应性研究[J]. 电力自动化设备, 2017, 37(12): 116-122. HAN Gang, CAI Xu. Output impedance modeling of virtual synchronous generator and its adaptability study in a weak grid[J]. Electric Power Automation Equipment, 2017, 37(12): 116-122. |

| [5] |

刘冬利, 兰慧. 基于DSP与FPGA的LPI辐射源信号仿真系统[J]. 舰船科学技术, 2020, 42(11): 124-127. LIU Dong-li, LAN Hui. A LPI radar emitter signal simulation system based on DSP and FPGA[J]. Ship Science and Technology, 2020, 42(11): 124-127. DOI:10.3404/j.issn.1672-7649.2020.11.025 |

| [6] |

朱鹏程, 胡娜. 基于APU+FPGA的机载视频和通讯总线处理系统设计[J]. 电光与控制, 2021, 28(5): 98-102. ZHU Peng-Cheng, HU Na. Design of an Airborne Video and Communication Bus Processing System Based on APU+FPGA[J]. Electronics Optics & Control, 2021, 28(5): 98-102. DOI:10.3969/j.issn.1671-637X.2021.05.022 |

| [7] |

李昕. 基于国产处理器的打印控制SoC的设计与实现[D]. 西安: 西安电子科技大学, 2019.

|

| [8] |

李贵娇, 鲁争艳, 房建峰. 基于FPGA的1553B总线远程终端设计[J]. 电子测量技术, 2020, 43(5): 97-101. LI Jiao-gui, LU Zheng-yan, FANG jian-feng. Design of 1553B bus remote terminal based on FPGA[J]. Electronic Measurement Technology, 2020, 43(5): 97-101. |

| [9] |

张吉康, 刘恩海, 魏宏刚, 等. MIL-STD-1553B总线曼彻斯特编解码器的FPGA实现[J]. 电子设计工程, 2019, 27(15): 103-107. ZHANG Ji-kang, LIU En-hai, WEI Hong-gang, ZHAO Ru-jin. The implement of manchester coder in MIL-STD-1553B bus based on FPGA[J]. Electronic Design Engineering, 2019, 27(15): 103-107. DOI:10.3969/j.issn.1674-6236.2019.15.022 |

| [10] |

闫昌浩. 基于DSP和1553B总线的嵌入式通讯模块设计[J]. 科技信息, 2011(22): 219. YAN Chang-hao. Design of embedded communication module based on DSP and 1553B bus[J]. Science & Technology Information, 2011(22): 219. DOI:10.3969/j.issn.1001-9960.2011.22.192 |

2022, Vol. 44

2022, Vol. 44