2. 山西职业技术学院,山西 太原 030031

2. Shanxi Polytechnic College, Taiyuan 030031, China

船舶导航雷达在航行过程中可以进行方向引导、避撞、定位等功能,具有非常广泛的应用,导航雷达的工作过程不受雨、雪、雾等气象条件的影响,是船舶不可缺少的助航设备之一。

由于导航雷达的回波信号中夹杂着多种噪声干扰信号,雷达数字信号处理机必须要具备相应的噪声滤波和信号提取能力[1]。本文研究的对象是导航雷达数字信号处理机的相关设计。

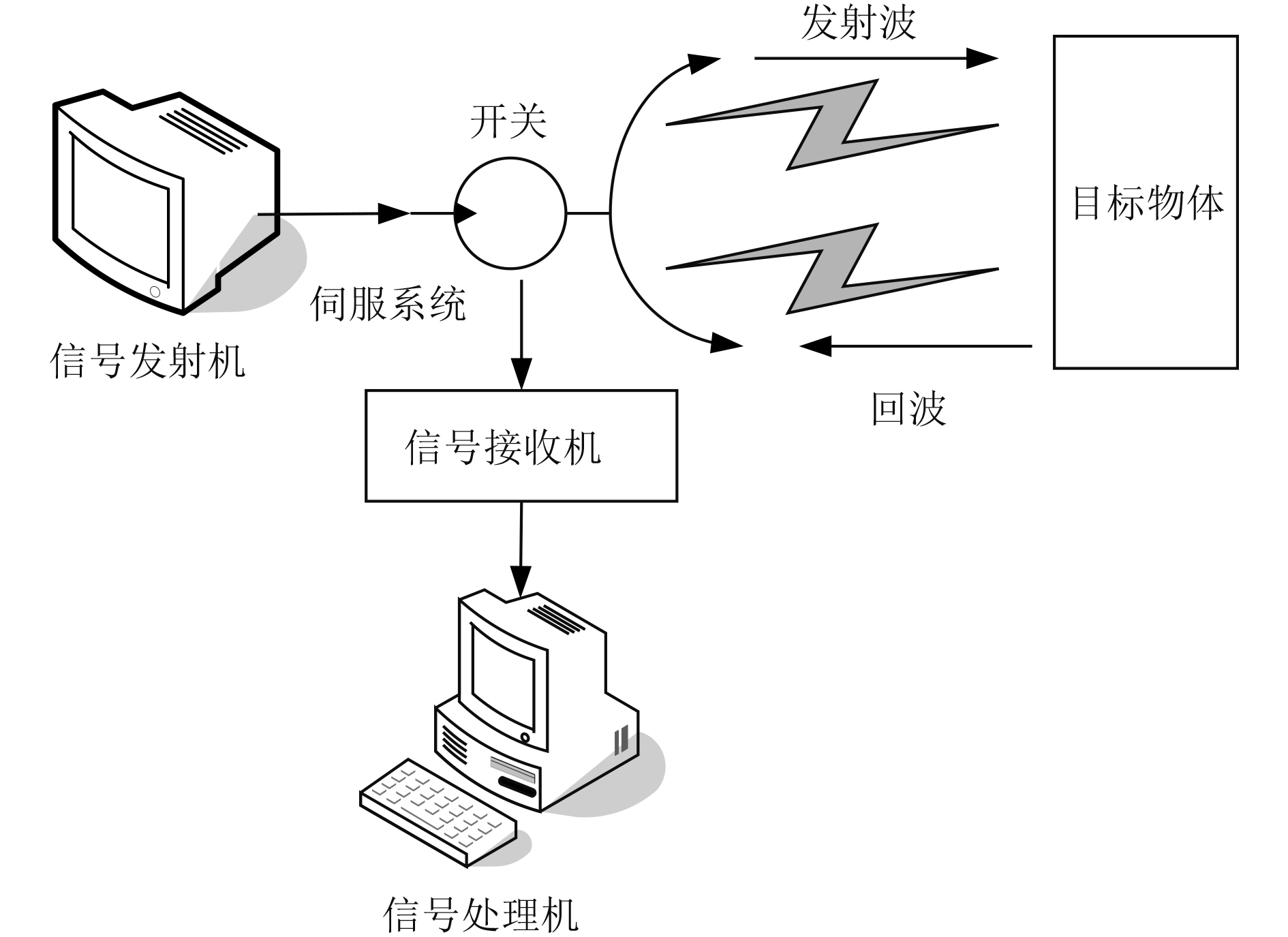

1 船舶导航雷达数字信号处理机工作原理及方案 1.1 船舶导航雷达工作原理目前,超过80%以上的船舶导航雷达为非相参脉冲雷达,雷达信号发射机向一定范围发射脉冲电波信号,信号经过目标反射后由天线接收,进入雷达信号处理机。图1为船舶导航雷达系统的工作原理。

|

图 1 船舶导航雷达系统的工作原理图 Fig. 1 Working principle of ship navigation radar system |

导航雷达的伺服系统主要功能是控制雷达信号发射机的机械扫描过程,根据被测目标的实际尺寸、距离等参数,输出较合理的信号发射机角度和工况。

信号接收机的功能是采集雷达的回波信号,并进行信号的基本处理,比如信号的放大、变频等,信号放大器又包括射频放大器、中频放大器等。

信号处理机对采集的雷达回波信号进行噪声过滤和处理,提取回波信号中的有效成分,并将目标特征信息发送至终端显示。此外,信号处理机也是雷达系统的控制中心,负责导航雷达系统整体性能的监测和控制。

1.2 船舶导航雷达数字信号处理机的方案设计雷达信号处理技术经历了较长时间的发展,目前,船舶雷达信号处理机从原理上可以分为模拟电路处理机和数字信号处理机,模拟电路处理机硬件设施较多,处理精度相对较低,数字信号处理机目前已经成为了主流的导航雷达信号处理方法[2]。

本文根据导航雷达的信号特性,将信号的数字处理分为以下2种方式:

1)视频段数字处理

这种信号处理方式只对回波信号的幅值进行信号处理,信号处理速度快,但对A/D转换的精度要求较低,缺少回波信号中的频率信息和相位信息,造成目标精度较低。

2)中频段数字处理

随着船舶导航雷达技术的进步,目前,导航雷达的工作频率一般都是1.0 GHz以上,采用传统的A/D器件难以满足信号转换的需求,因此进行雷达信号高速数字处理时必须要配置高速A/D转换器件,这也造成了信号处理机的成本增加。针对这一问题,最佳的解决方法是利用雷达中频信号进行目标探测。由于雷达中频信号的频率达到几十MHz,普通的A/D转换器就可以满足要求。

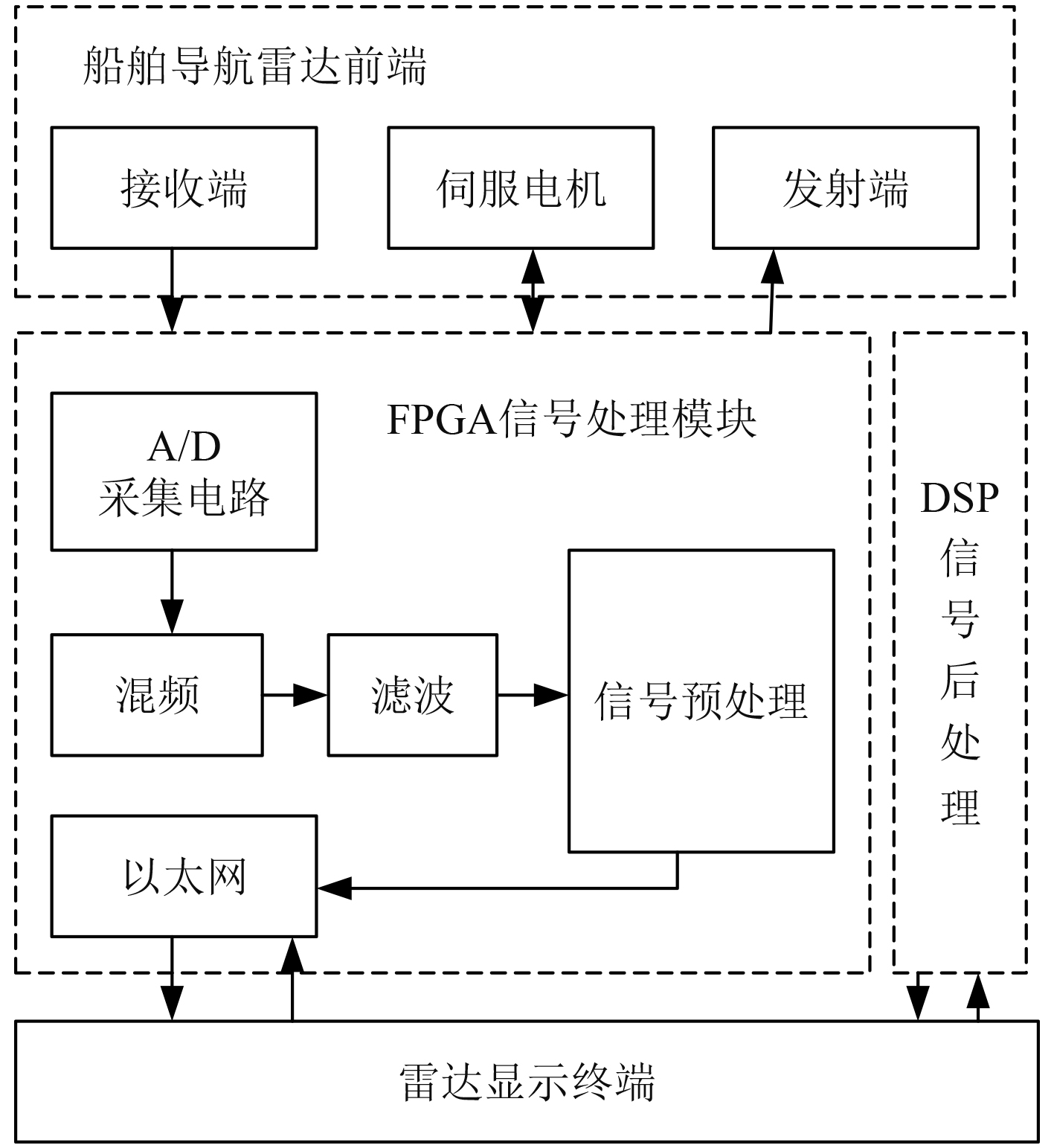

本文设计的导航雷达系统的数字信号处理机基本方案如图2所示。

|

图 2 导航雷达系统的数字信号处理机原理图 Fig. 2 Schematic diagram of digital signal processor of navigation radar system |

导航雷达系统的数字信号处理机主要由导航雷达前端、FPGA、显示终端和DSP信号后处理4个部分组成。

1)导航雷达前端

导航雷达前端主要包括雷达脉冲信号的发射端和接收端,以及用于雷达天线方位调节的伺服电机等设备。

2)FPGA信号处理模块

FPGA信号处理模块是数字信号处理机的核心,包括信号采集电路、信号处理、混频、滤波等功能,采用的FPGA芯片为EP2C35F672D。该芯片采用90 nm制造工艺,集成了3万个以上的逻辑控制单元,内嵌18*18位乘法器和16 kb存储器件,计算性能良好,能够满足雷达系统中频信号数字处理的要求。

3)DSP信号后处理

该模块为雷达中频信号的后处理模块,选用的DSP芯片为Blackfin -532芯片。该芯片的内核包括2枚处理器,采用dual-MAC数据运算引擎,可以实现导航雷达中频信号的加密、分类等后处理任务。

2 船舶导航雷达数字信号处理机的FPGA电路设计优化 2.1 导航雷达数字信号处理机的信号采集电路设计信号采集和数模转换是进行雷达信号处理的基本前提,采用的A/D转换器芯片为AD7792/3高精度转换芯片,可根据雷达导航系统的信号频率选择AD7792/3的工作模式。

雷达回波信号经过A/D转换后需要进行调频,建立调频信号模型:

| $ f(x) = \frac{{{A_0}}}{{{\eta ^2}}}\exp \left( { - \frac{{{x^2}}}{{2{\eta ^3}}}} \right) \text{。} $ |

式中:

进一步可得雷达调频信号的概率密度函数[4]为:

| $ {f_2}\left( x \right) = \frac{1}{{\sqrt {2{\text{π}}} \lambda x}}\exp \frac{{ - {{\ln }^2}\left( {\dfrac{x}{b}} \right)}}{{2{\lambda ^2}}} \text{,} $ |

式中,

在FPGA信号处理模块中,为了提高雷达噪声信号的信噪比,需要采用脉冲压缩的方式进行信号处理,脉冲压缩函数为:

| $ Z\left( t \right) = A \cdot {\rm{rect}} \left( {\frac{t}{\chi }} \right)\exp \left( {2{\text{π}} {f_0} + \frac{\alpha }{2}{t^2}} \right) \text{。} $ |

式中:

脉冲压缩函数的频域模型为:

| $ H\left( f \right) = \int\nolimits_{ - \infty }^\infty {x\left( t \right){e^{ - j2{\text{π}} ft}}{\rm{d}}t} 。$ |

雷达数字信号处理机中,FPGA信号处理模块需要处理的信号量非常大,且信号处理完成后需要暂时寄存在该模块中再进行后处理,而不是直接在终端显示,因此雷达数字信号处理机的存储器需要具有较大的容量和较快的读写速度。

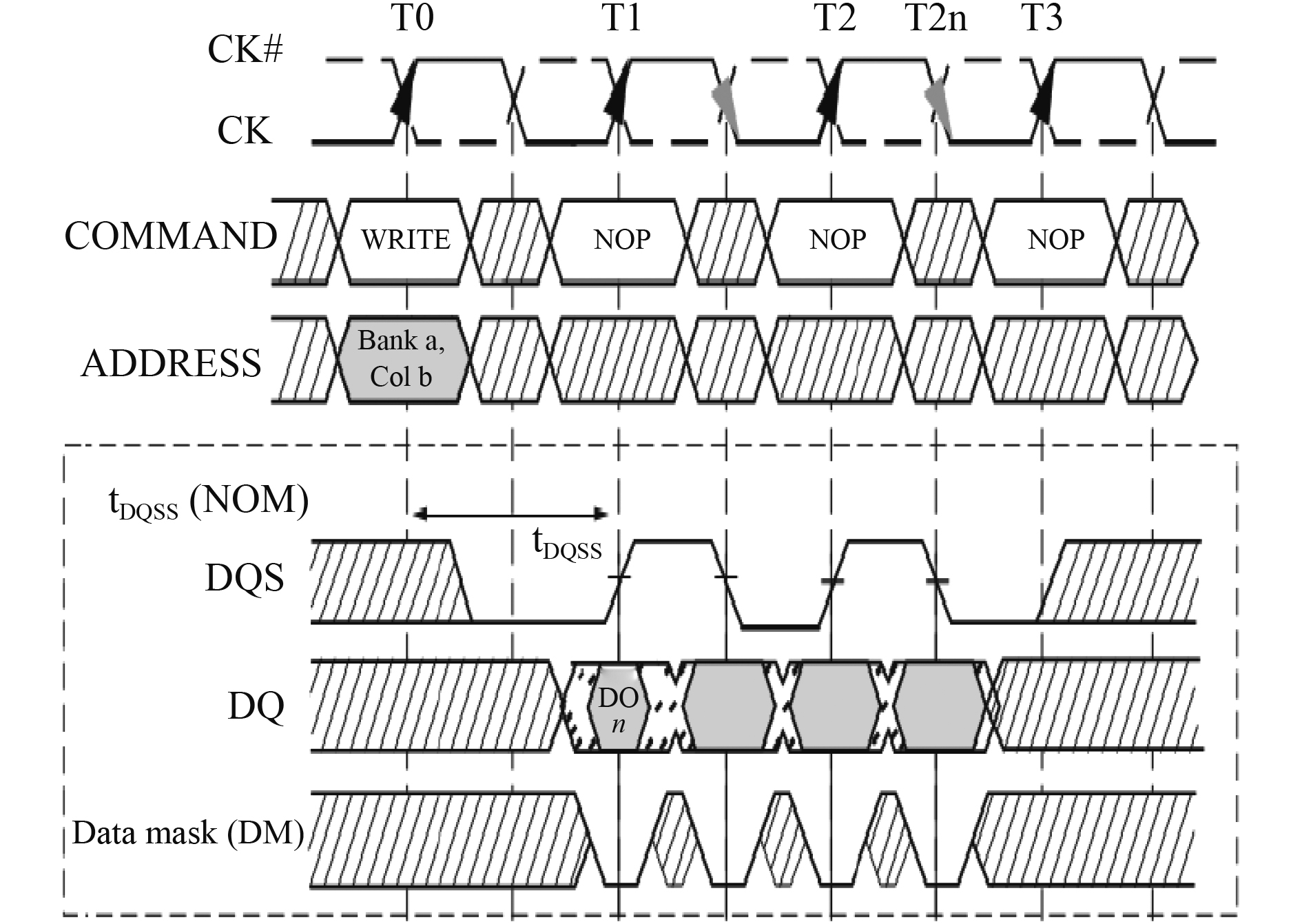

采用DDR SDRAM作为雷达信号的存储器,DDR SDRAM的集成度高,性能强,它的读写时序图见图3。

|

图 3 DDR SDRAM读写时序图 Fig. 3 DDR SDRAM read / write sequence diagram |

在DDR SDRAM 写入时,DQS的正沿必须与CK/CK#正沿保持一致,有效数据与DQS的跳变沿对齐[3]。

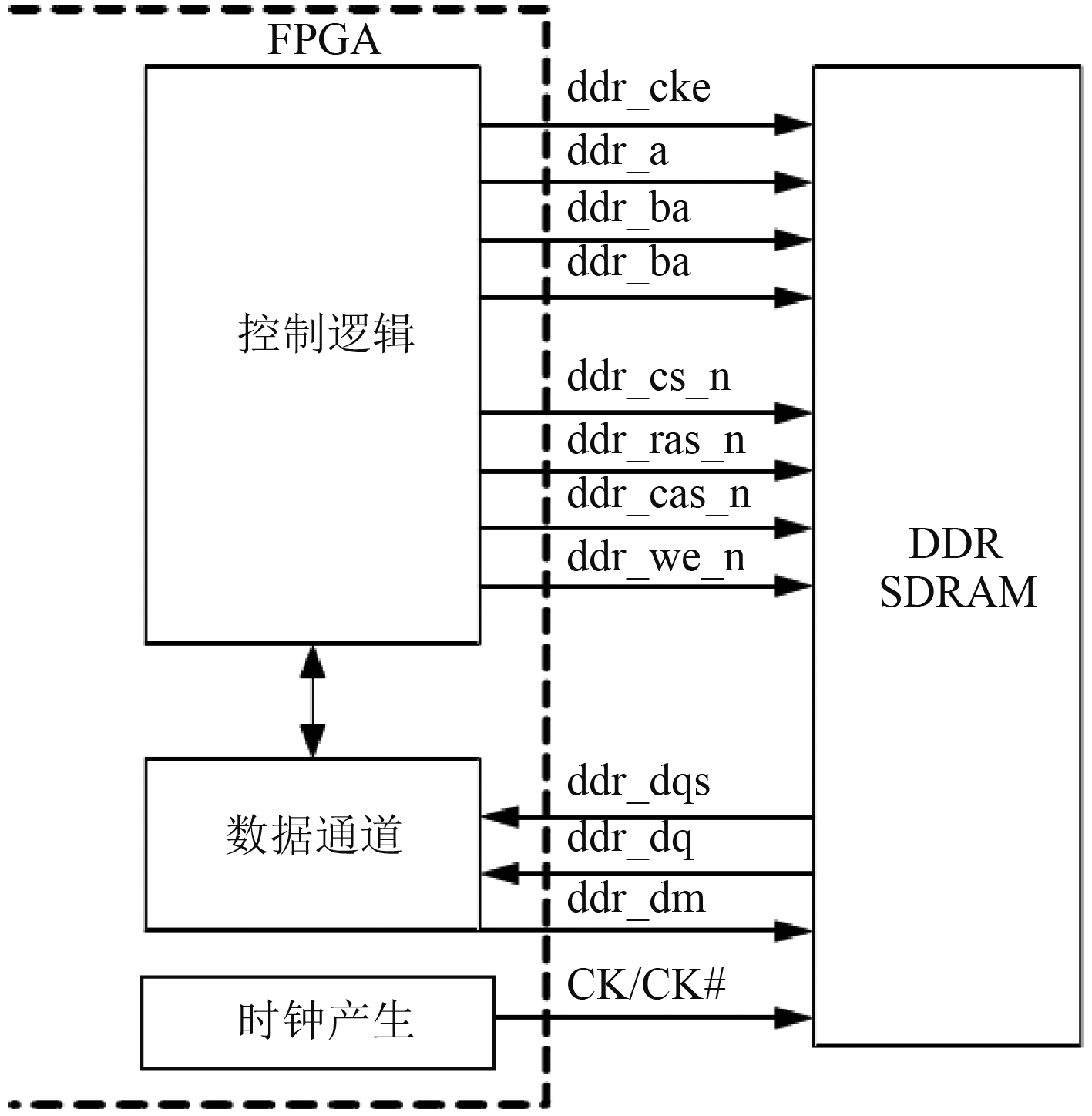

设计的DDR SDRAM与FPGA接口电路见图4。

|

图 4 DDR SDRAM与FPGA接口电路图 Fig. 4 DDR SDRAM and FPGA interface circuit diagram |

在该接口电路中,DDR SDRAM的输入引脚为CK/CK#,FPGA的I/O单元输出信号的地址,CK/CK#的正沿与 DQS正沿对齐,CK/CK#和 DQS的内部信号采用相同时钟。

2.3 雷达数字信号处理机的时钟电路设计时钟信号是FPGA与DDR-SDRAM进行信号传输的关键,为了保证雷达信号处理机工作时钟的稳定性,本文选择50 MHz的有源晶振作为基准频率,时钟电路采用3 V有源电压供电。

3 船舶雷达数字信号处理机的噪声滤波优化在FPGA信号处理模块中,雷达信号经过信号调频和压缩可以初步过滤系统的白噪声等干扰信号,但是雷达信号中仍然存在一些其他杂波干扰,常见的雷达信号杂波干扰包括地杂波信号和海杂波信号等。

1)地杂波信号

地杂波信号与雷达系统的信号覆盖面积和散射系数有关,通常,地杂波信号的强度会随着目标的移动而变化,且目标越远[5],地杂波信号的强度越高,建立地杂波信号模型为:

| $ {\sigma _{{\text{land}}}}(t) = \sum\limits_{t = 1}^n {\left( {\frac{{{\kappa _{{\text{land}}}}\sqrt {2s(t)\Delta w} \sin (wt + \theta )}}{2}} \right)} \text{。} $ |

其中:

地杂波信号的瑞利分布概率密度函数如下式:

| $ {\lambda _{LAND}}\left( t \right) = \frac{t}{{{b^2}}}\exp \left[ {\frac{{{{\left( {t - 1} \right)}^2}}}{{2{b^2}}}} \right]\;\;,t > 0 \text{。} $ |

式中:b为瑞利系数;t的均值为

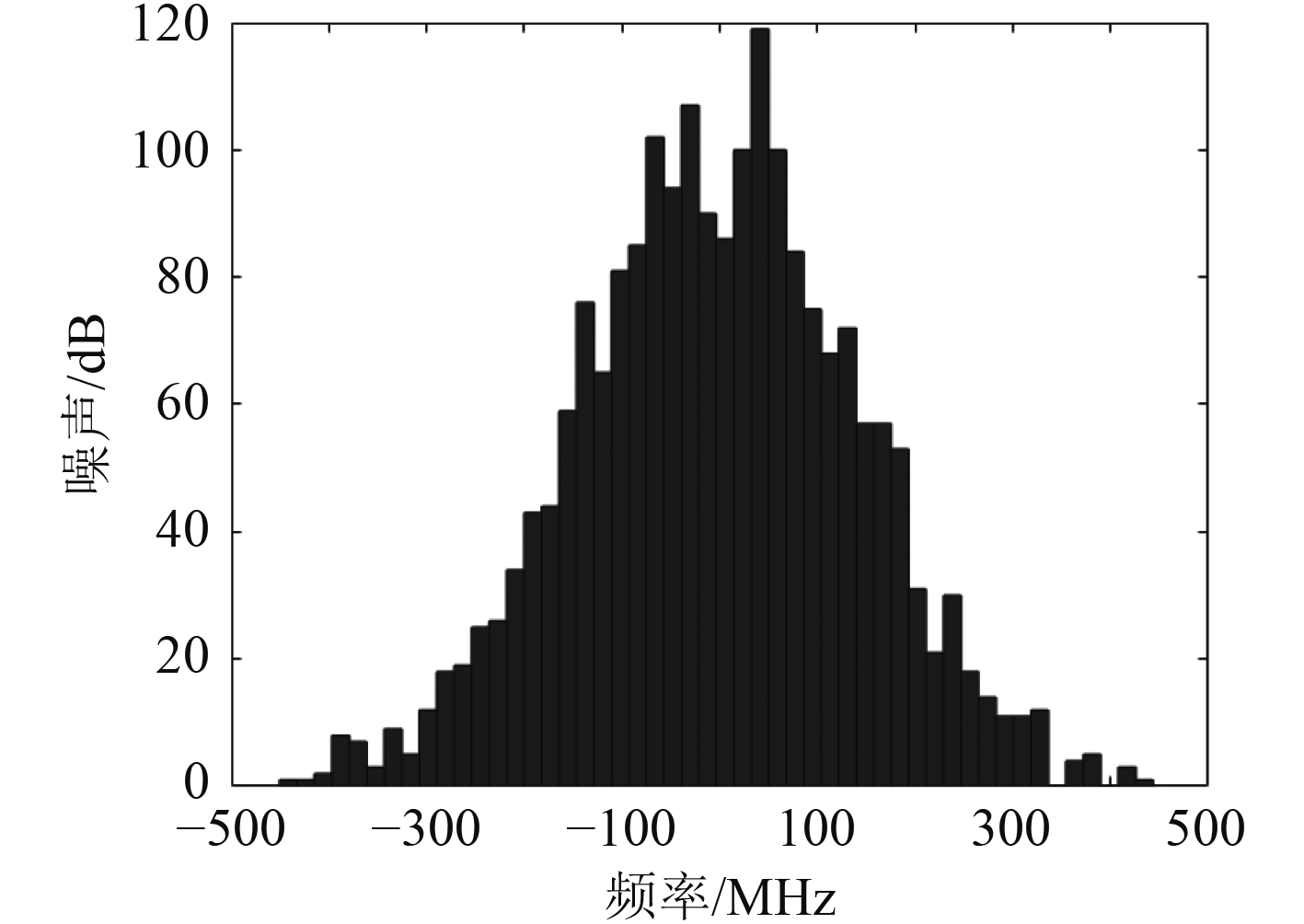

地杂波噪声的概率分布见图5。

|

图 5 地杂波噪声的概率分布图 Fig. 5 Probability distribution of ground clutter noise |

2)海杂波信号

海杂波信号模型为:

| $ {\sigma _{sea}}(t) = {A_{sea}} \cdot \sum\limits_{t = 1}^n {\cos \left( {\frac{{2\pi }}{\lambda }\left( {Y\cos {w_1} + X\sin {w_1}} \right)} \right)} \text{。} $ |

式中:

定义雷达信号的信噪比如下:

| $ SNR = 10 \cdot \log \left( {\frac{{E\left( {y{{\left( n \right)}^2}} \right)}}{{E\left( {{{\left( {y\left( n \right) - \sigma (n)} \right)}^2}} \right)}}} \right) \text{。} $ |

其中:

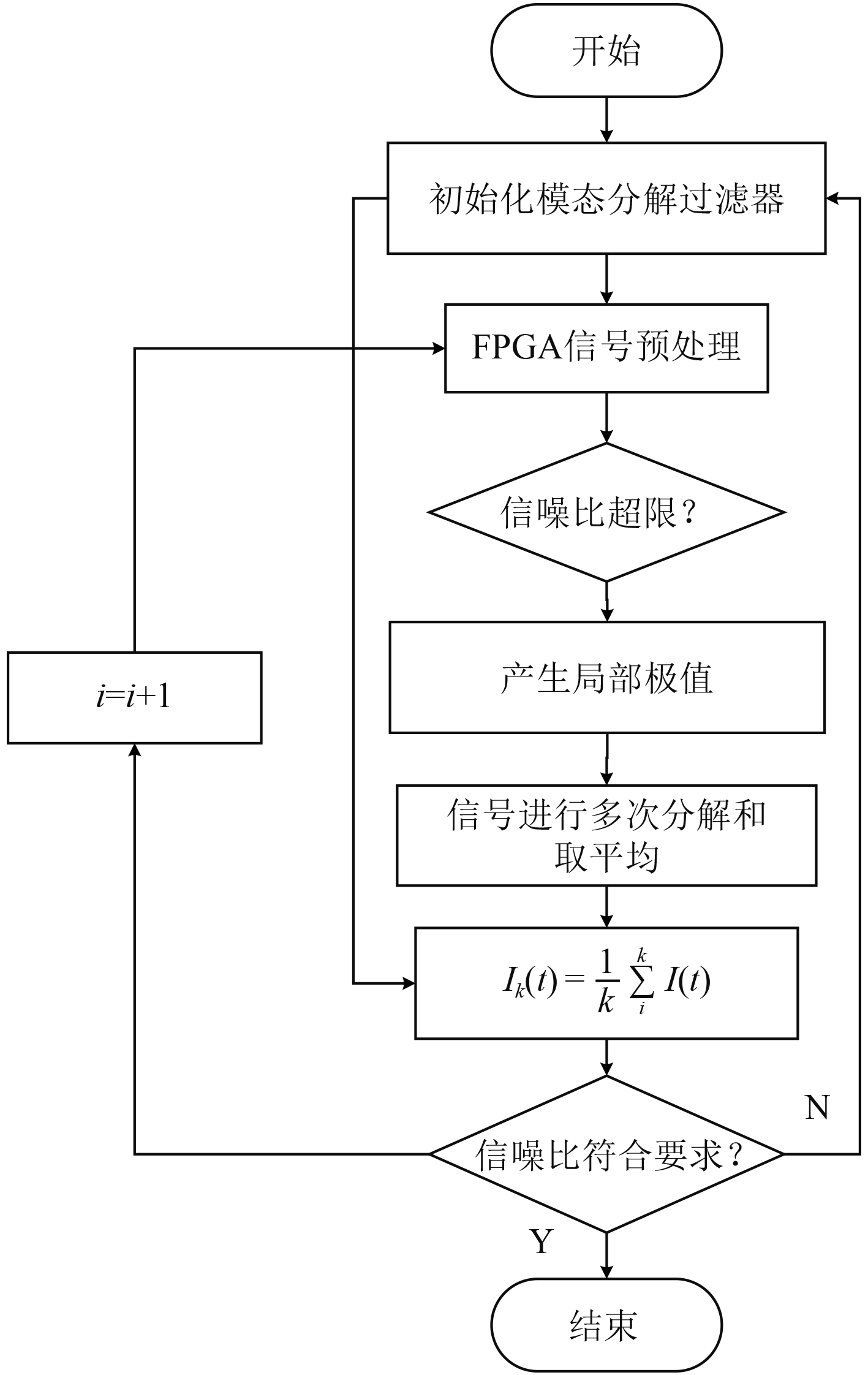

基于模态分解方法进行地杂波信号、海杂波信号的过滤,依据信号本身的时间尺度特征完成信号分解,基于模态分解方法的雷达信号处理流程如图6所示。

|

图 6 基于模态分解方法的雷达信号处理流程 Fig. 6 Radar signal processing flow based on modal decomposition method |

| [1] |

高磊, 黄兴玉, 余小强, 等. 机载测云雷达信号处理系统研制难点分析[J]. 电子世界, 2018(5): 2. |

| [2] |

吴三元, 王英, 刘尚富. 某雷达信号处理机的设计[J]. 舰船电子工程, 2009(5): 3. |

| [3] |

李嵩, 王强. 716改雷达信号处理分系统的分析与检修[J]. 气象水文装备, 2005, 16(4): 55-57. |

| [4] |

王党卫. 一种直扩信号快速捕获方法研究及实现[J]. 导航, 2008, 44(2): 4. |

| [5] |

李明理, 杨钏钏. ARPA导航雷达控制系统电压监视功能设计[J]. 电子科技, 2014, 27(11): 4. |

| [6] |

宋文, 闫修林. 某脉组参差体制雷达信号处理机设计[J]. 指挥信息系统与技术, 2010, 1(5): 3. |

2001, Vol. 44

2001, Vol. 44