2. 中国科学院大学,北京 100049;

3. 北京市海洋声学装备工程技术研究中心,北京 100190

2. University of Chinese Academy of Sciences, Beijing 100049, China;

3. Beijing Engineering Technology Research Center of Ocean Acoustic Equipment, Beijing 100190, China

声学多普勒测速声呐是目前最主要的流速测量仪器之一,一次测量可获得剖面内多个深度的流速,底跟踪速度和底深等数据,因此广泛用于舰船和水下航行器的定位导航、海洋流场监测,以及内陆河流流量测验等领域。近年来,随着我国海洋技术的快速发展,水下载体的低功耗、小型化和网络化成为一个主要的发展方向,急需研发能够适应于这些载体导航需求的低功耗、小型化声学多普勒测速声呐。目前系统硬件电路是制约声学多普勒测速声呐小型化和低功耗的主要因素,因此如何提高电路的集成度成为解决问题的关键。本文基于集成模拟前端(AFE)设计的多普勒测速声呐接收机,可有效降低接收机电路板面积,降低系统功耗,内部集成的数字正交解调模块取代传统多普勒测速声呐采用的模拟正交解调,可有效降低零漂和测量误差。

1 AFE接收机电路组成AFE接收机实现四通道回波信号的接收、放大、滤波、模数转换、数字正交解调、低通抽取滤波等功能。

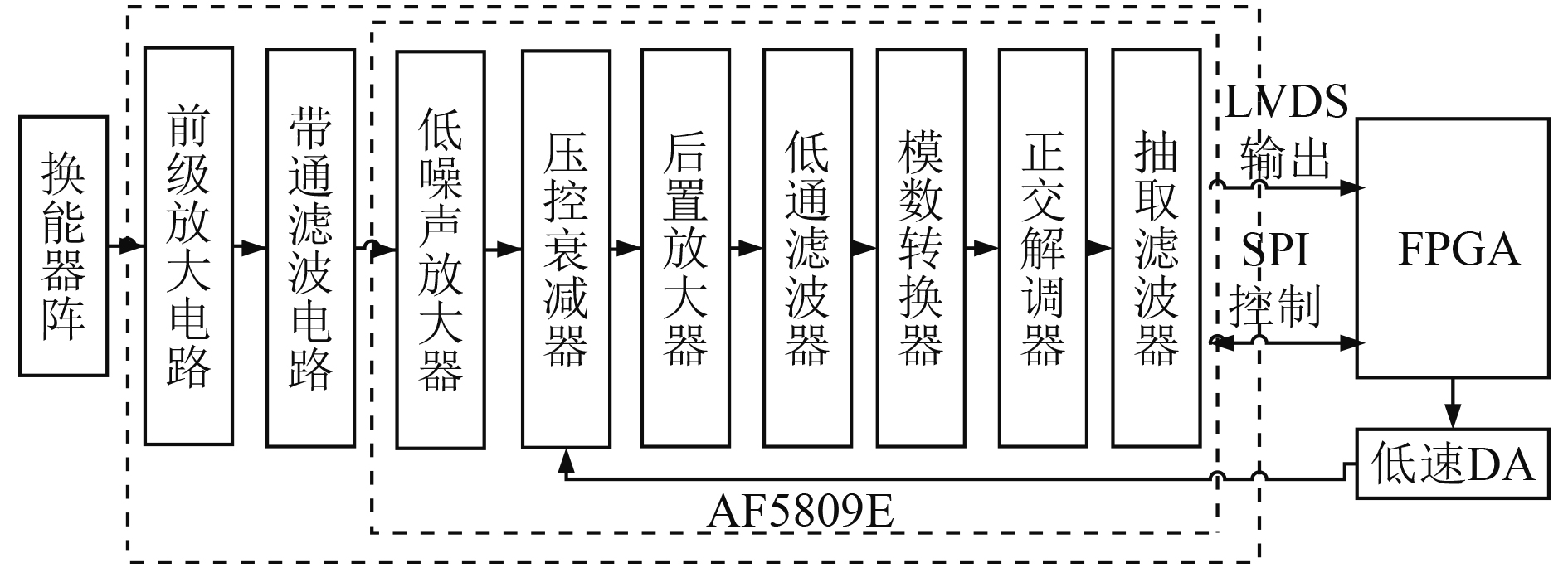

本接收机工作中心频率625 kHz,带宽200 kHz,总增益100 dB,等效输入噪声小于2μV,总动态范围超过50 dB,以满足近程回波与运程回波信号强度的差异。集成模拟前端AFE5809包含8通道低噪声放大器、压控衰减器、程控增益放大器、低通滤波器、模数转换器、数字正交解调器等功能,其模拟链路最大增益54 dB。为了满足接收机设计要求,在AFE电路前增加放大电路、带通滤波电路。其单通道电路系统逻辑结构如图1所示。

|

图 1 接收机电路系统逻辑图 Fig. 1 Logic diagram of receiver circuit system |

本接收机其主要特点如下:

1)接收机电路基于AFE5809(15 mm×9 mm)设计,外围电路器件少,电路印制板尺寸减小。

2)低功耗,单板功耗684 mW。

3)回波信号被AD采样后,在数字域进行正交解调,保证相位严格正交。

2 接收机电路设计在AFE5809集成模拟前端电路前增加前级放大和带通滤波电路,前级放大电路完成对回波信号的预放大,要求宽带、低噪声、大动态。带通滤波电路的作用是对回波信号进行选频,使通带内的信号无损耗通过,而滤除通带之外的噪声和干扰信号,提高信噪比,还可以防止干扰信号进入混频电路时造成镜像干扰,解调出近基频的频率成分和有效信号混叠而无法分辨。

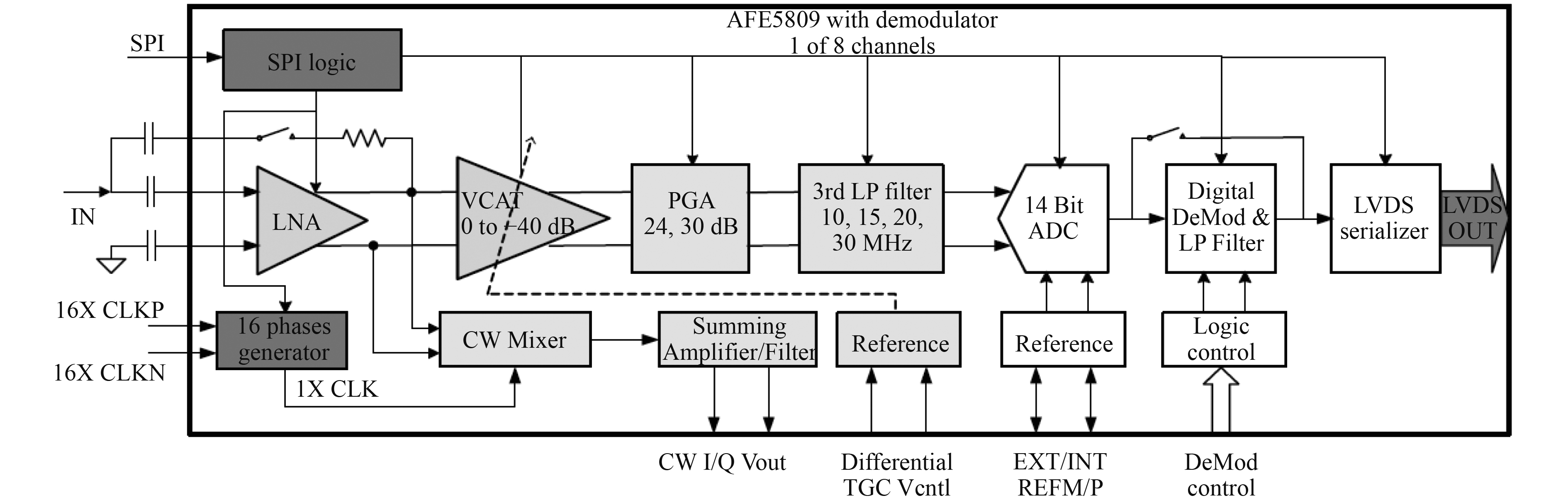

2.1 AFE5809内部功能模块介绍集成模拟前端电路是接收机电路的核心,既具有模拟信号调理功能,又具有模数转换、数字正交解调、低通抽取滤波等数字信号处理功能,从带通滤波级输入的模拟回波信号通过AFE5809之后已经是完成数字正交解调的信号,信号以低电压差分信号(LVDS)形式传输到数字信号处理板进行频移解算。AFE5809内部结构如图2所示。

|

图 2 AFE5809内部结构图 Fig. 2 AFE5809 internal structure diagram |

从AFE5809内部结构图可以看出,每个通道都是由低噪声放大器(LNA)、压控衰减器(VCAT)、(程控增益放大器)PGA、低通滤波器(LPF)、模数转换器(ADC)、正交(I/Q)解调器、低通抽取滤波器、波束成型器(CWD)等模块构成。

低噪声放大器(LNA)具有优异的低噪声性能,通过程序控制可选择24dB,18dB,12 dB三种增益,相对应等效输入参考噪声为0.63,0.7,0.9 nV/Hz,输入最大线性信号幅值1 Vpp,其低噪声和高输入范围相结合,实现了宽输入动态范围,有利于提高测速声呐系统作用距离。

压控衰减器(VCAT)完成对不同信号电平信号的时变增益控制,主要作用是抑制较强的近程信号。其动态范围40 dB,随控制电压VCNTL(VCNTLP与VCNTLM引脚上的电压差)在−40~ 0 dB之间线性变化。VCNTL采用差分电压控制方式,可减小共模噪声,控制电压变化范围0~1.5 V。

在压控衰减器之后,跟随一级程控增益放大器(PGA),通过程序控制24 dB,30 dB可选。PGA由差分电压-电流转换器、钳位电路、直流偏置校正电路、可编程的低通滤波器构成。钳位电路可以提高集成模拟前端的过载恢复性能,抗混叠滤波器用跨阻式运算放大器设计3阶巴特沃斯有源低通滤波器,−1 dB截止频率通过程序5 MHz,10 MHz,15 MHz,20 MHz,30 MHz可选,8个通道的低通滤波器带宽同时被设置。

模数转换器完成模拟信号到数字信号的转变,AFE5809内部ADC模块使用流水线结构,八通道ADC拥有共有的时钟输入,每个通道的采样时钟是由输入时钟通过时钟缓冲器产生。采样精度通过程序配置可选择12/14 bit,采样率在10 MHz~65 MSPS之间,模数转换后的信号以LVDS信号标准输出。

在模数转换器之后,AFE5809 还集成了数字正交 (I/Q) 解调器和低通抽取滤波器。解调模块的主要用途是产生两路相互正交的本振信号对回波信号进行数字正交解调,然后通过低通抽取滤波器滤除和频信号,保留差频信号,减少LVDS 数据速率,降低后级信号处理器负担。

2.2 集成模拟前端电路设计AFE5809是一款高度集成的模拟前端,单芯片集成8个通道,每通道具备调理模拟信号和数字信号功能。由于多普勒测速声呐有4路回波信号,因此只需使用AFE5809的4个通道。通过软件配置可独立关断其余4个通道,以减小功耗和外围配置阻容器件的数量,同时可以节省PCB空间。

AFE5809模拟信号电路实现对回波信号的放大和滤波功能,模拟端最大总增益54 dB,最小总增益−4 dB,抗混叠滤波器截止频率配置为5 MHz。

AFE5809数字信号电路完成对回波信号的模数转换、数字正交解调、低通抽取滤波等功能,最终将形成的LVDS信号传输给FPGA。

3 仿真结果 3.1 模拟电路仿真根据上述电路设计原理图,在TINA-TI软件中使用器件的spice模型搭建电路,对电路模拟功能进行仿真测试。

使用信号分析仪得到电路的增益-频率响应,其响应曲线如图3所示,频率为625 kHz时电路总增益100.41 dB,−3 dB带宽205.74 K,满足设计要求。

|

图 3 最大总增益—频率响应图 Fig. 3 Maximum total gain-frequency response graph |

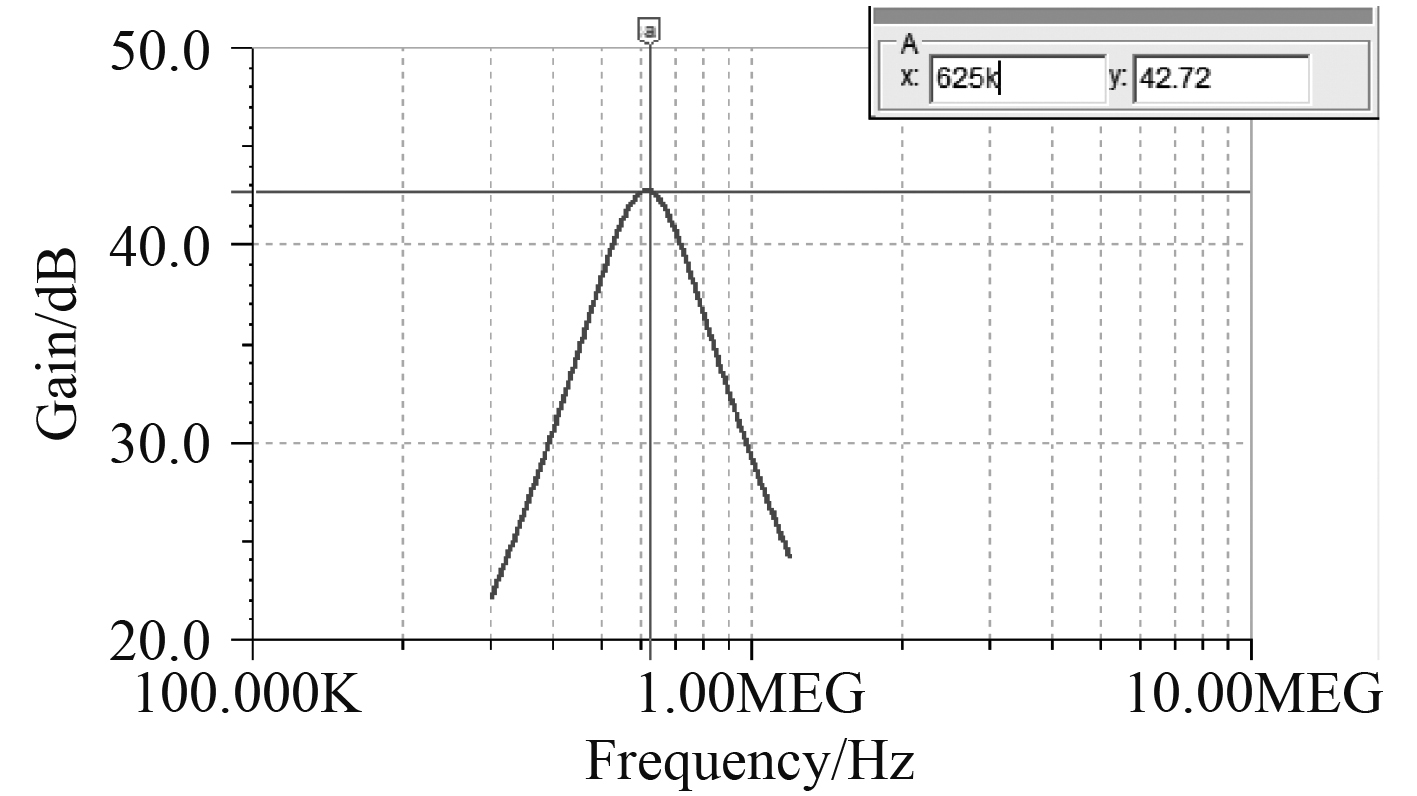

通过增益控制管脚配置AFE5809各级增益,配置LNA增益12 dB,PGA增益24 dB,压控衰减器增益−40 dB,固定增益46 dB,得到电路理论最小总增益42 dB。最小增益仿真电路曲线如图4所示,625 kHz时电路增益42.72 dB。电路最大总增益100.41 dB,因此电路模拟增益动态范围57.69 dB,满足设计要求。

|

图 4 最小总增益—频率响应图 Fig. 4 Minimum total gain-frequency response diagram |

AFE5809模拟前端集成了模数转换、数字正交解调、数字低通滤波、抽取等功能,在模拟仿真电路中无法进行数字功能测试,因此用Matlab软件模拟其数字电路功能进行测试,仿真流程框图如图5所示,表1是仿真得到的数据。

|

图 5 Matlab模拟仿真流程框图 Fig. 5 Matlab simulation flow diagram |

|

|

表 1 Matlab模拟仿真数据 Tab.1 Matlab simulation data |

由表1数据可以看出,用此方案仿真解算后得到的频移与真值之间存在0.034的偏差,经仿真验证固定频率差由抽取系数导致,抽取系数越低偏差越小。

4 实验数据分析通过电路板实物图对比可以发现,AFE接收机面积比传统接收机大幅度减小,AFE接收机尺寸80 mm×60 mm,传统接收机为圆形,直径146 mm,相比下面积减小71.3%。

在实验室环境下,用信号源和多普勒测速声呐检测设备对AFE接收机性能进行测试验证。

用信号源输出正弦波单频信号对AFE接收机的模拟性能进行测试,得到AFE接收机总增益100 dB,−3 dB带宽201 kHz,等效输入噪声0.8 dB,单板功耗684 mW。

多普勒测速声呐检测设备模拟生成具有频移的回波信号输入到AFE接收机,AFE接收机对回波信号进行模拟放大、模数转换、数字正交解调、低通抽取滤波等处理,将采集到的回波信号以LVDS形式传输到FPGA,用Matlab软件对采集到的数字信号进行频移解算,解算得到的频移值与多普勒测速声呐检测设备设定频移值进行比较,验证使用AFE接收机系统解算频移精度,实验数据如表2所示。

|

|

表 2 AFE接收机第一通道实验数据 Tab.2 Experimental data of the first channel of AFE receiver |

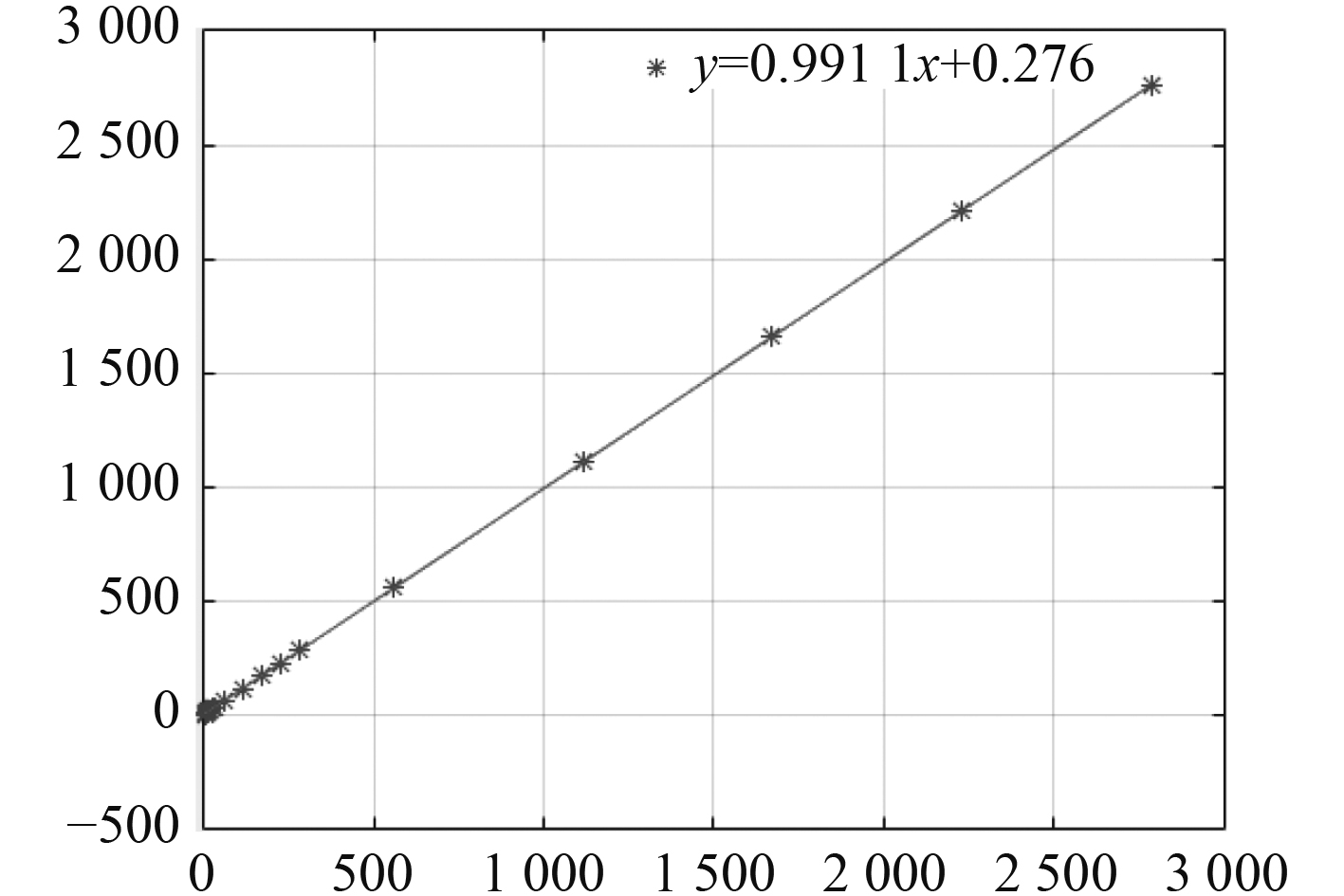

由表2可以看出:多普勒测速声呐检测设备输出回波信号的频移值范围0~2786 Hz,覆盖真实环境下的测速频移大小;AFE接收机对应解算的频移值与设定值相比存在一定的偏差,偏差值随着频移值增大而增大

由于偏差值与频移值之间的关系可以推测二者之间存在线性关系,因此对实验数据进行线性拟合,得到线性拟合公式,用该公式对实验数据进行处理后,得到线性拟合后偏差值见表2,偏差值在1 Hz左右。

|

图 6 线性拟合 Fig. 6 Linear fitting |

由表2可知,经过线性拟合之后频移仍然存在较小偏差,存在偏差的原因可能是因为系统时钟误差导致,因为检测设备系统时钟与AFE接收机采样时钟不同源。

5 结 语基于集成模拟前端AFE5809设计的多普勒测速声呐接收机,大幅度减小电路板面积,有利于多普勒测速声呐硬件系统的小型化,并且采用集成模拟前端设计的接收电路,用数字正交解调取代了传统的模拟正交解调保证了相位的严格正交。实验数据结果表明,解算出的频偏值经过拟合之后与真值之间的偏差较小,满足多普勒测速声呐系统要求。

| [1] |

冯宏, 王忠康. 通用型高频宽带ADCP信号处理系统设计与实现[J]. 声学技术. 2020, 39(1): 110-116

|

| [2] |

石靖鹏, 彭东立. OMAP平台嵌入式声学多普勒流速剖面仪系统设计与实现[J]. 声学技术, 2014, 33(3): 199-203. |

| [3] |

马修准. 基于FPGA的多普勒计程仪硬件平台设计[J]. 杭州电子科技大学学报, 2014, 34(1): 75-78. DOI:10.3969/j.issn.1001-9146.2014.01-018 |

| [4] |

张碧锋, 郭英. 数字中频正交采样及其FPGA实现[J]. 电讯技术, 2011, 51(2): 46-51. DOI:10.3969/j.issn.1001-893x.2011.02.009 |

| [5] |

薛凤杰, 吴建波, 王长红. 宽带多普勒测速声呐数字仿真系统设计[J]. 网络新媒体技术, 2016, 5(6): 43-48. DOI:10.3969/j.issn.2095-347X.2016.06.009 |

| [6] |

孙广金. 基于 ADS1299的新型电脑采集系统设计[J]. 机械与电子, 2014, 1: 75-76. DOI:10.3969/j.issn.1001-2257.2014.04.021 |

| [7] |

缪富城. 宽带相控多普勒计程仪硬件系统设计[D]. 哈尔滨: 哈尔滨工程大学, 2019.

|

| [8] |

刘宁. 基于常规阵的300kHzADCP模拟硬件系统的研究[D]. 哈尔滨: 哈尔滨工程大学, 2019.

|

| [9] |

王雪良. 多波束成像声呐集成模拟前端与数据采集系统设计[D]. 哈尔滨: 哈尔滨工程大学, 2013.

|

| [10] |

刘德铸. 声学多普勒流速测量关键技术研究[D]. 哈尔滨: 哈尔滨工程大学, 2010.

|

| [11] |

赵宇玲. 基于FPGA的信号采集与处理系统设计与实现[D]. 南京: 南京理工大学, 2008.

|

| [12] |

张金勇. 基于生物医学信号采集的多通道模拟前端集成电路设计[D]. 广州: 华南理工大学, 2010.

|

| [13] |

TexasInstruments. SLOS738E Datasheet[DB]. www. ti. com. cn, 2015.

|

2022, Vol. 44

2022, Vol. 44