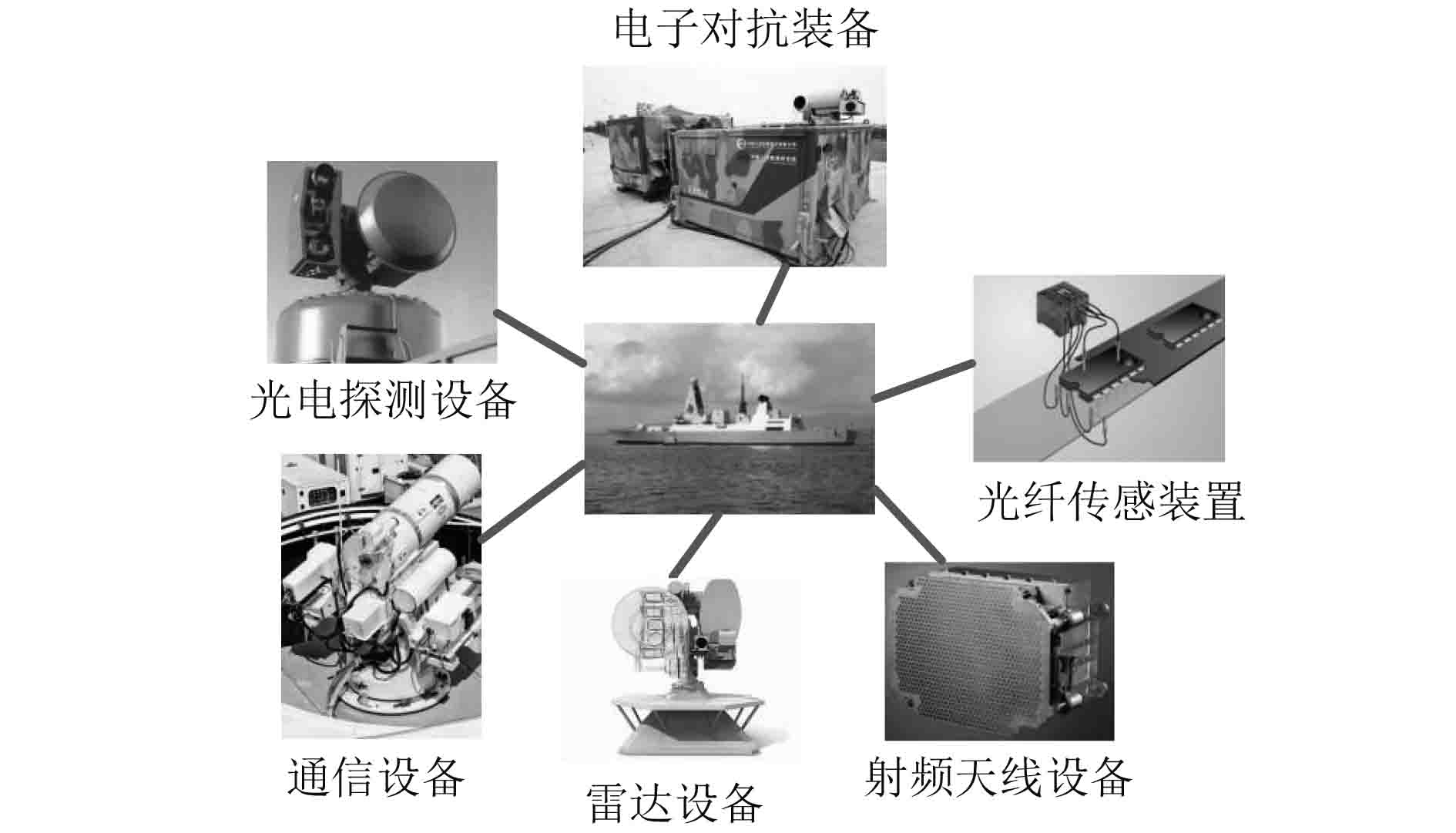

随着现代化舰船作战体系对于大数据获取和数据分析的要求日益强烈,新一代舰船装备对复杂海情和通信信息的处理需求不断增长。这些先进的电子装备包括:光电探测、电子对抗、光纤传感[1]、射频天线[2]、雷达、通信[3]等,如图1所示。为了适应复杂信息的处理需求,舰船装备上的电子系统规模越来越复杂,而且设备升级换代速度也越来越快。

|

图 1 现代化舰船上进行数据处理的电子设备 Fig. 1 Electronic systems for data processing on the modern ships |

为了快速、高效地实现这些复杂的电子系统,在数字电路和系统中越来越多地采用了软硬件协同设计方法。它是指对系统中的软硬件部分使用统一的描述和工具进行集成开发,可完成全系统的设计验证并跨越软硬件界面进行系统优化。核心思想是从软件平台的算法到硬件代码的实现形成统一的映射描述方式。采用软硬件协同设计的方法,进行数字电路的设计,可以有效地提高设计效率。

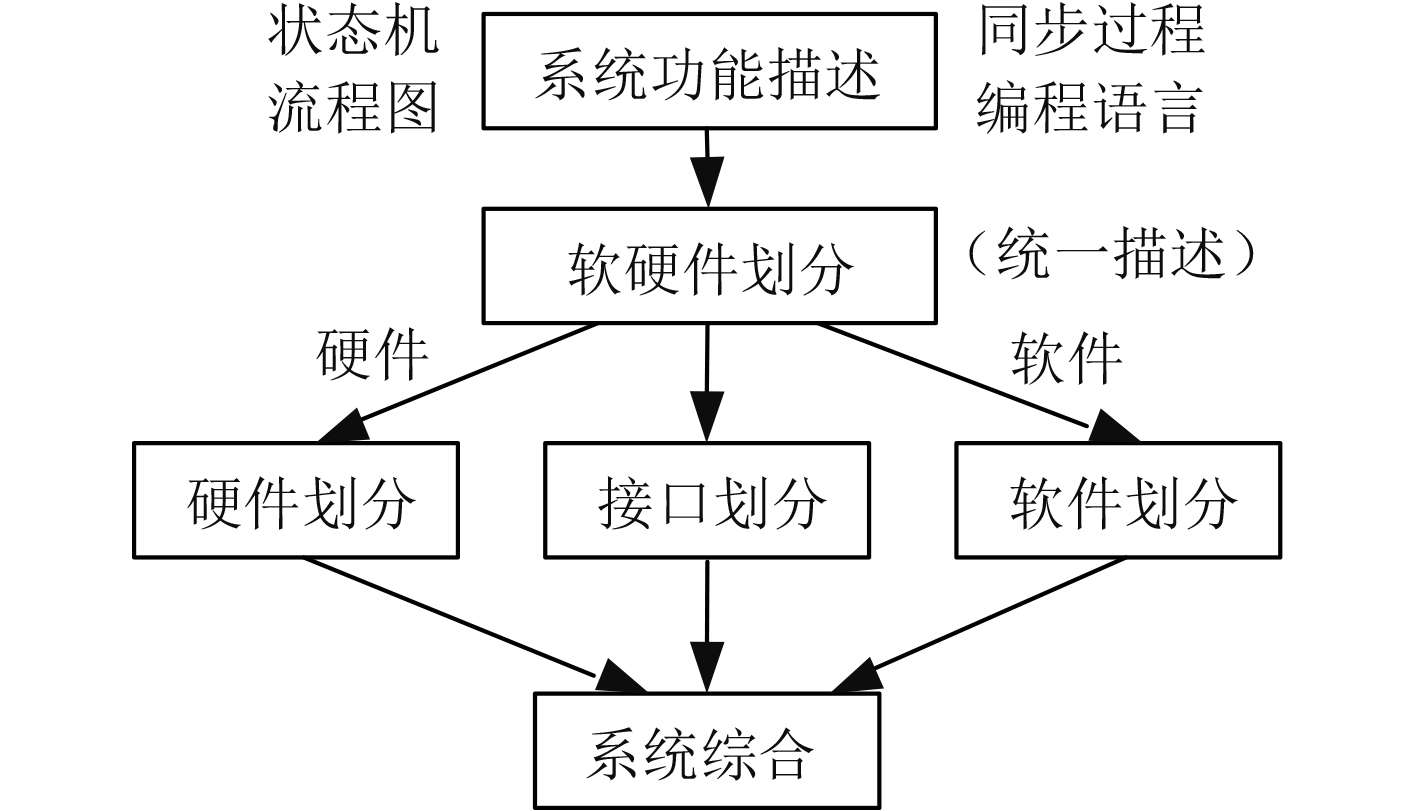

软硬件协同设计所涉及到的内容有软硬件协同设计流程、软硬件划分、软硬件并行综合、软硬件并行仿真,如图2所示。它的设计基本方法是:

1)用C语言等(高层次设计语言)进行系统描述,并进行模拟仿真和系统功能验证;

2)对软硬件实现进行功能划分,分别用语言进行设计并将其综合起来进行功能验证和性能预测等仿真确认(联调模拟仿真);

3)如无问题则进行软件和硬件详细设计和修改;

4)最后进行系统测试验证。

|

图 2 典型的软硬件协同设计流程图[3] Fig. 2 Typical design flow of software and hardware co-design |

但是,在传统数字电路的软硬件协同设计流程中,硬件部分的设计往往耗时又费力,通常是在有了软件代码(如C代码)之后,还需要通过人工的方式转换成硬件代码。随着数字电路设计对快速实现硬件化需求的不断增长、面世时间不断缩短,数字电路工程师们的设计压力越来越大。

为了有效解决这一问题,本文采用了一种高效的、基于自动化综合工具的数字电路快速设计方法。采用该方法,能够在实现正确、快速综合的同时,保证综合后模块的速度快、面积小。文中首先给出该快速设计方法的基本流程,其次介绍基于该方法进行快速设计的2个舰船上常用的频域数据处理和图像传输设计实例——快速傅里叶变换和图片压缩编码模块,最后对论文进行小结。

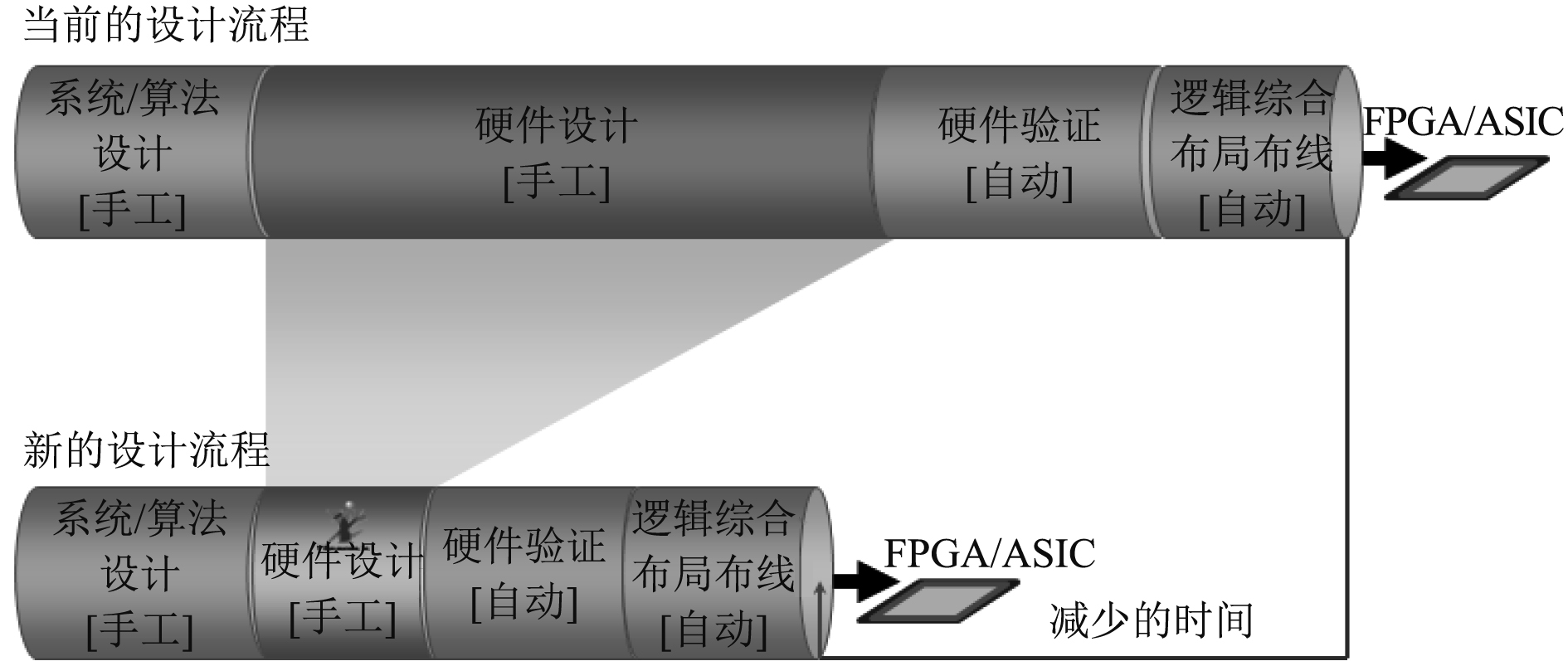

1 快速设计方法的基本流程目前,在系统算法设计到硬件设计的转换中,很多算法是以C语言的形式存在,转换过程主要还是以手工翻译为主,算法的改变会使得硬件设计的修改费时、费力。为此,采用一种实用的自动化综合工具eXCite,进行从C代码向HDL语言的自动转换,执行效率很高,大大缩短系统设计的周期,如图3所示。自动化综合工具eXCite是由Y.Explorations.Inc开发的一款将C代码转化为RTL级硬件代码的综合工具[4]。引入自动化综合工具eXCite进行部分软件代码的硬件化,实现C代码的高层次修改和硬件综合过程。基本过程包括:选定需要加速的模块、筛选需要加速的函数、自动化综合(即C2RTL转换)和现场可编程门阵列(FPGA)加速等几个部分。

|

图 3 使用eXCite协同设计可以缩短系统设计的周期[4] Fig. 3 Decreased system design period by using eXCite for co-design |

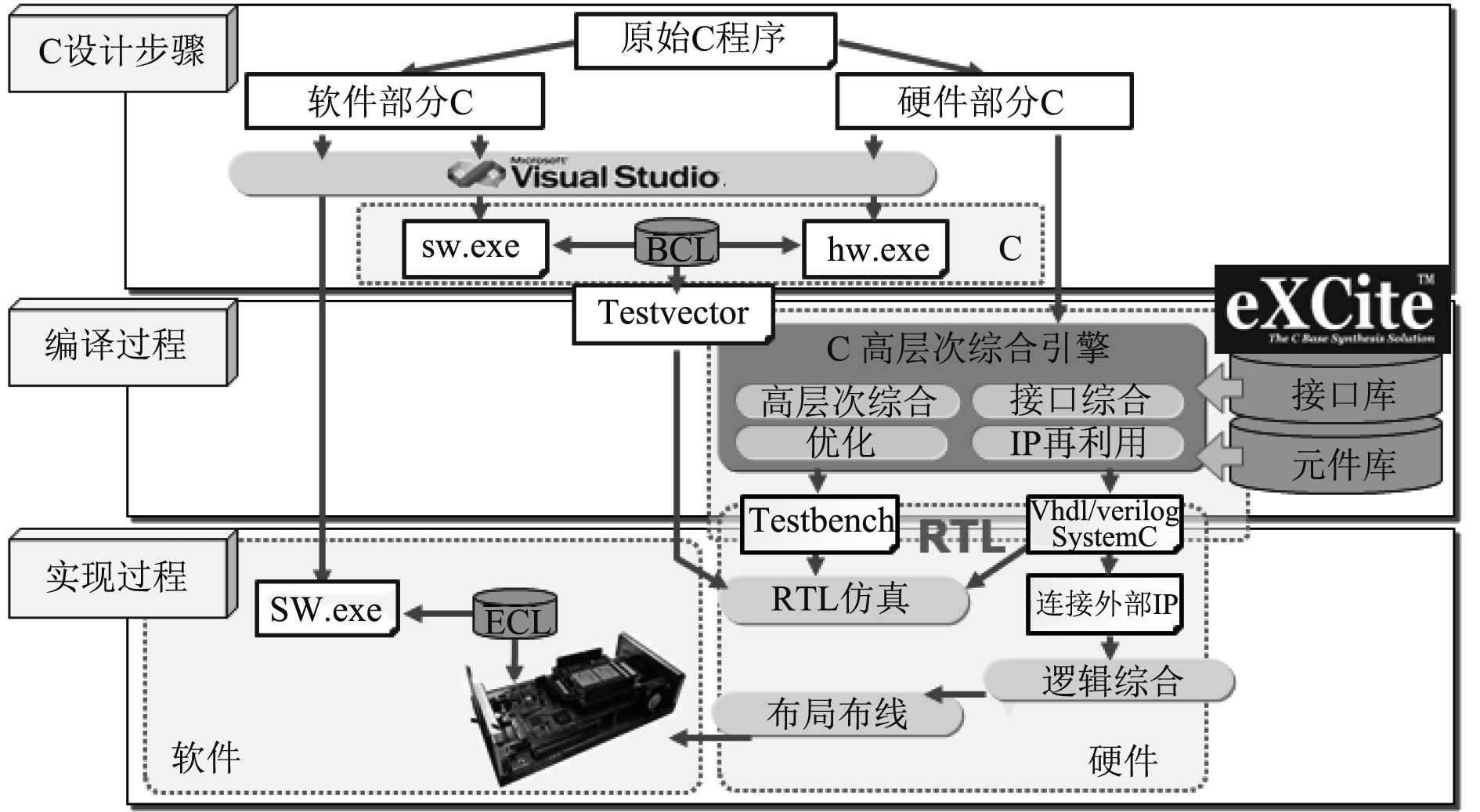

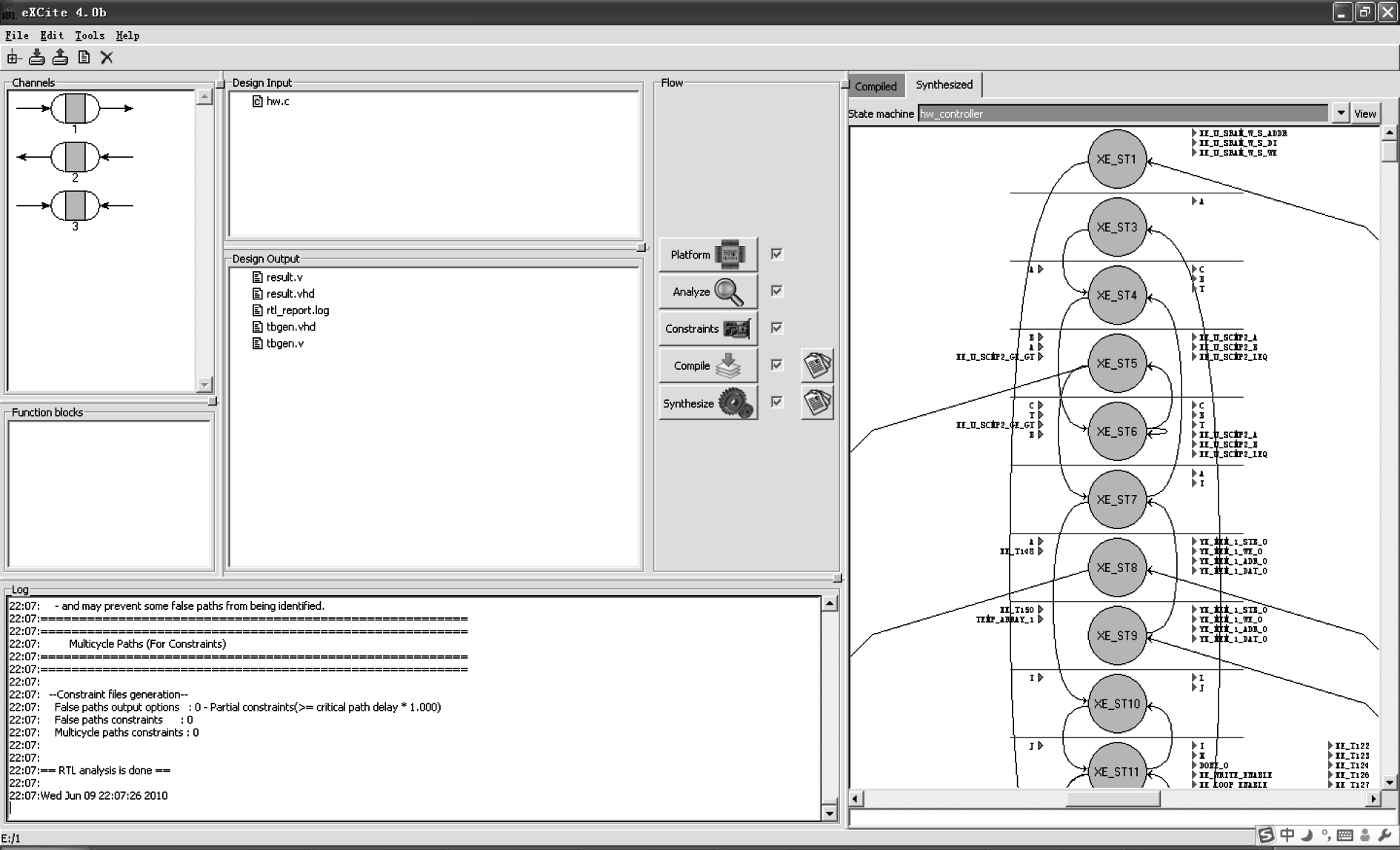

自动化综合工具eXCite采用软硬件协同设计的思想,在软件算法层面进行修改设计,并将C代码库文件及各个函数单元映射到相应的硬件单元库中,以有限状态机的形式生成HDL硬件代码,在FPGA等硬件平台上进行下载验证。实现流程如图4所示。

使用eXCite进行软硬件协同设计的优势主要包括:

1)用C/C++等高级语言进行FPGA/ASIC设计可大大使设计简化;

2)C到硬件描述语言的自动转换比手工设计快数倍;

3)要修改是在高级语言层级修改,简单容易,可使整个FPGA/ASIC设计开发周期大大缩短;

4)可充分利用大量当前存在的C算法库。

|

图 4 使用eXCite进行FPGA开发的流程图[4] Fig. 4 FPGA development flow with eXCite |

下面介绍2个舰船上常用的频域数据处理和图像传输设计实例——快速傅里叶变换(FFT)和图片压缩编码(JPEG)模块。

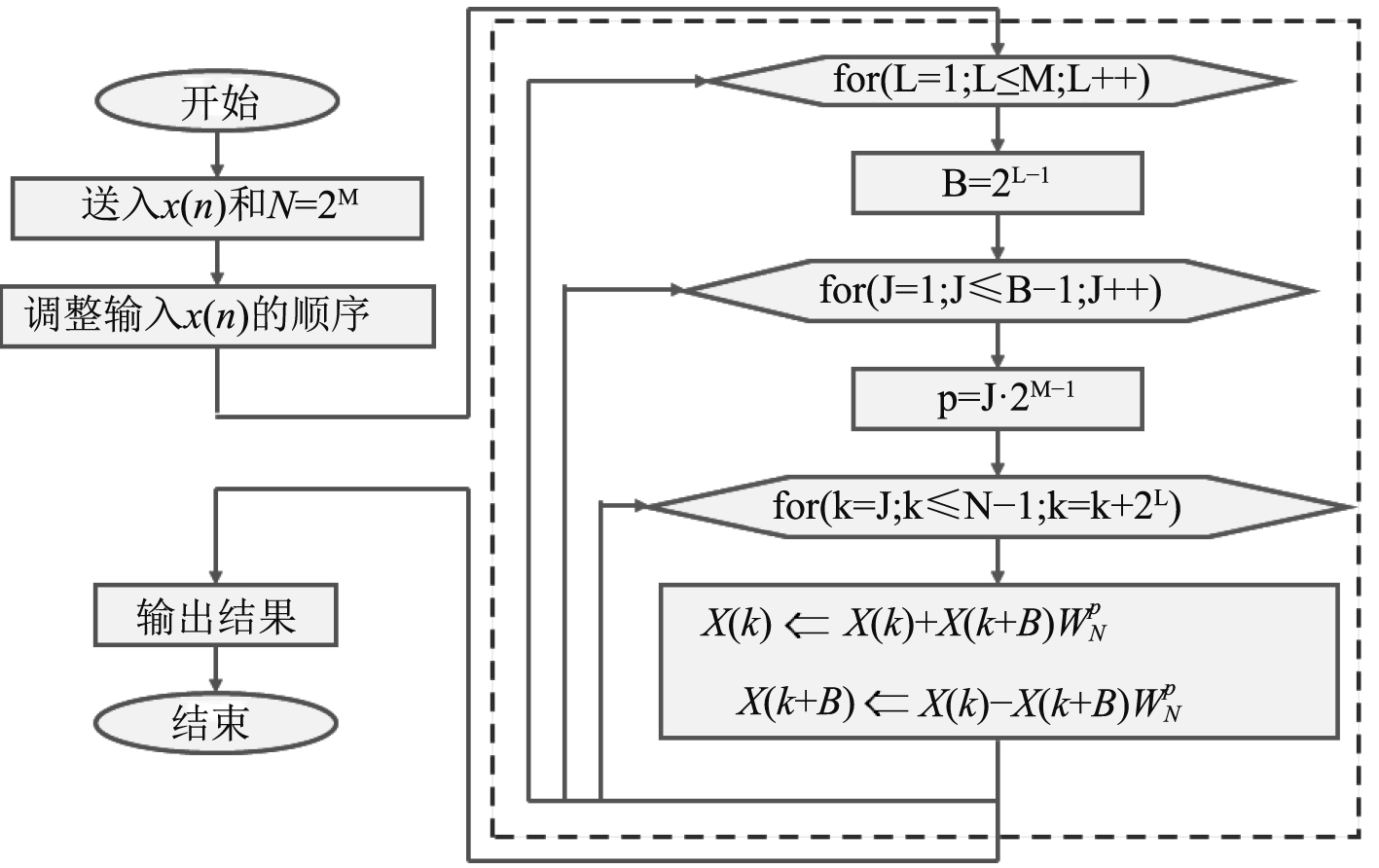

2 快速傅里叶变换模块设计快速傅里叶变换是电子设备中进行数据频域处理时最主要的步骤之一,对于舰船上振动频率、通信滤波的测量计算发挥着非常重要的作用。FFT算法有很多,本文采用基2的时间抽选算法(Coolkey-Tukey算法)。设输入序列长度为N=2M(M为正整数,将该序列按时间顺序的奇偶分解为越来越短的子序列,称为基2按时间抽取的FFT算法。也称为Coolkey-Tukey算法。其中基2表示:N=2M,M为整数。若不满足这个条件,可以人为地加上若干零值(加零补长)使其达到N=2M。该算法的流程如图5所示。

|

图 5 FFT算法的流程图[5] Fig. 5 FFT algorithm flow |

将该FFT算法中处理部分的C代码经过配置和优化,输入给eXCite工具来综合成硬件。其中:输入数据16位宽度(short int),256个(含实部和虚部)。输出数据16位宽度(short int),256个(含实部和虚部)。输入输出使用同一个MEM接口,握手信号start与done用HS接口。硬件化的界面如图6所示。

|

图 6 eXCite工具的代码硬件化界面 Fig. 6 Code hardware interface of the eXCite tool |

对128点FFT的不同输入进行多组测试,同时对比2种情况的测量结果。在相同硬件条件下,共测量5组数据,每组128个(含实部和虚部),每个数输入分别为16位,输出分别为16位。其中,第1组数均相同;第2,3,4,5组数,按照周期分别为8,16,32,64进行循环,第6组128数字均不相同。在DE2板上运行后,用示波器测量执行频率(换算成执行周期)。综合后生成RTL报告:在50 MHz的频率下,最长路径延时117 MHz,满足时序的要求,相对面积918,最长路径有2条。

将硬件化之后的代码写入硬件开发板DE2-70[7]中进行验证。其中,DE2-70开发板是Altera公司推出的一款Cyclone II系列教学开发板。同时,将FPGA硬件实现的算法运行的时间与处理器软件实现的结果进行多组对比,如表1所示。

|

|

表 1 软件和硬件FFT处理的比较 Tab.1 Comparison of FFT processing between software and hardware |

通过上面的实验可以看到,将运算较为复杂的FFT的C代码,通过自动化综合工具eXCite进行硬件化,转换为硬件描述代码,作为硬件加速器的执行频率,是处理器运行软件代码执行频率的20多倍,并且随着数据的复杂,加速比越高,加速效果非常明显,集成其他运算模块的潜力也非常大。

此外,将手工进行FFT算法硬件模块设计的时间与自动化综合工具eXCite综合所用的时间进行对比,如表2所示。可以看出,与传统手工硬件设计相比,基于自动化综合的快速设计方法可以有效减少设计时间达20倍以上。同时,综合后的相对面积与执行时间相差很小。这充分说明了该方法进行FFT模块硬件设计的有效性。

|

|

表 2 两种设计方法设计FFT模块的比较 Tab.2 Comparison of FFT module design between two methods |

图片压缩编码是电子设备上进行图像传输的关键步骤,通过压缩可以大大减少数据传递量,对于舰船上实时进行大容量的视频该图像识别、重组分析等具有重要的意义。当前,使用最广泛的图像压缩算法是JPEG。JPEG是用于灰度图与真彩图的静态图像压缩的国际标准[8],它是有损压缩的算法[9]。它的主要步骤包括:8*8分块、正向离散余弦变换(FDCT)、量化、Z字形编码、使用差分脉冲编码调制对直流系数进行编码、使用行程长度编码(RLE)对交流系数(AC)进行编码[10]。

基于JPEG压缩编码算法中的处理部分用C代码进行实现。考虑到验证数据量的大小,将这部分代码(处理的像素为256*256)加入eXCite软件中。其中:输入数据16位宽度(short int),65 535个(含实部和虚部);输出有用数据8位宽度(short int),4 979个(与图片本身有关);无用数据在jpg图片中用“0”补充完整;输入使用MEM1接口,输入使用MEM2接口,握手信号start与done用HS接口。用eXCite软件进行硬件化综合后生成result.v文件。综合后生成RTL报告:在28 MHz的频率下,最长路径延时47 MHz,满足时序的要求,面积3 798,最长路径有1条。

本文将硬件化之后的代码写入硬件开发板DE2-70中进行验证,多组图片的硬件压缩比参见表3。

|

|

表 3 多组图片的压缩比 Tab.3 Compression ratio of several pictures |

从表中可以看到,采用基于自动化综合的快速设计方法得到的硬件化JPEG模块平均压缩比超过10倍,说明该硬件化的JPEG模块具有良好的压缩性能。对于同第一组图片,将手工进行FFT算法硬件模块设计的时间与自动化综合工具eXCite综合所用的时间进行对比,如表4所示。可以看出,与传统手工硬件设计相比,基于自动化综合的快速设计方法可以有效减少设计时间达25倍以上。同时,综合后的相对面积与图片压缩比相差很小。这充分说明了该方法进行JPEG模块硬件设计的有效性。

|

|

表 4 两种设计方法设计JPEG模块的比较 Tab.4 Comparison of JPEG module design between two methods |

本文根据新一代舰船装备上电子系统对复杂海情和通信信息的处理需求,提出了一种高效的、基于自动化综合工具的快速协同设计方法,并基于方法设计实现了2个舰船上常用的频域数据处理和图像传输设计实例——快速傅里叶变换和图片压缩编码硬件模块。实验证明,采用该方法设计的硬件模块能够实现相应的功能,同时有效地缩短设计时间,提高设计效率。

在未来的工作中,还会进一步对带有选择和反馈等更复杂功能模块进行硬件化处理,并对其性能进行深入的优化和评估,让自动化综合工具能够在实际的舰船装备上电子系统设计中发挥出更大的作用,并在舰船的相关电子设备上进行更为精确的实验测试。

| [1] | MAINWARING A, CULLER D, POLASTRE J, et al. Wireless sensor networks for habitat monitoring[J]. Wireless Sensor Networks and Applications, 2002(2): 88–97. |

| [2] | HEMPSTEAD M, TRIPATHI N, MAURO P, et al. An ultra low power system architecture for sensor network applications.[J] ACM SIGARCH Computer Architecture News, 2005(33–2): 208–219. |

| [3] | SHEETS M, BURGHARDT F, KARALAR T, et al. A Power-managed protocol processor for wireless sensor networks[J]. Proc. IEEE Symp. VLSI Circuits, 2006(4): 262–263. |

| [4] | ZHANG Pei. eXCite: From C-code to RTL-code. Y Explorations Inc [R]. 2009. |

| [5] | Qureshi, Fahad, Analysis of twiddle factor memory complexity of radix-2.i pipelined FFTs[C]. Conference Record - Asilomar Conference on Signals, Systems and Computers. 2009:217–220. |

| [6] | HUSSAIN W, GARZIA F, NURMI J. Evaluation of Padix-2 and Radix-4 FFT processing on a reconfigurable platform [C]. 13th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, 2010: 249–254. |

| [7] | Altera DE2–70 Development and Education Board User Manual [M]. 2007. |

| [8] | EMIR O, ALTAN M, AYDIN C. Performance comparison of JPEG, JPEG2000 & JPEG XR imagecompression standards [C]. 24th Signal Processing and Communication Application Conference, 2016: 201–204. |

| [9] | LIN Fu-zhong. JPEG compress encoding[M]. Beijing: Multi-media Technology, Tsinghua University Press, 2000. |

| [10] | YU Tao. JPEG principle of detailed case analysis and its application in embedded Linux[R]. Computer Programming Network, 2008. |

2018, Vol. 40

2018, Vol. 40