由于在通信世界不同的标准和协议的快速进化,灵活性和适应性已成为现代通信系统的最重要特征,为此,在过去的几年里,高效的硬件架构能够支持不同的标准设计和多个无线协议,已经获得了极大的关注[1]。伴随着半导体技术、模拟集成电路和信号处理技术的高速发展,模拟芯片和印制板电路制作工艺的飞速提升,近些年射频和中频滤波器,LNA和ADC各项关键参数都有大幅度优化,为进一步改善传统接收机电路的模拟前端链路提供了可靠的技术支持[2]。

随着潜艇卫星通信需求的高速发展,目前星地间通信的数据传输速率需进一步提升,使得潜艇超高频卫星通信的接收技术面临严峻挑战[3]。HDR解调接收技术广泛应用于潜艇的卫星通信、导航和测控通信网中,近些年,720 Mbps和1.2 Gbps中频的解调接收系统正在研究或实验。本文主要针对传统的HDR系统前端模拟链路的关键技术提出自己的研究结果和优化。

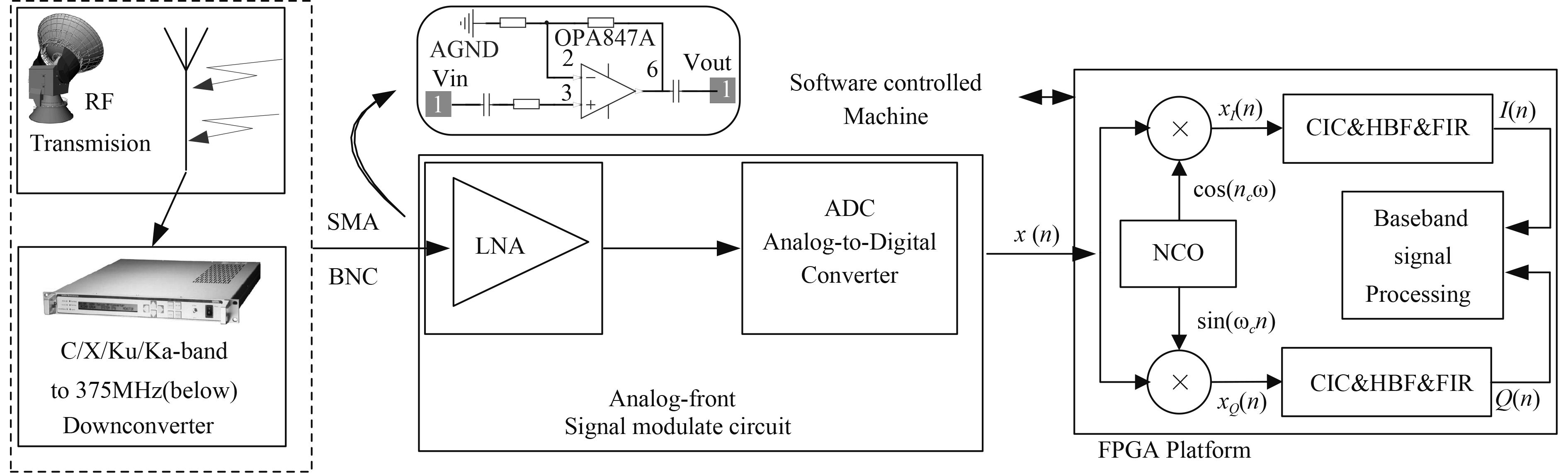

传统的解调接收系统结构框图如图1所示,该方案由3部分组成:射频下变频器、中频模拟信号调理和FPGA平台下的数字下变频器设计。射频下变频器主要功能是将C/X/Ka/Ku波段的潜用卫星信号由天线接收到的下变频器中,下变频得到期望的中频信号,这部分独立出来,组成了射频下变频器。传统的卫星通信中,下变频后的数据传输速率一般不超过375 Mbps,后端的模拟信号链路和数字信号处理也基于此传输数据率。然而,近些年更高速率的卫星通信的研究中,需要在传统的关键技术上做适合更高速率传输的研究和优化。第2部分和第3部分组成HDR解调器系统(本文的研究主要集中于这2个部分中的模拟信号链路的研究和优化),IF信号通过专用同轴线接口SMA/BNC连接入第2部分的模拟前端信号调理电路,针对不同卫星下变频器的输出IF信号,LNA单元做固定增益的调理,以单端信号或差分信号的形式送入的ADC,完成IF信号的采样。传统接收机中,ADC效果比较依赖于RF下变频器IF信号的功率和信噪比,易造成信号幅度过低,分辨率差和信号饱和失真等问题。另外,由固定增益放大器和ADC构成的模拟信号链路也存在信号带宽较窄,抗干扰能力差等缺点。第3部分:采样后的信号进入基于可编程逻辑阵列 (FPGA)平台的DDC处理模块中。传统的DDC系统由本地振荡器(NCO)、混频器、滤波器和半带滤波器(FIR&HBF)以及抽取器(CIC)组成,其主要作用:把中频信号变为零中频信号,同时降低采样率,从频谱上看,数字下变频将ADC采样后信号从中频变换到基带。这样的处理由两步完成:首先是将输入信号与正交载波相乘,然后进行数字滤波滤除不需要的频率分量。NCO、混频器、数字滤波器速率要等于采样率,采样率低于600 MHz,很难实时的在FPGA中进行处理[4]。

|

图 1 传统解调接收系统 Fig. 1 Traditional demodulation receiving system |

|

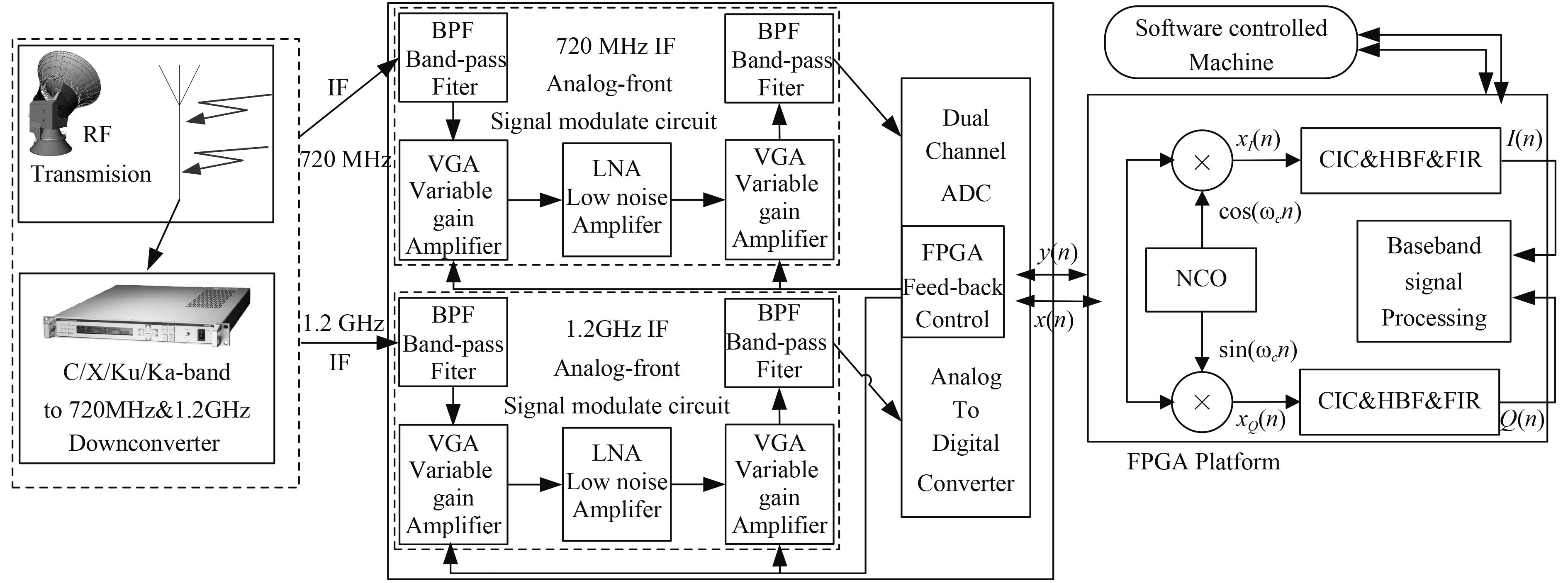

图 2 本文解调接收系统 Fig. 2 This paper's demodulation receiving system |

本文针对最近提出的720 Mbps和1.2 Gbps中频的卫星解调接收系统提出一种模拟信号链路关键技术的优化方案。图2为本文解调接收系统的设计方案图。相对于传统接收机的3个部分比较,第1部分的前端中频信号从375 MHz提升到720 MHz和1.2 GHz,第3部分基于FPGA的处理平台同时处理2个通道

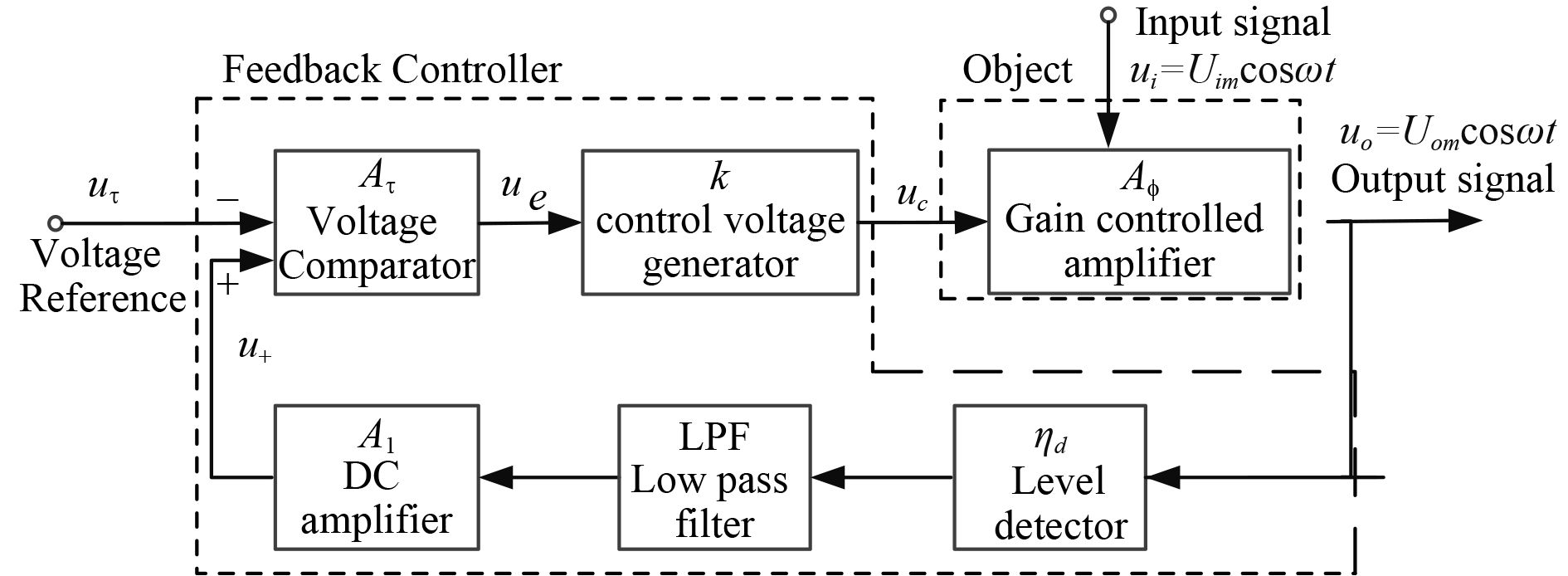

针对RF下变频器的IF输出频率为720±200 MHz或1.2 GHz±300 MHz,阻抗50 Ω,第1种方案,也是目前采用较多的方案为使用RF/IF固定增益放大器,例如ADL5542,内部集成信道阻抗匹配电路和20 dB固定增益放大电路,该方案结构简洁,幅频特性良好,从500 MHz到1.5 GHz带内波动仅不到1 dB,但该方案的缺陷也是致命的,因为该方案不能灵活调节IF信号的幅度,容易造成IF信号幅度过低、分辨率差和信号饱和失真等问题,对后级的ADC采样和FPGA处理产生不可恢复的影响。第2种方案,可以使用分立式的AGC模块,能根据输入信号电压的大小,自动调整模块的增益,使得模块的输出电压保持在ADC的最佳输入功率范围内。其机构框图如图3所示:核心模块为电压信号调节的可控增益放大器,该电压信号由电平检测器(峰值检波电路)、低通滤波器、直流放大器、电压比较器和控制电压产生器组成的环路自动生成。

|

图 3 分立式AGC结构框图 Fig. 3 Structure diagram of discrete AGC |

分立式AGC输入信号为

针对前2种方案的优缺点,本文提出一种新的模拟信道调理方案,如图2中模拟信号链路的设计所示,该方案结构复杂度具有类似于方案1的优势,优化了方案2的幅频特性抖动和不同增益下一致性差的问题,同时实现了自动增益控制,较好地解决了方案1中因IF信号幅度不可灵活控制造成的一系列影响。此外,该方案具有增益动态范围广、调理响应速度快、功耗低、噪声抑制效果良好的优点。

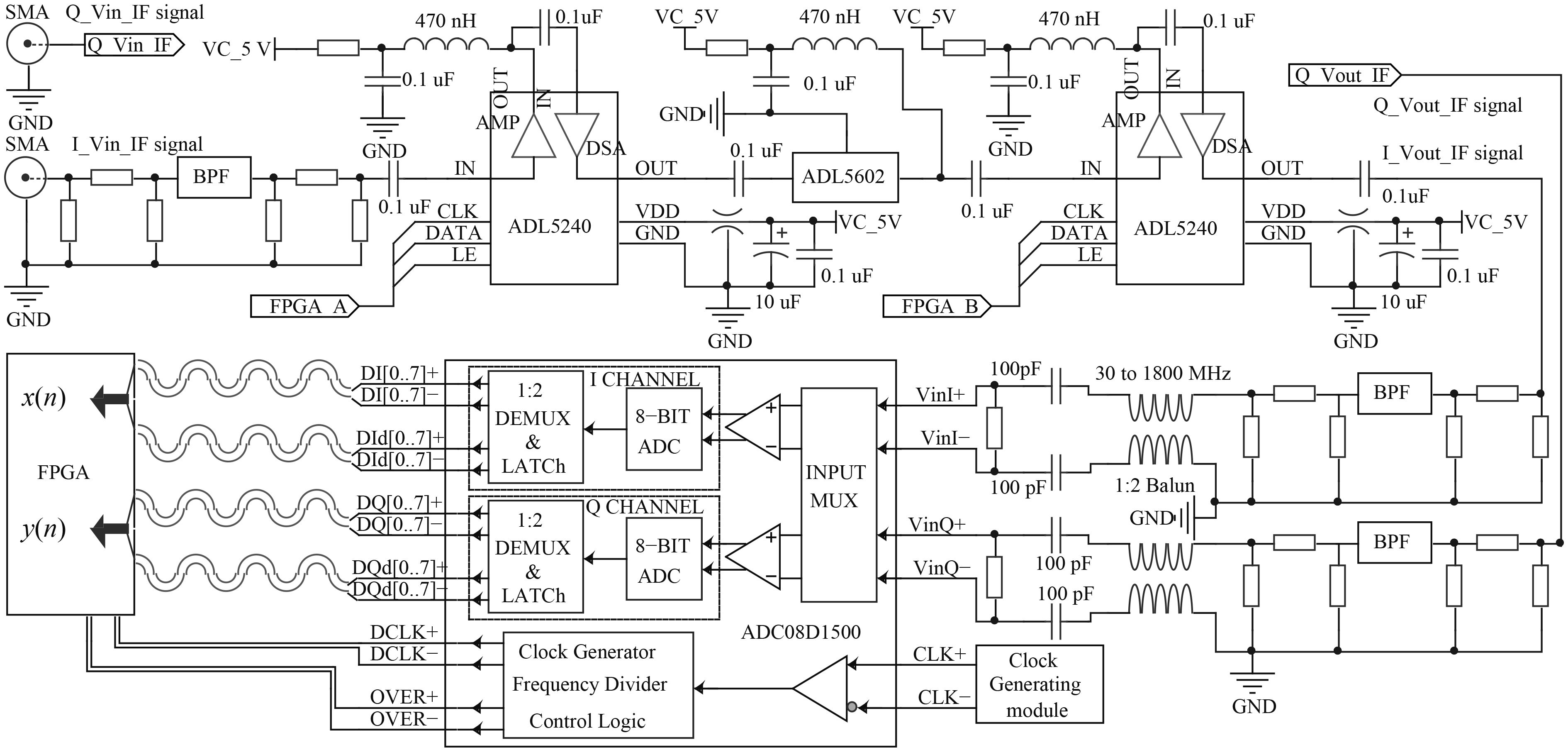

为了支持双通道卫星数据的同步解调,该方案采用2种不同中心频率和频宽的BPF,处理2个通道的IF信号,就一个通道来讲,IF信号进入HDR解调系统时,先经过一级BPF滤除低频分量和高频干扰,然后到下级数字式程控可变增益放大器(VGA),其增益由FPGA信号处理端控制,实现25 dB增益调节,再进入到下级低噪声放大器(LNA)实现固定增压20 dB调理,然后再经过VGA和BPF,滤除前端模拟链路引入的高频噪声和外界干扰,最后通过单端转差分的30~1 800 MHz的RF变压器,以差分信号的形式进入到双通道8-bit ADC端,该ADC支持双通道同时采样,因为其内部有采样保持单元,其最高速度可以达到1.7 Gbps,在选择单通道采样的情况下最高可以达到3.4 Gbps。采样后的数字信号在ADC内部做了1:2的降速并以32对差分LVDS信号对的电平模式送给FPGA端。考虑到这32对LVDS信号最高传输速率仍然会在1.5 Gbps左右,为了保持信号同步和较低的串扰,在PCB布板时以差分的蛇形等长线进入到FPGA处理平台,并针对其传输线设计100 Ω的特征阻抗,与FPGA的差分Bank接收端更好地匹配。该方案的示意电路图如图4所示。

|

图 4 本文提出的一种新的模拟信道调理方案图 Fig. 4 New scheme diagram of analog channel conditioning in this paper |

|

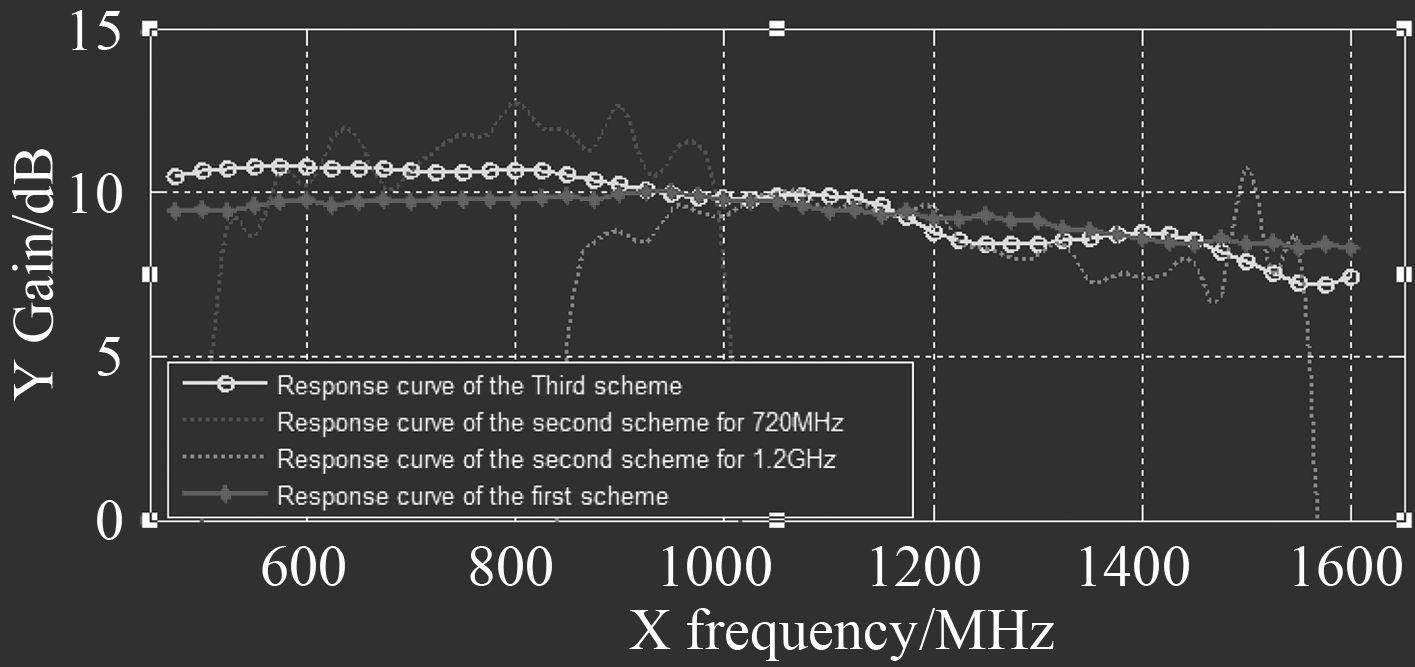

图 5 三种方案的幅频特性曲线对比图 Fig. 5 The amplitude-frequency characteristics of these three schemes |

|

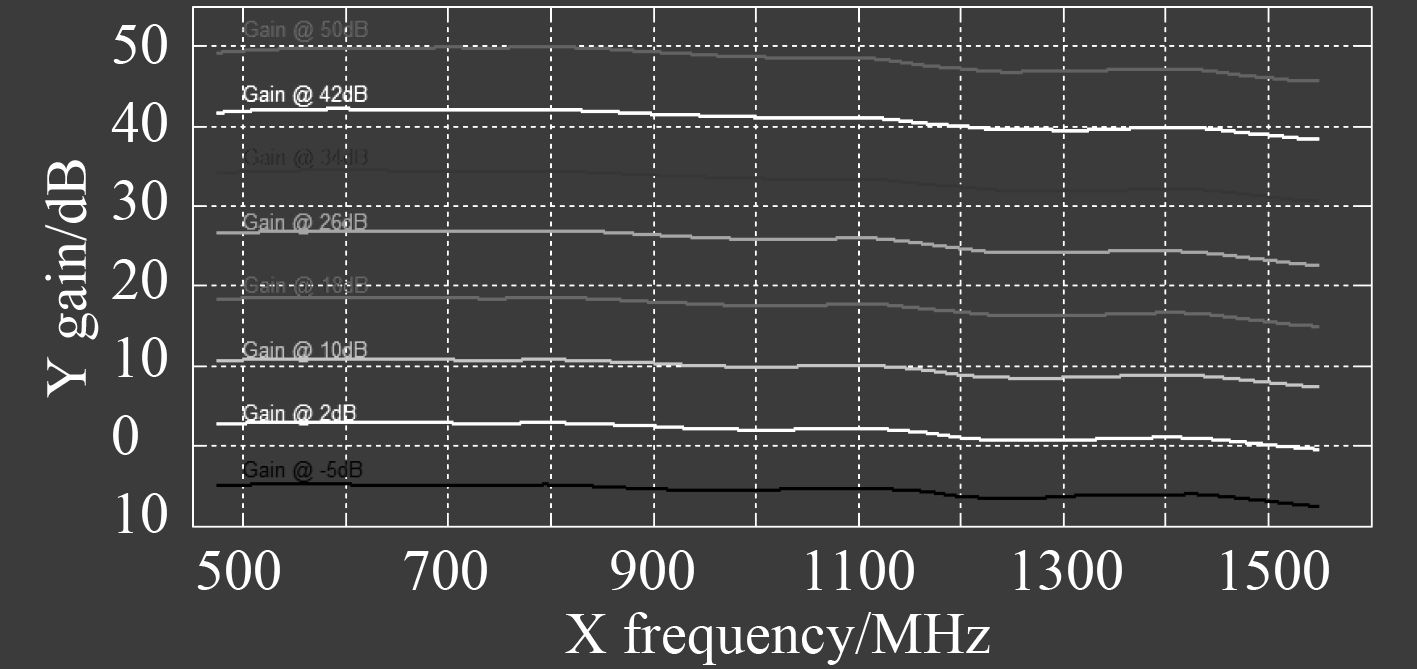

图 6 方案3下不同增益下的幅频特性曲线图 Fig. 6 Amplitude-frequency characteristic curves under different gain in the third scheme |

通过对3种模拟信号链路的PCB电路板的实际测试和数据分析得出模拟信号链路的关键指标,图5给出了3种方案的幅频特性响应曲线的对比图,保持输入信号为–10 dBm,频率从500 MHz~1.6 GHz扫频,得出3种方案的增益值,并在Matlab中做仿真对比。可以明显看出,方案1的曲线在带内平坦度最好,只有1.7 dB;其次,方案3的带内平台度也比较良好,特别是所考虑720±200 MHz或1.2 GHz±300 MHz的带宽范围内,其波动均小于0.73 dB或2.07 dB;方案2的带内波动最大,而且波动规律比较杂乱,在720±200 MHz或1.2 GHz±300 MHz的带宽范围内,其波动为4.1 dB或3.9 dB。从频谱响应上说,方案3克服了方案1幅度不可自动调节的缺陷,同时优化了方案2中存在的不可容忍的带内抖动,是最适合HDR解调系统的模拟信号链路。

对于HDR解调系统来讲,不同增益下的响应曲线的一致性也极为关键,图6给出了方案3在不同增益情况下的幅频特性响应曲线,设置不同功率的输入信号,从–5 dB~50 dB设置模拟前端的增益,频率从500 MHz~1.6 GHz扫频,并将获取到的数据在Matlab上仿真,可以明显看出该方案各个增益值下能够保持良好的一致性,并得出结论,实测动态范围最大可以达到55 dB,各个增益下响应一致性好。

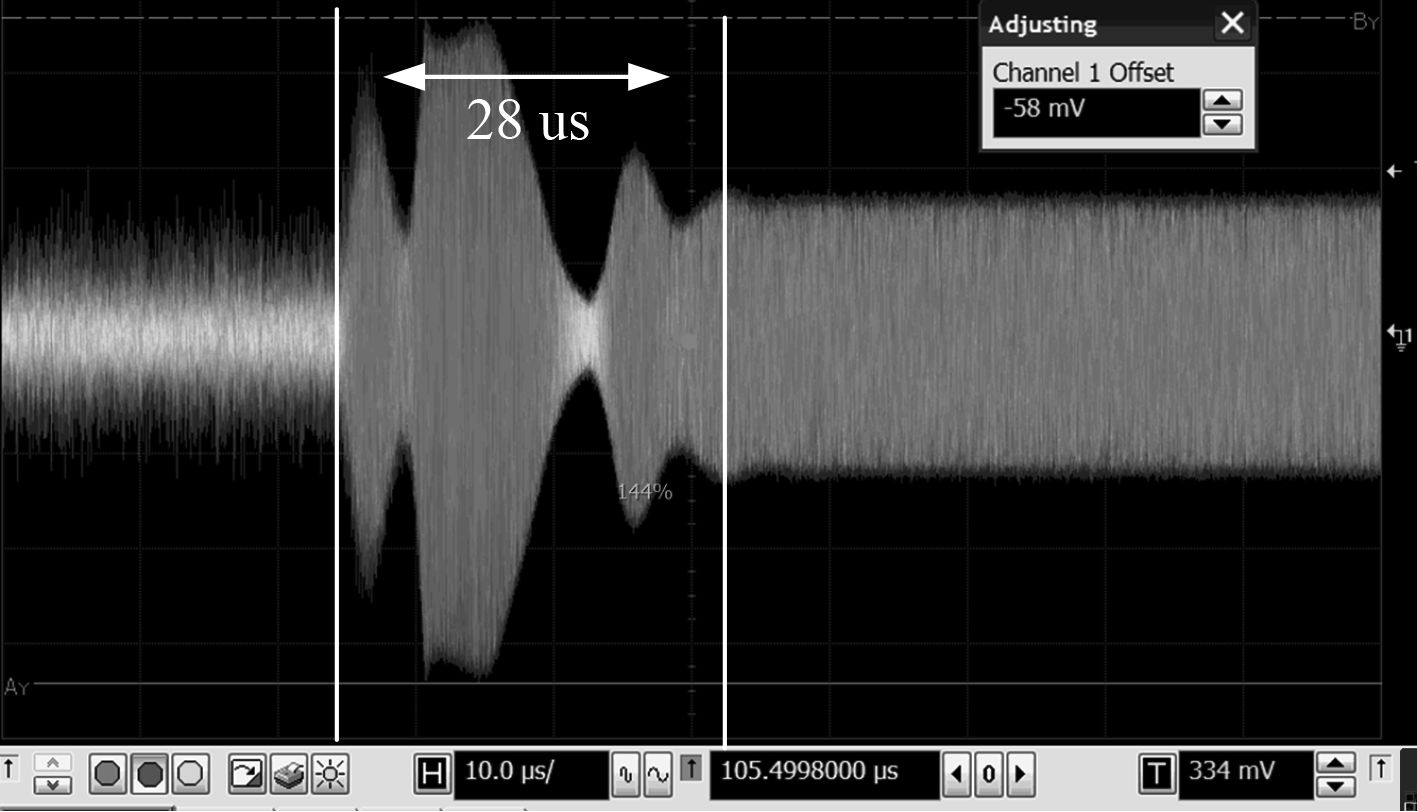

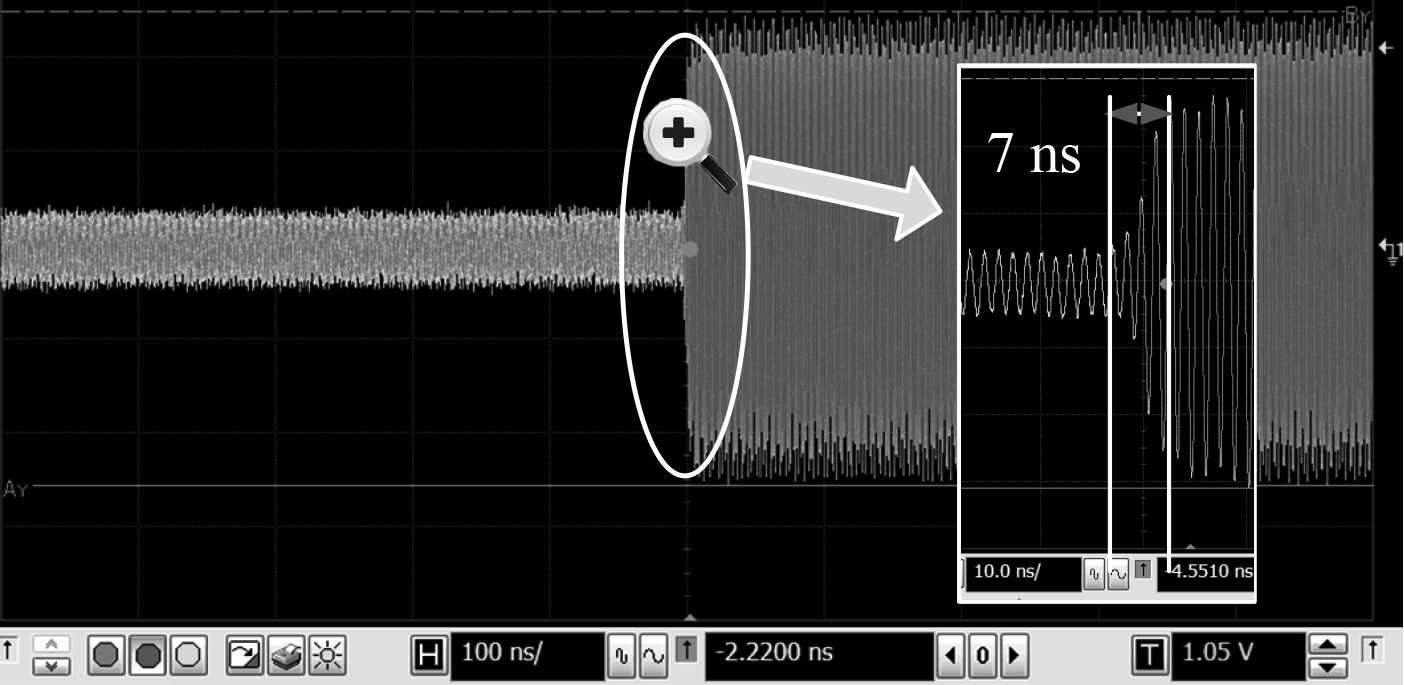

在无线通信中由于气候、环境、距离等各种因素的影响,接收到的信号幅度随机起伏变化,为了更好地调理模拟前端的信号,链路需要具有快速响应特性的AGC。图7和图8给出了方案2和方案3的响应时间对比图,两者有很大的区别。方案2响应时间长,实测28 μs,有个明显的调整信号输出的过程,该过程是方案2内部的峰值检波电路、电压比较器和控制电压产生器互相适应的必然结果。而方案3由FPGA直接给出数字信号进行增益控制,灵敏度高,响应时间仅为7 ns,相比方案2更具优势。

|

图 7 方案2 AGC响应时间测试 Fig. 7 Respond time of AGC in the second scheme |

|

图 8 方案2 AGC响应时间测试 Fig. 8 Respond time of AGC in the third scheme |

|

图 9 使用90°布线和R布线不同阻抗的TDR仿真 Fig. 9 TDR simulation of different using 90 ° and R wiring |

|

图 10 方案 2 和方案 3 的实物图 Fig. 10 Physical pictures of the two schemes |

模拟信号链路的阻抗设计是信号完整性的关键,任何阻抗突变都会引起信号的反射和失真。微带线的特征阻抗

| ${Z_0} = \frac{{87}}{{\sqrt {{\varepsilon _r} + 1.41} }}\ln \left( {\frac{{5.98h}}{{0.8w + t}}} \right)\text{。}$ |

式中:

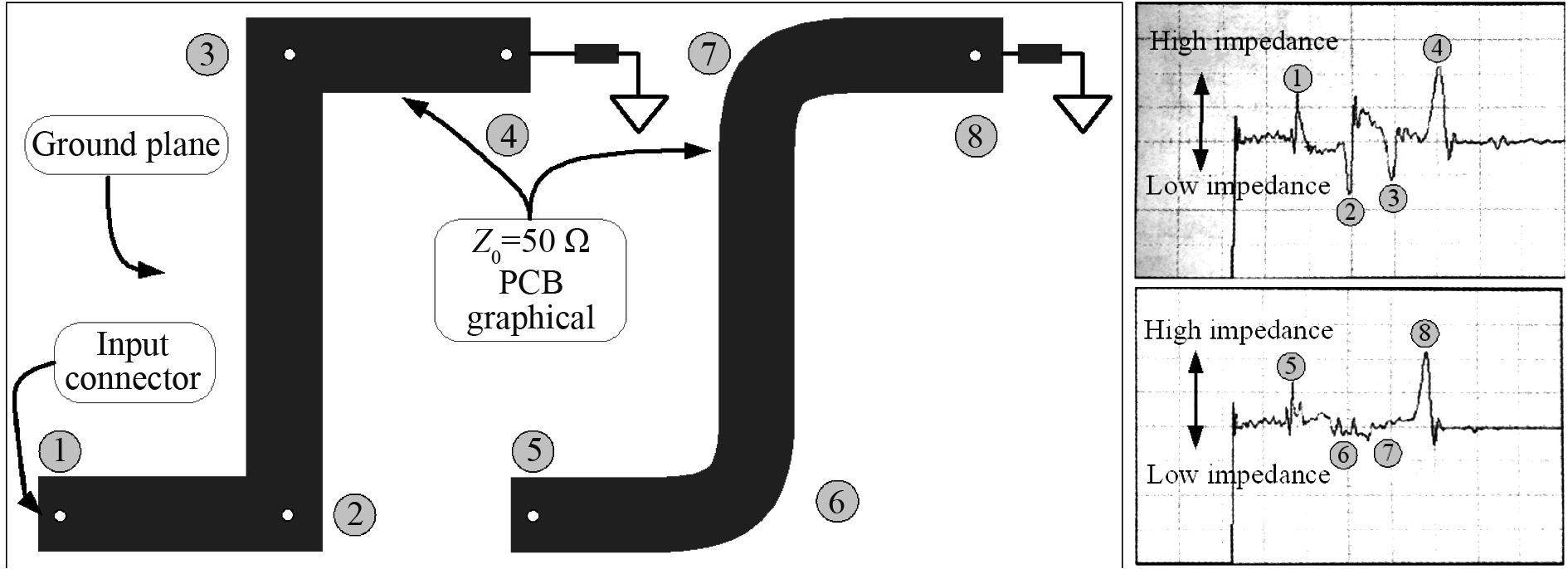

关键信号链路的PCB布线对阻抗匹配非常重要,图9为针对2种布线的TDR仿真,R布线的阻抗几乎没有什么变化。因此,在试验PCB上,模拟信号链路均采用R布线,减弱因阻抗变化而引起不确定的信号反射。

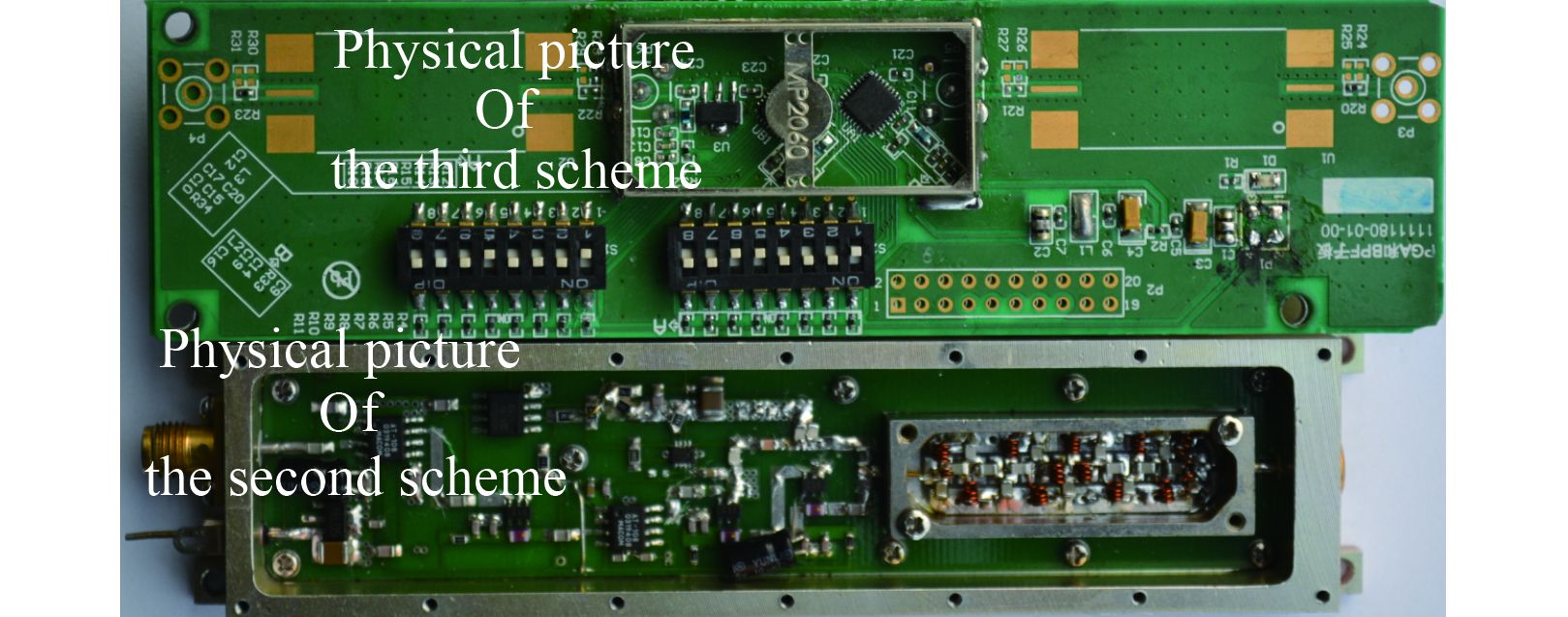

在制作试验PCB板时,着重考虑了电源回路和信号地分割对模拟链路信号的影响[6–7]。放大器和BPF构成的模拟链路的供电回路与ADC数字端供电以及FPGA其他供电回路在电路板的空间布局和电流路径彼此独立,并在电源模块端单点共地。为了取得较好的测试效果,采用蜂窝屏蔽壳和全屏蔽处理[8–9],并设计子母板的结构,尽量降低外界环境和供电电源之间的干扰,最后图10给出了试验用的2个验证模拟信号链路的PCB,分别是本文所描述的方案2(下半部分)和方案3(上半部分)的实物图。

4 结 语本文提出并实现了一种高动态范围,快响应速度,噪声抑制效果好的模拟信号链路优化方案。通过陶瓷带通滤波器(BPF)模块,数字式程控可变增益放大器(digital control variable gain amplifier,VGA),低噪声放大器(LNA),RF/IF固定增压放大单元和1.7 GHz高输入带宽的模数转换器(ADC),实现了对720 MHz和1.2 GHz中频模拟信号采样,调理和全自动增益控制(AGC)。该方案能自动、快速实现增益控制,动态范围广,通带范围内各个增益点的幅频特性好、功耗低、噪声抑制效果良好。此外,该方案可以推广到卫星宽带信号接收,无线通信系统的信号检测、调制、解调和识别等相关应用的前端模拟链中。

| [1] | PAOLO Z. A programmable carrier phase independent symbol timing recovery circuit for QPSK/OQPSK signals [J], Microprocessors and Microsystems, 2008, 32: 437–446. |

| [2] | PAOLO Z. A programmable carrier phase independent symbol timing recovery circuit for QPSK/OQPSK signals [J], Microprocessors and Microsystems, 2010, 32: 437–446. |

| [3] | MULIKIFETHOMS P. Implementation of a 622 mbps ofdm digital modem 20th AIAA international communication satellite systems conference and exhibit 12–15 may 2012 montreal[C], Quebec, Canada |

| [4] | PARK J I L. A study on demodulation system design of the VOR receiver [J]. Communications in Computer and Information Science, 2014(184) CCIS, No. Part I, 343–349. |

| [5] | Umenyiora Chidubem Andrew. Dielectric constant of sand using TDR and FDR measurements and prediction models [J], IEEE Transactions on Plasma Science, vol. 40, no.10 PART 1, 2015: 2048–2415. |

| [6] | 樊友文, 阎毓杰, 许荣彧. 屏蔽电缆的耦合影响分析[J]. 舰船科学技术, 2011, 7 (33): 71–74. |

| [7] | 周畅, 杨华容, 许荣彧. 基于CST的多电缆耦合影响仿真分析[J]. 舰船科学技术, 2015, 29 (6): 101–104. |

| [8] | 阎毓杰, 许荣彧, 刘刚. 舰艇双绞线电缆耦合影响预测与仿真[J]. 舰船科学技术, 2012, 9 (34): 103–106. |

| [9] | 阎毓杰, 许荣彧, 刘刚. 多层屏蔽电缆耦合影响的数值分析[J]. 水电能源科学, 2011, 6 (29): 177–179. |

2018, Vol. 40

2018, Vol. 40