2. 中南大学地球科学与信息物理学院, 长沙 410083;

3. 有色资源与地质灾害探查湖南省重点实验室, 长沙 410083;

4. 山东大学空间科学研究院, 山东威海 264209

2. School of Geosciences and InforPhysics, Central South University, Changsha 410083, China;

3. Hunan Key Laboratory of Non-ferrous Resources and Geological Hazard Detection, Changsha 410083, China;

4. Institute of Space Sciences, Shandong University, Weihai Shandong 264209, China

目前提供时钟信号的器件主要有普通晶振、压控晶振、温补晶振、压控恒温晶振等(孙成城,2013).晶振输出频率精度等性能与温度有直接的关系,普通晶振频率精度较低且价格便宜,一般作为MCU等器件的时钟配置器件;压控晶振精度等特性高于普通晶振,一般用于锁相环路;温补晶振频率精度与稳定度更高一些,通常用于通信等设备中;压控恒温晶振由于高精度和高稳定性而常用于高精度采集与一些电力等高精度应用中(吴义华,2007;于生宝等,2016).由目前的一些晶振公司产品手册可知,国内外的压控恒温晶振产品输出的频率稳定度与温度、启动时间等有直接关系,经过摸底测试表明压控恒温晶振在不同温度中功耗不同,在低温环境中比常温25 ℃中甚至大1倍,因此除了增加野外工作电池容量及选择低功耗器件等常规降低功耗方法外,笔者提出了一种地球物理仪器软关机的方法与系统,从一定程度上解决了地球物理仪器的功耗问题,对于压控恒温晶振,即GPS锁定情况下采用GPS输出高稳定时钟,如果在一些GPS无法锁定的地理位置,则等待压控恒温晶振输出稳定后使用(MORION, Inc.,2014;Beijing Jingyuxing Technology Co., Ltd.,2017;严发宝等,2013).

Shinagawa等研究了ADC、采样电路等系统中的时钟抖动,并提出了一种采样电路时钟抖动的估计方法(Shinagawa et al., 1990).吴义华研究了时钟抖动与ADC采样之间的关系,并总结了已有的时钟抖动测量方法,并利用ADC测量时间间隔来确定时钟抖动的方法(吴义华,2007).胡智宏等通过对ADC及时钟抖动的研究,提出了减少时钟抖动的方法(胡智宏和廖旎焕,2011).Antonelli等在分析了环形振荡器的特点后,提出了一种基于信息量化的抖动测量方法(Antonelli et al., 2017).Abidi采用了一种时域抖动计算方法来分析CMOS环形振荡器白噪声的效率(Abidi,2006).伍小保等则分析了采样时钟抖动、相噪等与ADC输出数据的SNR的关系,结合邓贤进等课题组的研究,同时说明了时钟抖动与信号传递线路上的干扰等有很大的关系(伍小保和王冰,2016;邓贤进等,2006).

ADC芯片作为电磁法观测系统信号检测最重要的环节,主要作用是将模拟信号采样并转换为数字信号,基于连续模拟信号产生一系列定时数据样本,外部主时钟为其提供定时功能,因此该时钟的稳定性非常重要(Brannon,2000;胡智宏和廖旎焕,2011).影响时钟不稳定性的主要因素是时钟抖动,时钟抖动会导致系统的SNR降低,严重时会使系统不能工作,而时钟抖动采用时钟孔径不确定度来衡量(Brannon,2000;李林,2011;何正淼,2005).鉴于普通晶振、压控晶振、温补晶振等时钟不确定度性能差,即相噪很差,无法满足电磁法观测系统的高精度采样,因此通常采用具有优良短稳特性的压控恒温晶振与具有优良长稳特性的GPS时钟配合,发挥各自的优势,实现准确频率与高精度采样.

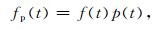

2 时钟不确定度分析ADC芯片采样过程可以看成是一个乘法过程,在频率域进行卷积(Brannon,2000;胡智宏和廖旎焕,2011).f(t)表示连续时间模拟信号输入波形,p(t)表示周期为T的理想采样函数,fp(t)为采样输出,则有(Brannon, 2000, 2004;Smith,2004)

|

(1) |

|

(2) |

对fp(t)进行频域转换则变为卷积:

|

(3) |

p(t)与P(ω)为时域和频域中的脉冲序列,进行频域转换有

|

(4) |

进一步可得

|

(5) |

式中ωs为采样频率.p(t)如果为一个理想脉冲则等同于在ADC采样时钟的上升沿.从式(1)和(2)中可以得到,采样时钟和连续时间模拟输入信号之间的卷积对全频谱有效,即集中于时钟周围的频谱细节与集中于连续时间模拟输入信号的频谱细节进行卷积.时钟周围集中的任何相位噪声都将与被测信号进行卷积,这将造成被数字化的模拟信号频谱失真.

设f(t)为一个0相位正弦信号输入ADC,该正弦信号表示为

|

(6) |

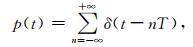

式中A为连续时间模拟输入信号f(t)的幅值,ω为连续时间模拟输入信号f(t)角频率.则其导数为

|

(7) |

当采样时钟fsamp具有抖动的时候,采样f(t)获得的数据将会有误差,该误差将会以f(t)的导数为系数变化.当式(7)值最大时相同的时钟抖动将会产生最大误差,即(Brannon,2000)

|

(8) |

若用f(t)err表示孔径不确定度误差大小,用tj表示抖动大小的孔径误差,则有

|

(9) |

若tj为均方根值,则f(t)err也同样为均方值.

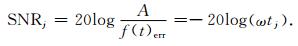

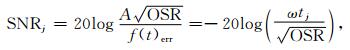

针对电磁法观测系统中的ADC芯片,先不分析ADC本身的分辨率,则由孔径不确定度来确定ADC芯片的信噪比为(Brannon, 2000, 2004)

|

(10) |

因此,为了获得更高的信噪比,必须要保证tj足够小.针对本文所选ADC为AD7760,外部主时钟fsamp=20 MHz,其内部采样时钟来自外部主时钟fsamp,频率与外部主时钟fsamp相同,由于采用的为过采样模式,其孔径不确定度引起的信噪比为(Brannon, 2000, 2004;Analog Devices, Inc.,2014a)

|

(11) |

式中OSR是ADC的过采样率,为ADC的内部时钟与数据输出速率之比.当ω一定,OSR与tj直接影响信噪比.由信噪比、连续时间模拟输入信号最大频率及OSR已知,则可得到tj:

|

(12) |

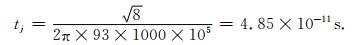

根据电磁法观测系统要求,信号频率高达93 kHz,为了定性计算,信噪比要求一定,当采样率最大时,对tj要求最苛刻,AD7760使用2.5 MHz采样率计算时钟孔径不确定度误差要求,此时按照100 dB的信噪比来进行计算.

列出相关参数:

数据输出速率为2.5 MHz;

内部时钟频率为20 MHz;

输入最大信号频率为93 kHz;

信噪比为100 dB.

则有

|

(13) |

因此在最大数据输出速率2.5 MHz的情况下,孔径不确定度的时钟抖动误差为48.5 ps.当满足这个时钟抖动条件时,ADC芯片输出数据速率或连续时间模拟输入信号的频率降低都会使信噪比增大.

普通晶振由于本身的相噪过大,其时钟抖动大于48.5 ps,而压控恒温晶振本身具优良的短稳特性,但在温度控制上具有时滞特性,所以单纯采用压控恒温晶振会使采样频率不稳定,造成长时间的数据信噪比增大,因此如果结合GPS或北斗的PPS长稳特性规范压控恒温晶振的温度控制电压进行压控恒温晶振的温度控制,将会使压控恒温晶振在一定的时间内达到采样时钟的要求.

4 压控恒温晶振跟踪PPS技术采用GPS和北斗兼容的设计模式,两者信号可以完全兼容,GPS覆盖率比北斗覆盖率高,本过程中以GPS为例进行说明.

当GPS锁定时,输出时钟没有累计误差,经过测试ublox模块(GPS接收模块)的PPS脉冲的频率稳定性小于0.1 μs·s-1,由此可知根据其输出得到的20 MHz信号产生的时钟抖动远小于ADC所需的最大抖动误差,可采用GPS输出的时钟来保证ADC芯片采样时钟的孔径不确定度.当GPS失锁时,需采取其他方法来保证ADC的时钟信号质量.为了保证时钟的稳定性,研究者采用很多方法,如恒温晶振驯服、原子钟驯服等,由于原子钟价格昂贵,所以目前普遍使用恒温晶振驯服的方法来解决时钟问题.因此,文中使用恒温晶振驯服的方法.

GPS输出两个时钟信号,分别是PPS秒脉冲与可以设置频率的时钟输出信号,本文在测试稳定的基础上使用8 MHz频率输出,然后使用PLL芯片使其变成10 MHz时钟信号送给FPGA.然后针对恒温晶振进行10 MHz时钟频率的稳定性控制.

采用漂移和相位噪声都较低的压控恒温晶振OCXO芯片MV180-CD-10.0 MHz,该芯片为俄罗斯MORION公司的产品,输出标准频率10 MHz,短稳小于2×10-12/s,长稳度为±1×10-10,25 ℃下启动时间小于10 min,采用5 V参考电压的时候,控制端输入电压范围为0~5 V,频率调整范围为-3~+3 Hz,控制端电压和频率调整成线性关系(MORION, Inc.,2014).

采用MV180-CD-10.0 MHz得到的输出时钟频率在启动后接近10 MHz,但由于温度对压控恒温晶振输出信号频率有一定的影响,且该响应需要一定的时间,快速调整压控端输入电压会使得恒温晶振出现过调,这种频率稳定性不能长期保证,因此需要根据GPS的PPS信号对压控恒温晶振进行频率调制.

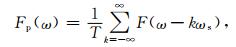

以FPGA为控制器,在GPS模块锁定后通过串口为ARM提供时间信息,并为FPGA提供PPS信号和经过PLL转换为10 MHz的时钟信号.同时在FPGA的控制下,由16 bit的DAC芯片AD5541给压控恒温晶振提供电压,如图 1所示硬件组成图(Analog Devices, Inc.,2014b).

|

图 1 压控恒温晶振跟随GPS时钟框图 Fig. 1 The OCXO clock following GPS diagram |

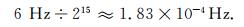

为使AD5541满足0到+5 V的输出范围,特使用运放OP196对其进行同相2倍放大,去除非线性误差等影响,此时其16 bit的精度被压缩为15 bit左右,电压分辨率为0.000153 V,而压控恒温晶振起伏频率为6 Hz,则在起伏频率上频率最小步进为:

|

(14) |

该步进量加上标准频率能够达到亚ps级,因此满足ADC的时钟抖动误差.

为了使得MV180-CD-10.0 MHz输出的10 MHz频率和GPS输出的频率相一致,抖动误差小,因此要针对MV180-CD-10.0 MHz输出对GPS输出的PPS进行跟踪,只有当误差一定的时候能够满足要求.

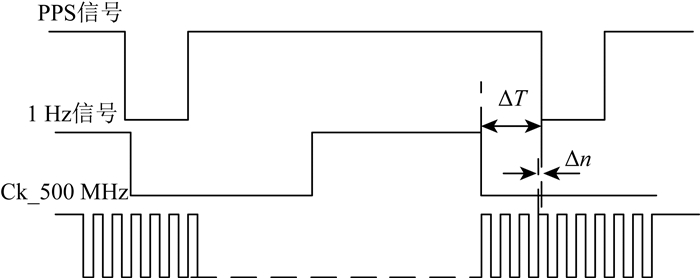

首先在GPS有效产生PPS信号时,采用FPGA对MV180-CD-10.0 MHz进行分频,产生1 Hz信号.若该1 Hz信号与PPS信号一致,则能保证其输出的10 MHz时钟信号抖动误差满足要求.然后把该1 Hz信号和PPS信号进行相位对比,得出两者相位差.最后根据得出的相位差对压控恒温晶振MV180-CD-10.0 MHz进行控制.其中,获得两者相位差有很多办法,对比而言,延迟线内插法要更为精确,因此采用延迟线更优(淳少恒等,2015;冯志辉等,2010;田洪现等,2005).图 2为1 Hz信号与PPS相位误差测量图,Ck_500 MHz为MV180-CD-10.0 MHz采用FPGA内部PLL倍频获得的500 MHz信号,利用该高频信号对相位误差进行粗测量,测得的数量为整数.剩余的误差采用FPGA内部构造延迟线法,选用专用进位单位CARRY4或者计数器都可以获得延迟线,在文献(淳少恒等,2015)有详细描述,则得到的误差如图 2所示,有(张超和郑勇,2001;党晓圆等,2009;王卿,2007)

|

图 2 PPS相位误差测量图 Fig. 2 PPS phase error |

|

(15) |

ΔT为相位总误差,m为整数,Δn为延迟线获得精密测量误差值,当1 Hz信号比PPS相位超前,则ΔT为正,否则为负.

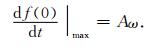

得到相位误差之后,要对1 Hz信号进行控制.根据控制原理,相当于1 Hz信号跟踪GPS锁定状态下的PPS信号.因此采取常用的PID算法解决该跟踪问题较为简单.

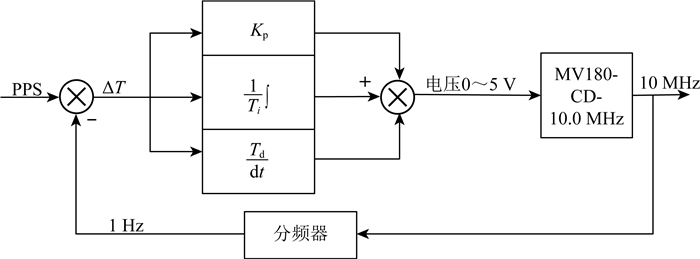

结合实际情况,采用PID算法框图如图 3所示,由PID公式则有(王伟等,2000;严发宝等,2015):

|

图 3 Hz信号PID跟踪PPS结构框图 Fig. 3 The structure diagram of 1 Hz signal PID tracking PPS |

|

(16) |

|

(17) |

式中u(t)为图 3中电压0至+5 V的控制电压,Kp为比例控制参数,Ti积分时间参数,Td为微分时间参数.

由于微分容易产生过冲现象,所以此处舍弃,而只用比例可以调整达到平稳的速度,积分控制可以消除余差,减小稳定后的振荡误差.

对公式(17)化简,得到:

|

(18) |

式(18)中u1为当前输出控制量,u0为上一个控制量,两者范围为0至+5 V,e1、e0分别为当前相位误差和上一个相位误差,k0为上一次因子,一般在0.9至1之间取值,k为调整系数.

k0在实际设计根据测试选择0.97,然后根据ΔT讨论k的取值,k与ΔT大小进行一个映射关系.ΔT绝对值大取大,ΔT绝对值小取小,根据这个原则来整定k的取值.把ΔT绝对值分成5个区间,中间3个区间为等量级区间,在设计中k设计成分段取值的方法分成5个区间,当ΔT绝对值落在某一个分段区间,就取相应的值来对压控恒温晶振进行控制,则k由大到小分别为:40、15、8、3、1.也可以根据实际情况调整为其他值.

由于不同的压控恒温晶振在PID取值时不一样,因此参数要根据实际情况对k和k0进行微调整定,所分区间越多,控制的越精确(马佳光,1989;徐智勇等,1998).映射到相应的值之后,根据得到的值换算为二进制,并对AD5541进行控制,输出总电压,由此电压控制MV180-CD-10.0 MHz.

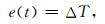

5 测试验证经过测试,1 Hz信号跟踪GPS锁定后产生的PPS信号,跟踪时间越久,当GPS失锁后保持当前控制电压获得的频率准确性越高.1 Hz信号跟踪PPS信号2 h后,经过测试跟踪精度可以保持到40 ns以内,此时压控恒温晶振输出的10 MHz信号倍频成20 MHz后能够满足ADC采样时钟孔径不确定度的误差要求,图 4为跟踪相位测试图.

|

图 4 Hz信号跟踪PPS相位测试图 Fig. 4 The phase test diagram of 1 Hz signal tracking PPS |

图 4主要比较横坐标时间轴,从图 4中可观察到,二者相位相差在25 ns以内,可见,压控恒温晶振产生的时钟源是满足ADC时钟精度要求.

两个信号经过2 h以上的跟踪后,让GPS失锁,然后利用示波器进行两个信号的长时间比对,经过统计,如表 1所示,当1 Hz信号稳定后,拔掉GPS天线或者把系统移至室内使其失锁,压控恒温晶振MV180-CD-10.0 MHz与标准锁定GPS的PPS对比在1.5 h内漂移小于380 ns,而4 h内漂移小于1.3 μs,经过转换后满足ADC采样时钟的孔径不确定误差,因此压控恒温晶振MV180-CD-10.0 MHz跟踪GPS获得校准后,4 h内可以进行替代GPS产生采样时钟.

|

|

表 1 GPS失锁后1 Hz信号与PPS的跟踪误差统计 Table 1 Statistical analysis of tracking error of 1 Hz signal and PPS after GPS lock off |

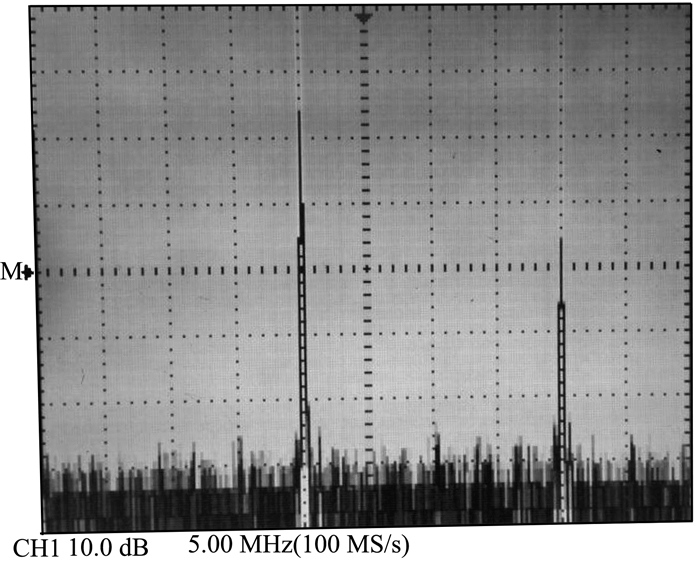

图 5为实验中压控恒温晶振与性能稳定的普通晶振对比测试图,由于仪器的原因只能观测出相噪曲线走向,但是可从图中看出普通晶振在2 kHz与3 kHz相噪位置上具有很大的相位噪声,说明该普通晶振具有很大的相位抖动.由于相噪曲线是逐渐减小的,则可以推断普通晶振比压控恒温晶振的临近噪声(1~100 Hz)大很多.

|

图 5 压控恒温晶振与普通晶振的相噪特性 (a)压控恒温晶振的相噪特性;(b)普通晶振的相噪特性. Fig. 5 Phase noise of OCXO and crystal oscillator (a) Phase noise characteristics of OCXO; (b) Phase noise characteristics of crystal oscillator. |

图 6为由压控恒温晶振MV180-CD-10.0 MHz独立产生的10 MHz经过转换后的ADC采样时钟频谱图,虽然输出功耗不准确且测量的阻抗不匹配,得不到准确的功率信号,但还能清楚地观察到20 MHz的信号为主信号.

|

图 6 采样时钟频率特性 Fig. 6 Spectrum characteristics of sampled clock |

GPS锁定时,其输出的PPS信号用来同步2路ADC进行数据采样,当GPS失锁后,由校准后的压控恒温晶振MV180-CD-10.0 MHz产生的10 MHz信号分频得到的1 Hz信号进行同步数据采集.同样,在GPS失锁后,时间参数由1 Hz信号输入ARM进行自然累计.

当电磁法观测系统进行低频数据采集的时候,为了获得更高的SNR,需要降低采样率,这个时候根据所选ADC的要求,利用PLL使得FPGA输出时钟为ADC芯片所需时钟.

6 结论时钟电路是地球物理仪器数据检测的重要组成部分,直接影响了最终获取数据的信噪比和动态性能.本文重点讨论了地球物理仪器中信号检测时钟抖动的来源及确定方法,以及对最终数据质量的影响,通过利用PID的改进算法使用恒温晶振跟踪GPS的秒脉冲信号来保证低抖动时钟的输出,为地球物理仪器信号检测提供了高精度的时钟.该实现方法在满足时钟指标的基础上,简单易于实现,整个参数整定过程容易确定,避免了使用较为复杂的电路系统或算法.通过实验测试可知,该方法具有良好的效果.确定及降低时钟抖动的方法可以应用于大部分的数据采集系统中.

致谢感谢中国兵器工业第五八研究所工程师提供的帮助,也感谢中国科学院光电技术研究所5室相关研究人员的帮助.

Abidi A A.

2006. Phase noise and jitter in CMOS ring oscillators. IEEE Journal of Solid-State Circuits, 41(8): 1803-1816.

DOI:10.1109/JSSC.2006.876206 |

|

Analog Devices, Inc. 2014a. AD7760-2.5 MSPS, 24-Bit, 100 dB Sigma-Delta ADC with On-Chip Buffer. http://www.analog.com/en/products/analog-to-digital-convertersad-converters/ad7760.html.

|

|

Analog Devices, Inc. 2014b. AD5541: 2.7 V to 5.5 V, Serial-Input, Voltage-Output, 16-Bit DAC. http://www.analog.com/en/products/digital-to-analog-converters/da-converters/ad5541.html.

|

|

Antonelli M, de Micco L, Larrondo H A.

2017. Measuring the jitter of ring oscillators by means of information theory quantifiers. Communications in Nonlinear Science & Numerical Simulation, 43: 139-150.

|

|

Beijing Jingyuxing Technology Co., Ltd. 2017. OCXOs' introduction. http://en.jfvny.com/products_l/pmcId=23.html.

|

|

Brannon B. 2000. Aperture Uncertainty and ADC System Performance. Applications Note AN-501. Analog Devices, Inc.

|

|

Brannon B. 2004. Sampled systems and the effects of clock phase noise and jitter. Applications Note AN-756. Analog Devices, Inc.

|

|

Chun S H, Chen R J, Xiang B W, et al.

2015. Frequency correction method of OCXO and its application in the data acquisition of electrical prospecting. Progress in Geophysics , 30(4): 1870-1881.

DOI:10.6038/pg20150448 |

|

Dang X Y, Shan Q X, Xiao C Y, et al.

2009. Research on voltage-controlled crystal oscillator calibration based on GPS&BD double time service. Computer Measurement & Control , 17(11): 2246-2248.

|

|

Deng X J, Li J Y, Zhang J.

2006. Accurate phase noise prediction and simulation in PLL synthesizers. Journal of Circuits and Systems , 11(5): 128-131.

|

|

Feng Z H, Liu E H, Yue Y J.

2010. FPGA delay-line interpolation method for laser range finding. Opto-Electronic Engineering , 37(4): 53-59.

|

|

He Z M. 2005. Research on high speed sampling ADC and clock signal [Ph. D. thesis] (in Chinese). Beijing: University of Science and Technology of China.

http://d.wanfangdata.com.cn/Thesis/Y730789 |

|

Hu Z H, Liao N H.

2011. Research of clock jitter and its effect on high-speed data conversion. Microcomputer & Its Applications , 30(2): 85-88.

|

|

Li L.

2011. Analysis and application of effect caused by clock jitter on high-speed ADC. Computer Engineering and Applications , 47(8S): 245-248.

|

|

Ma J C.

1989. The basic technologies of the acquisition, tracking and pointing systems. Opto-Electronic Engineering(3): 1-42.

|

|

MORION, Inc. 2014. Double Oven Low Profile Ultra Precision OCXO MV180. http://www.morion.com.ru/catalog_pdf/18_MV180.pdf.

|

|

Shinagawa M, Akazawa Y, Wakimoto T.

1990. Jitter analysis of high-speed sampling systems. IEEE Journal of Solid-State Circuits, 25(1): 220-224.

DOI:10.1109/4.50307 |

|

Smith P. 2004. Little Known Characteristics of Phase Noise. Application Note AN-741. Analog Devices, Inc.

|

|

Sun C C. 2013. Study on low aging rate and compensation of high stability crystal oscillator[Master's thesis] (in Chinese). Xi'an: Xidian University.

http://cdmd.cnki.com.cn/Article/CDMD-10701-1013295398.htm |

|

Tian H X, Yang G X, Gao Z B.

2005. Design of the delay line based on the high-speed digital circuit. Measurement & Control Technology , 24(4): 72-74.

|

|

Wang Q, Song T C, Feng Y.

2007. Method of accurate timing based on GPS technology. Journal of Electrical & Electronic Education , 29(4): 34-38.

|

|

Wang W, Zhang J T, Chai T Y.

2000. A survey of advanced PID parameter tuning methods. Acta Automatica Sinica , 26(3): 347-355.

|

|

Wu X B, Wang B.

2016. Research on clock jitter、phase noise and output SNR relationship. Information & Communications(6): 30-32.

|

|

Wu Y H. 2007. Study on technology of ADC measure the clock [Ph. D. thesis] (in Chinese). Beijing: University of Science and Technology of China.

http://cdmd.cnki.com.cn/article/cdmd-10358-2007098187.htm |

|

Xu Z Y, Yuan J H, Huang Z H, et al.

1998. Method study on accurately correction of the system errors of the photoelectric theodolite. Opto-Electronic Engineering , 25(S1): 55-58.

|

|

Yan F B, Dong H, Yao H C, et al. 2013. The way and system of soft shutdown in geophysical instruments (in Chinese). CN, 201310635090.7.

|

|

Yan F B, Su Y R, Yang H, et al.

2015. High-precision optical platform focusing control system. High Power Laser and Particle Beams , 27(9): 56-61.

|

|

Yu S B, He J L, Su F, et al.

2016. Design of high precision synchronization system for electromagnetic instruments. Journal of Central South University (Science and Technology) , 47(12): 4035-4040.

|

|

Zhang C, Zheng Y.

2001. Research of accurate timing by using GPS OEM chip. Journal of Information Engineering University , 2(4): 50-53.

|

|

淳少恒, 陈儒军, 向毕文, 等.

2015. OCXO时钟修正机制在电法勘探采集中的应用研究. 地球物理学进展, 30(4): 1870–1881.

DOI:10.6038/pg20150448 |

|

党晓圆, 单庆晓, 肖昌炎, 等.

2009. 基于GPS与北斗双模授时的压控晶振校频系统的研究与设计. 计算机测量与控制, 17(11): 2246–2248.

|

|

邓贤进, 李家胤, 张健.

2006. 锁相频率合成器相位噪声的精确估计与仿真. 电路与系统学报, 11(5): 128–131.

|

|

冯志辉, 刘恩海, 岳永坚.

2010. 基于FPGA延迟线插入法的半导体激光测距. 光电工程, 37(4): 53–59.

|

|

何正淼. 2005. 高速采样ADC和时钟信号的研究[博士论文]. 北京: 中国科学技术大学.

http://d.wanfangdata.com.cn/Thesis/Y730789 |

|

胡智宏, 廖旎焕.

2011. 高速adc时钟抖动及其影响的研究. 微型机与应用, 30(2): 85–88.

|

|

李林.

2011. 时钟抖动对高速ADC性能影响的分析和应用. 计算机工程与应用, 47(8S): 245–248.

|

|

马佳光.

1989. 捕获跟踪与瞄准系统的基本技术问题. 光电工程(3): 1–42.

|

|

孙成城. 2013. 高稳定度晶体振荡器的低老化及补偿问题研究[硕士论文]. 西安: 西安电子科技大学.

http://cdmd.cnki.com.cn/Article/CDMD-10701-1013295398.htm |

|

田洪现, 杨公训, 高忠伯.

2005. 基于高速数字电路的延迟线设计. 测控技术, 24(4): 72–74.

|

|

王卿, 宋铁成, 奉媛.

2007. 基于GPS技术进行精确授时的方法. 电气电子教学学报, 29(4): 34–38.

|

|

王伟, 张晶涛, 柴天佑.

2000. PID参数先进整定方法综述. 自动化学报, 26(3): 347–355.

|

|

伍小保, 王冰.

2016. 采样时钟抖动、相噪与输出snr关系研究. 信息通信(6): 30–32.

|

|

吴义华. 2007. 利用ADC测量时钟技术的研究[博士论文]. 北京: 中国科学技术大学.

http://cdmd.cnki.com.cn/article/cdmd-10358-2007098187.htm |

|

徐智勇, 袁家虎, 黄祖华, 等.

1998. 精确修正光电经纬仪中的系统误差方法研究. 光电工程, 25(S1): 55–58.

|

|

严发宝, 董海, 姚红春等. 2013. 一种地球物理仪器软关机的方法和系统. CN, 201310635090. 7.

|

|

严发宝, 苏艳蕊, 杨洪, 等.

2015. 高精度光学平台调焦控制系统. 强激光与粒子束, 27(9): 56–61.

|

|

于生宝, 何建龙, 苏发, 等.

2016. 电磁法仪器高精度GPS同步系统设计. 中南大学学报:自然科学版, 47(12): 4035–4040.

|

|

张超, 郑勇.

2001. 利用GPS OEM板进行精确授时的研究. 信息工程大学学报, 2(4): 50–53.

|

|

2017, Vol. 60

2017, Vol. 60