为了实现某高速实时系统中的大量数据存储需求,提出了一种基于双倍速率同步动态随机存储器的短周期存储方法.概述了双倍速率同步动态随机存储器控制器的读、写操作基本原理.为了解决数据持续性交替读入和写出存储器且存取顺序不一致的实际问题,设计了一种短周期存储方法.按照数据存取方式的不同可分为单次突发和多次突发2种模式,其中少行多列的存储结构可使多次突发模式下短周期读写速度进一步提高.对基于双倍速率同步动态随机存储器的短周期存储方法进行了性能分析和功能仿真,结果表明,多次突发模式下的短周期存储方法可以少量的现场可编程门阵列片上存储资源和较高的数据读写速率实现存储需求.

To meet the storage requirements of mass data in a high-speed and real-time system, a short-period storage method based on double data rate 2 synchronous dynamic random access memory(DDR2 SDRAM) was proposed. First, the basic principles of reading and writing operation of DDR2 SDRAM controller are summarized. Then, in order to solve the practical problem of reading and writing data in different orders continuously and alternately, a short-period storage method was designed, which can be divided into two modes of single burst and multiple burst according to the different data access modes. In the multiple burst mode of short-period storage method, the storage structure of fewer rows and more columns can further improve the speed of reading and writing data. At last, the performance analysis and function simulation of the short-period storage method based on DDR2 SDRAM is carried out. It is shown that the short-period storage method in the mode of multiple burst can achieve the storage requirement with a small amount of internal storage resource of field-programmable gate array(FPGA) and high speed of reading and writing data.

在某系统的工程实现过程中,数据处理时钟达到百兆赫兹级别,所需存储数据量为百万比特量级,大量的数据存储不适合采用现场可编程门阵列(FPGA,field-programmable gate array)片上存储方式,须通过片外高速存储器配合FPGA工作以达到大量数据快速读出和写入的存储需求.结合低发热量、低功耗、低成本等需求[1-2],选用双倍速率同步动态随机存储器(DDR2SDRAM,double data rate 2 synchronous dynamic random access memory)作为系统的片外存储器.

目前,DDR2多用于长时间单独读数据或单独写数据操作[3-4].而在某系统实现中,要求数据持续写入的同时完成大量数据的读出,如果将存储设计为长时间读数据操作或长时间写数据操作,则需要消耗大量的片上存储资源才能满足读写数据操作持续交替进行的需求.在上述背景下,笔者提出DDR2的短周期内多次突发的存储方法,以很少的片上存储和处理资源完成大量数据的高速存取,并保证DDR2的读写效率和数据可靠性.最后结合功能仿真实验,分析了新方法的可行性和数据传输速率.

1 MIG控制DDR2存储器原理DDR2 SDRAM在读、写操作过程中需要进行初始化、刷新、预充电、激活等操作[5]. ISE为用户提供了IP核MIG,自动完成DDR2初始化等基本操作,其工作模式为突发传输,突发长度LBurst可设置为4或8[6].用户通过MIG对DDR2存储器中读写数据主要分为以下3步.

1)用户通过MIG的用户接口发送地址信息,并存入地址FIFO中,其中地址信息中包含读写命令,MIG提供地址FIFO溢出标识指示地址FIFO的状态;

2) DDR2控制器检测到地址FIFO非空后,将地址信息从FIFO中读出后转化为控制指令,发送给DDR2存储器;

3)读操作中,经过读延迟tRL后,DDR2存储器将相应地址的数据输出到DQ总线上,写入数据FIFO中,将DDR2工作时钟上升沿及下降沿的输出数据拼接好后,然后输出至MIG相应接口;写操作中,数据FIFO将相应地址数据按照DDR2工作时钟上升沿及下降沿数据拆分好后,发送到DQ总线上传输到DDR2储存器,经过写延迟tWL后,DDR2将数据写入对应存储地址.其中tRL=tCL+tAL,tWL=tRL-1,行选通延迟tCL和行选通附加延迟tAL均在MIG的建立过程中设置.

读写操作中MIG使用用户输入的地址信息控制DDR2,MIG反馈给用户的信息包括数据及地址FIFO溢出标识.若地址信息存入地址FIFO中的速度超过控制指令的处理速度,将导致地址FIFO溢出,此时地址FIFO溢出标识由0变为1,地址信息丢失,对应数据读出或写入失败.因此,用户必须设计合适的读写控制时序来保证操作的正常运行和数据正确,并且实时监测FIFO溢出标识和调整时序,实现程序可控.

2 基于DDR2 SDRAM的短周期存储方法笔者将基于某系统工程实现的背景需求进行讨论. FPGA采用Xilinx Virtex-5 XC5VFX130T,DDR2 SDRAM采用Micron的MT47H32M16NF-25E.这款DDR2每个存储单元的数据位宽为16 bit,10条列地址线,容量为512 Mbit. FPGA工作时钟为100 MHz,DDR2工作时钟为200 MHz.

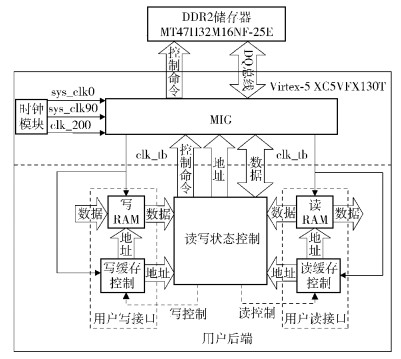

在实际应用中,数据存储速率需求常常和MIG与用户之间的接口数据速率要求不一致,因此用户需要对MIG进行状态控制.如图 1所示,用户端主要分为用户写接口、用户读接口和读写状态控制3大部分.

|

图 1 存储控制整体结构框图 |

某系统的具体存储需求为,数据位宽为16 bit,每1 ms需要将5万个数据顺序写入存储器,每8 ms需要将32×5万个数据按非写入顺序读出,即在DDR2读写顺序不一致的前提下,要求平均写速率Rw达到0.8 Gbit/s,平均读速率Rr达到3.2 Gbit/s.可将存储数据用矩阵形式表示为

| $ \boldsymbol{Y} = \left[ {\begin{array}{*{20}{c}} {{y_{1,1}}}& \cdots &{{y_{1,32}}}\\ { \vdots \;}&{{y_{i,j}}}&{ \vdots \;}\\ {{y_{50\;000,1}}}& \cdots &{{y_{50\;000,32}}} \end{array}} \right] $ |

其中:yi, j为第j ms的第i个数据,每个数据16 bit位宽.则每1 ms需要将5万个数据顺序写入存储器(y1, j, y2, j, …, y50 000, j),每8 ms将Y中所有数据按顺序y1, 1, y1, 2…, y1, 32, …, yi, 1, yi, 2…, yi, 32, …全部读出.由此可知,笔者提出的存储需求有以下3个实现难点:

1)由于片上存储资源有限,用户控制程序应该以最小的片上存储资源完成时序控制.

2)以1 ms为周期,读操作和写操作交替持续性执行,且数据传输速率要求较高.

3)数据存、取顺序不一致.如果按照常规逐行存储方式,地址操作将在不同行中频繁转换.

针对上述存储要求和MIG突发传输特性,笔者提出基于DDR2的短周期存储方法.将长时间DDR2的单独读数据操作或单独写数据操作分割为短周期内读、写数据操作的交替进行.短周期的周期长度和周期内的读写次数需要按照存储要求来具体设置,以使得数据传输速率和效率达到最佳.根据存取方式的不同,下面将分别从单次突发和多次突发2种模式进一步阐述短周期存储方法和涉及的独特存储结构.不失一般性,突发长度LBurst设置为4,设置为8时的分析方法一致.

2.1 基于单次突发的短周期存储基于单次突发的短周期存储方法,即根据存储需求设定周期长度,在每个周期内只执行1次突发写操作和1次突发读操作.

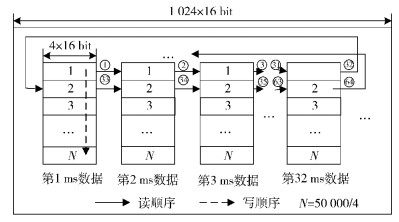

如图 2所示,每一格表示单次突发操作的连续4个存储单元.则每1 ms数据在列方向占据4个存储单元,那么32 ms数据占据128个存储单元.每毫秒的5万个16 bit位宽的数据按输入先后顺序写入图中对应ms下的标号1, 2, 3, …, N(N=50 000/4)的存储单元中.同时每8 ms时间段内将32×50 000个数据逐行(图中实线箭头所示顺序)全部读出.也就是说,在1 ms的时间内,至少需要执行N次写操作和4N次读操作,那么每1 ms至少需要划分为4N个短周期才能使所有数据读写完毕.

|

图 2 单次突发的短周期存储方法示意图 |

从MIG时延要求考虑,基于单次突发的短周期存储的周期长度L由1次读操作和1次写操作所需时长,以及刷新和换行等基本操作造成的时延共同确定.在前述硬件条件下,将读写短周期L设为32个时钟周期,可防止FIFO溢出标志拉高(具体分析详见文章第3部分).在此基础上,进一步分析算法实现资源消耗和数据读写速率是否满足存储需求.

2.2 基于多次突发的短周期存储MIG控制DDR2的读写操作中,换行操作将造成额外延迟,降低数据读写效率,极易导致MIG FIFO溢出.上述基于单次突发的短周期存储方法,时序控制逻辑简单,FPGA处理资源消耗低.但不同行地址的读写操作交替进行,每个周期L内平均进行2次换行操作,执行延迟较大.虽然可通过合理增大周期长度来确保FIFO不溢出,但是直接导致DDR2读写效率下降,不适用于数据传输速率要求高的系统.为此提出基于多次突发的短周期存储方法,即在设定的读写短周期内进行若干次连续的突发读操作和连续的突发写操作,同时配合采用少行多列的存储结构,以减少DDR2地址换行的次数,提高DDR2数据存取效率.

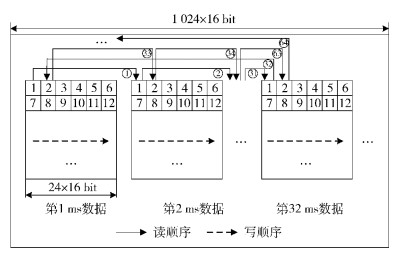

如图 3所示,在逻辑层面将存储空间划分为少行多列结构,图 3中最小格代表连续4个存储单元.则每1 ms数据在列方向占据24个存储单元,那么32 ms数据占据24×32个存储单元.每1 ms必须将数据按输入先后突发写入对应毫秒下的标号1, 2, 3, …的存储单元中,直至5万个数据全部写入.同时每8 ms时间段内必须将32×5万个数据以图 3中实线箭头所示顺序①②③…一一读出.

|

图 3 多次突发的短周期存储方法示意 |

基于多次突发的短周期存储方法的实现过程中,1个周期L划分为读周期和写周期2部分,读周期内执行多次突发读操作,写周期内执行多次突发写操作.周期长度L和1个周期内读、写操作的次数则需要根据具体应用背景进行合理设置(具体分析详见文章第3部分).在笔者的应用背景下将读写短周期L设为128个时钟周期,在此周期内DDR2执行突发读操作32次,突发写操作12次,每个周期内平均进行3次换行操作.

3 短周期存储方法的性能分析上面介绍了基于DDR2 SDRAM的短周期存储方法,假定长度为L的1个周期内突发读操作m次,读出数据涉及u行,突发写操作n次,写入数据涉及v行,m、u、n和v均为正整数.当m=n=1时,为单次突发模式,否则为多次突发模式,所以单次突发模式为多次突发的短周期存储方法的一种特殊形式.

在保证MIG中FIFO不溢出的原则下,结合存储需求分别计算出单次突发和多次突发模式下的参数合理值,并分析资源消耗量和数据存储速率.将用户程序、MIG相应代码和测试程序添加到ISE工程,在Xilinx ISE14.4编程环境下进行功能仿真,验证数据存取的正确性,最后给出FPGA片上资源消耗情况.

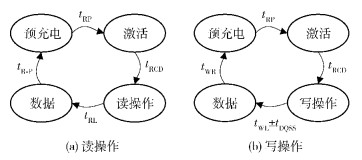

3.1 参数选择 3.1.1 MIG时延首先分析MIG地址和数据FIFO不溢出的原则下参数所需满足的关系. DDR2的突发读、写操作过程有分别包含4个状态,转换过程如图 4所示.

|

图 4 读、写操作状态转换过程 |

图 4(a)和(b)中各状态连接线上的符号表示状态间转换所需时延,表 1进行说明.其中,tRP为行地址预充电时延,tRCD为行寻址到列寻址的延迟,tDQSS为数据选取脉冲上升沿到时钟上升沿时延,tWR为写恢复时延. tR-P为读命令到预充电命令时延,tR-P=tAL+LBurst/2-2tCK+max(tRTP/tCC, 2tCK),tCK为DDR2工作时钟周期,tRTP为内部读命令到预充电命令时延,tCC为内存时钟周期;tRP、tRCD、tRTP、tDQSS、tCC和tWR由DDR2型号决定.

|

|

表 1 基于单次及多次突发的短周期存储性能比较 |

对于短周期存储方法,为保证MIG中FIFO不会溢出,则必须使得周期长度不小于1个周期内操作所需的时延,即

| $ \begin{array}{l} L \ge (u + v)({t_{{\rm{RP}}}} + {t_{{\rm{RCD}}}}) + l({t_{{\rm{RL}}}} + {t_{{\rm{R-P}}}}) + \\ v({t_{{\rm{WL}}}} + {t_{{\rm{DQSS}}}} + {t_{{\rm{WR}}}}) + (2m + 2n + 1){t_{{\rm{CK}}}} \end{array} $ | (1) |

从数据读写速率角度,分析各个参数所需满足的关系.基于DDR2 SDRAM的短周期存储方法中,在1个短周期L内,可读出m×LBurst个存储单元数据,写入n×LBurst个存储单元数据,对应的平均读速率和平均写速率分别为

| $ R{'_{{\rm{rd}}}}{\rm{ = }}\frac{{16{L_{{\rm{Burst}}}}m}}{{L \times {t_{{\rm{CK}}}}}} $ | (2) |

| $ R{'_{{\rm{wt}}}}{\rm{ = }}\frac{{16{L_{{\rm{Burst}}}}n}}{{L{t_{{\rm{CK}}}}}} $ | (3) |

为完成存储要求,短周期存储方法的平均读写速率R'rd和R'wt必须达到实际所需速率Rrd和Rwt,即满足

| $ R{'_{{\rm{rd}}}} \ge {R_{{\rm{rd}}}} $ | (4) |

| $ R{'_{{\rm{wt}}}} \ge {R_{{\rm{wt}}}} $ | (5) |

查看MT47H32M16NF-25E的数据手册可知,tRP=4tCK,tRCD=3tCK,tR-P=2tCK,tRL=3tCK,(tWL+tDQSS)=2tCK,tWR=3tCK.另外,1次读出和1次写入数据均持续2个时钟周期.

对于单次突发的短周期存储方法,m=u=n=v=1,代入式(1)的右侧,结果为

| $ \begin{array}{l} 2{t_{{\rm{RP}}}} + 2{t_{{\rm{RCD}}}} + {t_{{\rm{RL}}}} + {t_{R-P}} + {t_{{\rm{WL}}}} + {t_{{\rm{DQSS}}}} + {t_{{\rm{WR}}}} + \\ \;\;\;\;\;\;\;4{t_{{\rm{CK}}}}{\rm{ = }}28{t_{{\rm{CK}}}} \end{array} $ |

说明DDR2 SDRAM完成1次突发读操作和1次突发写操作至少需要28个时钟周期.为留有余量,设置短周期长度L为32tCK,仿真结果如图 5所示.监测到溢出标识“app_wdf_afull”和“app_af_afull”保持“0”状态,MIG存取操作正常,数据正确.

|

图 5 单次突发的短周期存储仿真结果L=32tCK |

对于多次突发的短周期存储方法,不妨设m=32,u=1,n=12,v=2,代入式(1)的右侧计算得

| $ \begin{array}{l} 3({t_{{\rm{RP}}}} + {t_{{\rm{RCD}}}}) + {t_{{\rm{RL}}}} + {t_{R-P}} + \\ 2({t_{{\rm{WL}}}} + {t_{{\rm{DQSS}}}} + {t_{{\rm{WR}}}}) + 88{t_{{\rm{CK}}}}{\rm{ = }}124{t_{{\rm{CK}}}} \end{array} $ |

说明DDR2可在124个时钟周期内完成32次突发读和12次突发写操作.为留一定时延余量,设置短周期长度L为128tCK.仿真结果如图 6所示,显示溢出标识“app_wdf_afull”和“app_af_afull”保持“0”状态,表明多次突发的短周期存储方法的参数设置合适,MIG正常工作,数据正确.

|

图 6 多次突发的短周期存储仿真结果L=128tCK |

为分析的连贯性,沿用上文的参数,对于单次突发的短周期存储方法,m=u=n=v=1,L=32tCK,对于多次突发的短周期存储方法,不妨设m=32,u=1,n=12,v=2,L=128tCK.传统存储方法中,MIG对DDR2连续地址进行读写操作,无须考虑地址换行造成的延迟.笔者选用的DDR2位宽为16 bit,工作时钟为200 MHz,要求平均写速率Rwt为0.8 Gbit/s,平均读速率Rrd为3.2 Gbit/s.根据式(2)和式(3)分别计算得到单次突发和多次突发的短周期平均读、写速率.

表 1结果表明,传统存储方法中,DDR2在2个时钟周期内读出或写入4个存储单元数据,DDR2平均读速率和平均写速率为3.2 Gbit/s,吞吐量可达到6.4 Gbit/s,达到存储要求.基于单次突发的存储方法中,在32个时钟周期内读出4个存储单元数据,写入4个存储单元数据,DDR2平均读速率为0.4 Gbit/s,平均写速率为0.4 Gbit/s,吞吐量可达到0.8 Gbit/s,在笔者存储要求速率下,显然不满足式(4)和式(5).

基于多次突发的短周期存储方法中,采用少行多列的存储结构,在128个时钟周期内读出128个存储单元数据,写入48个存储单元数据. DDR2平均读速率为1.2 Gbit/s,平均写速率为3.2 Gbit/s,吞吐量可达到4.4 Gbit/s,与基于单次突发的短周期存储方法相比,平均存取速率约提高5倍,满足式(4)和式(5),达到存储要求.

3.3 资源消耗考虑到单次突发模式的短周期存储方法无法达到背景中的存储速率需求,此处仅讨论多次突发模式下短周期存储方法和传统存储方法的资源消耗情况.在实现过程中,用户后端所需片上存储资源的大小与数据瞬时读写速率密切相关.不失客观性,仅给出笔者基于的系统实现过程中的资源消耗情况.

从表 2可以看出,在实现大量数据存取顺序不一致的存储需求下,多次突发模式下的短周期存储方法所需片上资源消耗远小于传统存储方法.

|

|

表 2 多次突发模式下短周期存储方法资源消耗 |

针对高速实时系统中对于大量数据持续性交替写入和读出存储器的需求,为节省FPGA片上存储资源,笔者提出了基于DDR2 SDRAM的短周期存储方法,根据数据存取方式可分为单次突发和多次突发2种模式.分析和仿真结果表明,在满足MIG时延要求的前提下,单次突发模式下数据存取速率达到0.8 Gbit/s,多次突发模式下数据存取速率达到4.4 Gbit/s,比前者提升约5倍,以很少的片上资源消耗完成了存取顺序不一致的实时数据存储.

| [1] | 张刚, 贾建超, 赵龙. 基于FPGA的DDR3 SDRAM控制器设计及实现[J]. 电子科技 , 2014 (1) :70–73. |

| [2] | 唐岚. 基于Xilinx V5的DDR2数据解析功能实现[J]. 电子设计工程 , 2014 (9) :124–126. Tang Lan. The function of data analysis based on Xilinx V5 DDR2[J]. Electronic Design Engineering , 2014 (9) :124–126. |

| [3] | 韩刚. 用于高速图像处理的DDR2 SDRAM控制器[J]. 西安邮电大学学报 , 2015 (4) :58–61. Han Gang. A DDR2 SDRAM controller for high-speed image data processing[J]. Journal of Xi'an University of Posts and Telecommunications , 2015 (4) :58–61. |

| [4] | 刘冠男, 欧明双, 宋何娟. DDR2 SDRAM控制器的设计及FPGA验证[J]. 中国集成电路 , 2010 (4) :42–45. Liu Guannan, Ou Mingshuang, Song Hejuan. The design of DDR2 SDRAM controller and implementation in FPGA[J]. China Integrated Circuit , 2010 (4) :42–45. |

| [5] | 徐永刚.基于FPGA与DDR2-SDRAM的高速数据缓冲器的设计与实现[D].南京:南京邮电大学, 2012. http://cdmd.cnki.com.cn/article/cdmd-10293-1012510581.htm |

| [6] | 舒展. DDR2控制器IP的设计与FPGA实现[D].合肥:合肥工业大学, 2009. http://cdmd.cnki.com.cn/article/cdmd-10359-2009156111.htm |