高速电路中, 串扰是系统速率继续提高的瓶颈之一, 现有方法只考虑了每边各一条传输线对受扰线的串扰, 这样最多能抑制75%的串扰.为了解决每边第2条传输线对受扰线的串扰, 提出了一种新的电路结构, 该电路结构根据串扰的相位抵消原则, 利用反相器的位置和数量变化抑制每边各两条传输线对受扰线的串扰.仿真结果显示, 在0.1~4 GHz范围内, 该方法能使受扰线每边第2条传输线对受扰线的远端串扰降低约10 dB.

In high-speed circuit, crosstalk is one of the bottlenecks hindering system rate to continue rising. In a 50-Ohm bus, with a spacing equal to the line width, 95% of all the crosstalk on any victim line comes from the nearest two traces on either side of the victim line. However, the current methods only consider the crosstalk from the first nearest traces, which means the crosstalk can be suppressed 75% at most. In order to solve the crosstalk from the second nearest traces, a new circuit structure was proposed, in which the position and the number of inverters could be changed according to the principle of crosstalk phase cancellation to suppress the crosstalk from the nearest two traces at same time. Simulation shows that in range of 0.1~4 GHz, far crosstalk from the second nearest trace can be eliminated about 10 dB.

在高速高密度电路中, 传输线间的串扰限制了信号的互连, 这已经成为电路系统继续提高速率的瓶颈[1].串扰是信号完整性中的主要问题之一, 它是指有害信号从一个网络转移到相邻网络.任何一对网络之间都存在串扰, 如芯片、印刷电路板、互连件及其他非屏蔽的高密度集成电路中.串扰增加了通信系统中的噪声, 恶化了系统中数字信号和模拟信号的质量[2-3].如何抑制传输线间的串扰是设计高速高密度电路的关键.

串扰的形成来源于传输线间的电磁耦合, 国内外的学者对如何抑制串扰这个问题进行了大量的研究.可将现有抑制串扰方法归为两类,一类是通过减小传输线间的电磁耦合来抑制串扰, 表现特征是从电路板和传输线的物理结构角度来考虑抑制串扰[4-9], 从理论上来说, 电磁耦合只能减小而无法消除, 因此从电路板和传输线的物理结构角度来考虑抑制串扰效果有限, 在目前电子产品尺寸逐渐减小的背景下, 这类抑制串扰方法的应用范围越来越窄; 另一类是通过对相关信号进行处理来抑制串扰, 表现特征是通过添加一些电路结构来抑制串扰[10-14], 这一类抑制串扰方法的效果较好, 但缺点是电路较复杂, 如何通过简单的电路获取更大的抑制串扰效果是研究这类方法的方向.基于效果和代价的折衷, 文献[15]提出了在干扰线中点添加反相器, 利用信号反相来抑制串扰, 这种方法的实质是在线上通过对串扰进行信号处理来抑制串扰的, 实验结果表明该方法能明显抵消微带传输线间的串扰.但是,在50 Ω总线中, 当线间距等于线宽时, 对其中的任意一条受扰线, 这种方法只是考虑了其左右两侧各一条相邻传输线的串扰, 这样最多能抑制75%的串扰, 如果要抑制95%的串扰, 这就需要考虑其左右两侧各两条相邻传输线的串扰[3].国内外的学者在现有研究抑制串扰时, 都是以两条相邻传输线为研究对象, 而没有以多条相邻传输线为研究对象, 也就是说上述这些方法仅考虑了每边第1条传输线的对受扰线的串扰, 而未考虑每边第2条相邻传输线对受扰线的串扰[4-15].笔者在利用信号反相进行串扰抵消方法的基础上提出了新的抑制多条平行耦合微带线间串扰的电路结构, 该结构利用反相器组合在抑制每边第1条传输线对受扰线远端串扰的同时能够抑制每边第2条传输线对受扰线的远端串扰.

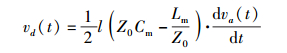

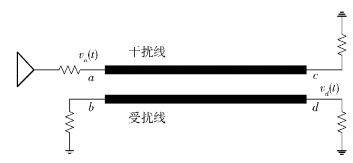

1 串扰的相位抵消原则如图 1所示的2条平行耦合微带传输线, 在忽略二次串扰后, 干扰线上a点到受扰线上远端d点的传输特性即远端串扰可表示为[12]

|

(1) |

|

图 1 传输线间的串扰模型 |

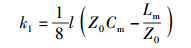

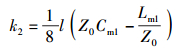

其中:Z0为传输线的特性阻抗, Cm为相邻传输线间的单位长度耦合电容, Lm为相邻传输线间的单位长度耦合电感, l为传输线的耦合长度, va(t)为干扰线上的激励信号.

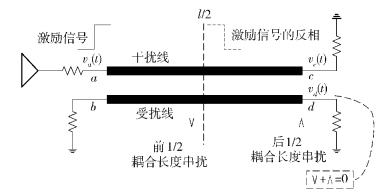

由式(1) 可知串扰的相位与激励信号的相位具有相关性, 因此可以得到如图 2所示的微带线间串扰相位抵消关系.即在干扰线的中点进行激励信号的反相, 可以使前后各1/2耦合长度所产生的串扰信号也反相, 由串扰的叠加性可知, 此时串扰完成了相位抵消, 串扰被完全抑制.平行耦合微带传输线间的串扰相位抵消原则可表述为:相邻耦合微带传输线中, 在干扰线或受扰线的中点使信号反相, 即在前1/2耦合长度和后1/2耦合长度上使串扰信号反相,即可实现串扰的相位抵消.

|

图 2 微带线间串扰的相位抵消 |

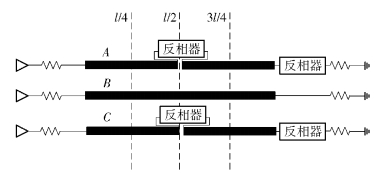

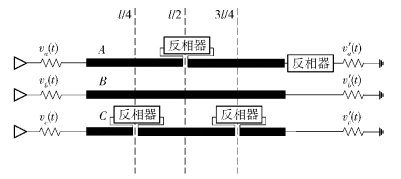

根据串扰的相位抵消原则, 可以获得应用于多条平行耦合微带传输线间串扰抵消的一般电路模型, 该模型如图 3所示.由于在50 Ω总线中, 线间距等于线宽时, 受扰线上95%的串扰来源于受扰线两边距离最近的每边各两条线. 图 3中, 以3条线为例,显然传输线A与B、传输线B与C都符合串扰相位抵消原则, 但传输线A与C却不符合, 因此需要改进该抑制串扰的电路结构, 使3条传输线中的任何两条都符合串扰的相位抵消原则.

|

图 3 利用信号反相减小串扰的电路模型[15] |

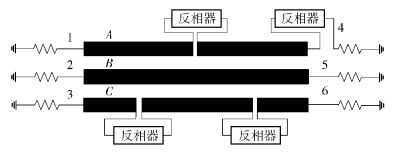

依据串扰的相位抵消原则, 图 4给出新的用于抑制多条平行耦合微带传输线间串扰的电路结构.相对于图 3方案, 图 4方案改变了传输线C上反相器的位置, 使串扰的相位抵消原则在任何两条传输线上都成立.

|

图 4 利用反相器组合抑制串扰模型 |

在3条平行且长度相等的相邻微带传输线A、B和C上, 分别输入激励信号va(t)、vb(t)和vc(t), 在忽略二次串扰的情况下推导每条传输线上的输出信号v′a(t)、v′b(t)和v′c(t).

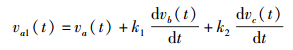

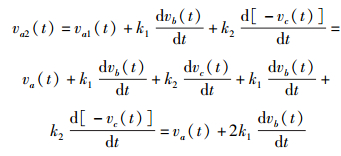

首先推导传输线A上的输出信号.显然,传输线A受到了传输线B和C的串扰叠加.由于不考虑二次串扰, 所以式(1) 依然适用于传输线A与C间的串扰计算.为了推导的方便, 记

|

(2) |

|

(3) |

其中:Cm1为受扰线与每边第2条相邻传输线间的单位长度耦合电容, Lm1为受扰线与每边第2条相邻传输线间的单位长度耦合电感.

根据式(1), 在l/4耦合长度点, 传输线A受到了传输线B和C的l/4耦合长度的串扰叠加, 此处传输线A上的信号为

|

(4) |

在l/2耦合长度点, 传输线A受到了传输线B和C的第2个l/4耦合长度的串扰叠加, 此处传输线A上的信号为

|

(5) |

在3l/4耦合长度点, 传输线A受到了传输线B和C的第3个l/4耦合长度的串扰叠加, 此处传输线A上的信号为

|

(6) |

在终点, 传输线A受到了传输线B和C的第4个l/4耦合长度的串扰叠加, 此处A上的信号为

|

(7) |

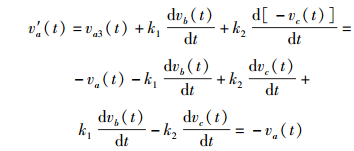

v′a(t)信号再经过反相器就得到了输入信号.同理也可推导出其他两条传输线上的输出信号就为输入信号.以上从时序的角度直观地推导出了受扰线和第3条线间的串扰抵消.

把图 4的电路结构与图 3的电路结构相比较可以看出, 在保证相邻传输线间串扰抵消的前提下, 提出的电路结构也保证了受扰线与其相邻的每边第2条传输线间的串扰抵消.同时, 对于n条传输线, 把图 4中的电路结构进行复制应用即可, 能保证受扰线与其相邻的每边两条传输线都满足串扰抵消原则.

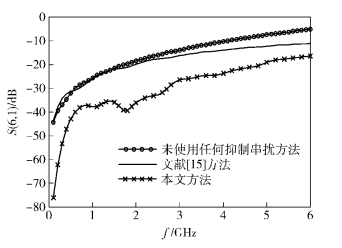

3 仿真结果与分析利用先进设计系统软件验证所提抑制多条耦合微带传输线间串扰方法的有效性.在软件版图界面创建了印刷电路板上的3条平行微带传输线, 具体参数为:微带线的宽度w=1 mm, 线间距s=1 mm, 介质厚度h=0.56 mm, 金属厚度t=70 μm, 介质相对介电常数εr=4.2, 相对磁导率μr=1, 微带线长度l=15 cm, 金属为铜, 微带线的特征阻抗约为50 Ω.利用软件提供的Momentum仿真器对布局元件进行了三维平面电磁场仿真, 然后把具有实际物理意义的布局元件引入到原理图界面进行电路仿真, 其中插入的反相器为理想的, 它能够把输入信号进行180°移相, 且在传输线上进行了阻抗匹配.电路仿真布局及端口设置如图 5所示.由于S参数可以很直观地表示串扰, 且大部分参考文献都用S参数仿真来说明串扰, 因此这里给出系统S参数的仿真结果.把传输线A记为受扰线, 从图 5的左边向右看, 那么传输线B为与受扰线相邻的右边第1条传输线, 传输线C为与受扰线相邻的右边第2条传输线.根据S参数的定义, 图 5中S(6, 1) 就为右边第2条传输线对受扰线的远端串扰.

|

图 5 提取S参数(串扰)的仿真模型 |

S参数仿真结果如图 6所示.在相同条件下, 图 6给出了使用本文方法、文献[15]方法与未使用任何抑制串扰方法这3种情况下, 第2条传输线对受扰线远端串扰的对比.从图 6可以看出, 在0.1~4 GHz范围内, 相对于其他两种方法本文方法能使每边第2条传输线对受扰线的远端串扰降低约10 dB;在4~6 GHz范围内, 能使远端串扰降低5 dB以上.

|

图 6 第2条传输线对受扰线远端串扰的仿真结果对比 |

除本文方法外, 其他2种方法中传输线A和传输线C都不具有串扰相位抵消的条件, 因此这2种情况下远端串扰的大小基本一致.但由于文献[15]方法中相邻传输线间具有串扰抵消功能, 这样传输线C上的二次串扰会有所减小, 进而会减弱对传输线A的串扰, 所以当频率较高时, 在第2条传输线对受扰线远端串扰上, 文献[15]方法会比未使用任何抑制串扰方法有所降低.

在高速电路中, 由于可能存在着多条耦合微带线的情况, 那么在任意两条相邻微带传输线(干扰线与受扰线)中, 本文方法与文献[15]方法都符合串扰相位抵消的原则, 所以这2种方法在抑制每边第一条相邻传输线对受扰线串扰的效果相同.基于此, 这两种方法在抑制每边第2条相邻传输线对受扰线的串扰更具有可比性, 上述仿真对比结果验证了本文方法更具有优势.

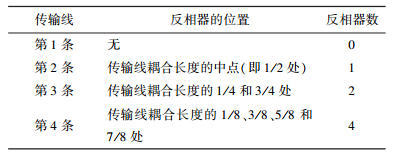

如果在实际应用时, 当总线中线间距继续减小需要考虑受扰线每边第3条相邻传输线对受扰线的串扰时, 可以把本文方法进一步改进, 此时反相器插入的位置和数量如表 1所示.可以以这种方式继续增加反相器来抑制更多条传输线对受扰线的串扰.但需要注意的是, 随着反相器数的增加, 系统的复杂度和代价必然提升, 这需要在效果和代价之间进行平衡.

|

|

表 1 反相器的位置和数量 |

提出了一种抑制多条耦合微带线间串扰的电路结构, 该电路结构利用反相器组合可以抑制每边第2条传输线对受扰线的串扰.由于该结构保证了电路系统中任意两条平行相邻微带线间的串扰抵消原则, 所以该方法能够抑制受扰线每边两条相邻传输线的串扰.同时, 所提出电路结构中反相器数不会增加太多.在3条传输线情况下, 图 3方法和图 4方法中的反相器数一致.如果增加微带线的数量使之为n, 那么图 3方法反相器数为n(n>3且n为偶数)或n+1(n>3且n为奇数), 图 4方法反相器的平均数为n+2(n>3且n为偶数)或n+1(n>3且n为奇数), 比较可以看出, 反相器数基本没有大的变化.结合仿真结果可以说明, 在电路复杂度和代价基本一致的情况下, 采用本文方法能更好地抑制多条平行耦合微带传输线间的远端串扰, 这可以为高速电路设计者提供技术选项, 使高速电路的误判决和误码率等指标显著下降.

| [1] | Gravelle L B, Wilson P F. EMI/EMC in printed circuit boards-a literature review[J].IEEE Transactions on Electromagn Compatibility, 1992, 34(4): 109–116. |

| [2] | Hall S H, Hall G W, McCall J A. 高速数字系统设计: 互连理论和设计实践手册[M]. 伍微, 译. 北京: 机械工业出版社, 2004: 29-46. |

| [3] | Bogatin E. 信号完整性分析[M]. 李玉山, 等译. 北京: 电子工业出版社, 2005: 239-240, 338-339. |

| [4] | Lee K, Lee H B, Jung H K, et al. A serpentine guard trace to reduce the far-end crosstalk voltage and the crosstalk induced timing jitter of parallel microstrip lines[J].IEEE Transactions on Advanced Packaging, 2008, 31(4): 809–817. doi: 10.1109/TADVP.2008.924226 |

| [5] | Choi U, Kim Y J, Kim Y S. Crosstalk reduction in printed circuit boards using irregularly-spaced vias in a guard trace over a slotted ground plane[C]//European Conference on Circuit Theory and Design. Antalya: IEEE Press, 2009: 794-797. |

| [6] | Mallahzadeh A R, Ghasemi A H, Akhlaghi S, et al. Crosstalk reduction using step shaped transmission line[J].Progress In Electromagnetics Research C, 2010, 12(2010): 139–148. |

| [7] |

安静, 武俊峰, 吴一辉. 使用防护带抑制微带线间串扰的研究[J]. 北京理工大学学报, 2011, 31(3): 343–347.

An Jing, Wu Junfeng, Wu Yihui. Research of suppressing crosstalk of the microstrip lines by using stripe protection[J].Journal of Beijing Institute of Technology, 2011, 31(3): 343–347. |

| [8] | Wu B P, Mo T T. Barbed transmission lines for crosstalk suppression[C]//Asia-Pacific Symposium on Electromagnetic Compatibility. Sentosa: IEEE Press, 2012: 621-624. |

| [9] | Takbiri M, Masoumi N, Mehri M, et al. Crosstalk reduction using open-loop resonators for printed circuit boards traces [C]//13th Mediterranean Microwave Symposium (MMS). Saida: IEEE Press, 2013: 1-4. |

| [10] | Broyde F, Clavelier E. A new method for the reduction of crosstalk and echo in muhiconductor interconnections[J].IEEE Transactions on Circuits and Systems, 2005, 52(2): 405–416. doi: 10.1109/TCSI.2004.841596 |

| [11] | Ciamulski T. Coupling compensation concept applied to crosstalk cancelling in multiconductor transmission lines[J].IEEE Transactions on Electromagnetic Compatibility, 2008, 50(2): 437–441. doi: 10.1109/TEMC.2008.921025 |

| [12] |

王亚飞, 陈迎潮, 杨曙辉, 等. 利用微分电路减小PCB上串扰的方法[J]. 华南理工大学学报(自然科学版), 2012, 40(8): 20–25.

Wang Yafei, Chen Yinchao, Yang Shuhui, et al. Method using derivative circuit to reduce crosstalk between transmission lines in PCB[J].Journal of South China University of Technology(Natural Science Edition), 2012, 40(8): 20–25. |

| [13] | Lin Y, Liu S. 4-Gb/s Parallel receivers with adaptive far-end crosstalk cancellation[J].IEEE Transactions on Circuits and Systems-Ⅱ: Express Briefs, 2013, 60(5): 252–256. doi: 10.1109/TCSII.2013.2251957 |

| [14] | Oh T, Harjani R. A 12-Gb/s multichannel I/O using MIMO crosstalk cancellation and signal reutilization in 65-nm CMOS[J].IEEE Journal of Solid-State Circuits, 2013, 48(6): 1383–1307. doi: 10.1109/JSSC.2013.2252517 |

| [15] |

王亚飞, 杨鸿文, 李学华. 基于串扰与干扰源相位同步的减小串扰研究[J]. 电波科学学报, 2012, 27(3): 470–475.

Wang Yafei, Yang Hongwen, Li Xuehua. Crosstalk-reduction based on phase synchronization between crosstalk and interference source signal[J].Chinese Journal of Radio Science, 2012, 27(3): 470–475. |