在磁共振成像(Magnetic Resonance Imaging,MRI)系统中,谱仪部分作为其核心部件负责产生成像序列、射频脉冲和梯度信号,以及接收磁共振回波信号.其中磁共振信号接收系统的灵敏度、噪声系数、动态范围,以及互调干扰抑制等指标直接影响磁共振信号的接收质量,从而影响成像质量.因此磁共振信号接收系统的设计对于MRI系统来说非常关键.

在早期的MRI系统中,由于数字系统运算能力的限制,对磁共振信号只能采取模拟正交检波的方法分离信号的实部和虚部[1].这种做法的缺点是正交检波所用的本振信号由于模拟器件的差异性和不稳定性无法做到完全正交和同等大小,所以在模拟正交检波后会产生镜像峰和零频峰,进而在图像上出现伪影.近几年伴随着半导体技术的发展,有些半导体厂商推出了高速数字接收信号处理器,其包含了数字正交检波和可编程数字滤波器,避免了模拟正交检波的缺点,但是由于其各级数字滤波器结构和阶数较固定,且开发周期长,因此不是MRI应用中的最佳选择.

本文提出了基于全可编程片上系统(System-on-a-Chip,SoC)和实验室虚拟仪器工程平台(Laboratory Virtual Instrument Engineering Workbench,LabVIEW)的MRI接收系统的设计,硬件设计平台采用Xilinx公司全可编程SoC芯片ZYNQ-7000系列.该系列全可编程SoC片内集成了丰富的可编程逻辑(Programmable Logic)资源和高性能中央处理单元(Central Processing Unit,CPU),其中可编程逻辑部分主要包括了数字信号处理(Digital Signal Processing,DSP)单元、查找表(Lookup Table,LUT)和随机存储器块(Random Access Memory Block,Block RAM)等.LabVIEW是美国国家仪器公司(National Instruments Corp.)推出的一种基于图形化编程语言方式的创新软件产品[2],其图形化的编程方式使得软件开发周期更短.本文提出的MRI接收系统充分利用Xilinx全可编程SoC的优势,利用可编程逻辑部分实现磁共振信号的正交检波、抽取滤波、通用串行总线(Universal Serial Bus,USB)通信和存储等功能,利用处理器部分控制信号预处理部分增益和中频频率等.PC(Personal Computer)端上位机软件采用LabVIEW编写,实现与SoC的USB通信,以及磁共振信号的显示和储存.

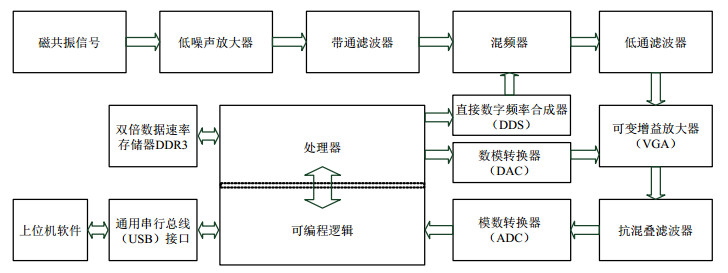

1 系统结构本接收系统主要分为三部分,包括磁共振信号预处理部分、Xilinx ZYNQ全可编程SoC部分和上位机部分,系统结构框图如图 1所示.

|

图 1 系统结构框图 Figure 1 Block diagram of system structure |

磁共振信号预处理部分主要负责对磁共振线圈接收的磁共振信号进行放大和滤除相邻频带的干扰信号,并对其进行下变频至中频,再使用可变增益放大器(Variable Gain Amplifier,VGA)对中频信号进行适当放大后送入高速模数转换器(Analog-Digital Converter,ADC)进行数字化.

SoC部分包括处理器部分和可编程逻辑部分,处理器部分主要负责三方面工作:第一是控制直接数字频率合成器(Direct Digital Synthesizer,DDS)产生下变频所用的本振信号;第二是控制VGA对中频信号进行适当增益;第三是协同可编程逻辑将数字化后的磁共振信号存储到双倍数据速率(Double Data Rate,DDR)存储器DDR3中;可编程逻辑部分负责读写DDR3中数字化的磁共振信号数据,以及对磁共振信号进行正交检波和抽取滤波,还负责实现同USB通信部分的时序接口.

上位机部分负责接收通过USB传输的磁共振数据和对信号进行显示和存储.

1.1 信号预处理部分设计信号预处理部分包括前置低噪声放大器、混频器、DDS、模拟滤波器、VGA和ADC.信号预处理部分对磁共振信号的处理过程如下:当上位机发出采集数据的命令后,信号由磁共振线圈接收,通过同轴线进入低噪声放大器,增益+20 dB,然后经带通滤波器滤除干扰信号.信号在混频器中与DDS产生的本振信号混频,经过滤波器得到下变频的中频信号.中频信号在VGA中进行程控放大,增益控制电压可以由SoC的处理器控制数模转换器(Digital-Analog Converter,DAC)产生.放大后的信号被高速ADC采集,并数字化传输到SoC部分.

前置低噪声放大器作为接收系统的第一级放大器,负责将磁共振线圈接收的微弱信号进行放大,由于接收的信号幅值很小,所以这一级放大器要求噪声系数尽量小,且增益要选取适当,为使得接收链路总噪声系数最小,第一级放大器噪声系数要尽可能小,且第一级增益要尽可能大[3].然而由于磁共振接收线圈接收的信号有可能存在相邻信道的干扰信号,增益过大有可能会造成放大器输出饱和.基于以上因素考虑,本接收系统前置低噪声放大器采用亚诺德半导体(Analog Device Inc.,ADI)低噪声放大器AD8099实现,AD8099是一款超低失真高速运算放大器,增益带宽积达到3.8 GHz,电压噪声仅为

混频器的作用是将磁共振信号下变频到中频,以便降低后级放大器带宽要求和ADC采样速率要求.可供选择的混频器器件分为两大类:有源混频器和无源混频器,由于有源混频器具有对本振信号的功率电平要求低,且混频后输出中频信号可以做到无衰减的优点,本接收系统选择亚诺德半导体的低失真有源混频器AD831实现.AD831具有500 MHz的射频和本振输入带宽,单端输出下中频输出频率范围为DC至200 MHz,且其本振信号输入驱动能力要求仅为-10 dBm,1 dB压缩点为10 dBm[5].因此AD831有带宽范围宽、本振要求低、信号失真小和输出无衰减的优点.混频器输入的本振信号来自SoC控制的DDS AD9851产生,中频频率选择3.31 MHz,混频后利用滤波器选择出中频信号.滤波器使用ADS设计的11阶LC低通滤波器.

在运行MRI序列时[6],接收到的磁共振信号有K空间中央行电平大、两端电平小的特点,所以通过VGA对接收不同电压值的信号进行适当放大,使ADC采集到的中频信号每次都是在不超过其可量化范围的较大值,从而提高接收机的动态范围[7].对于不同大小的磁共振信号需要不同的增益大小以最大限度的利用ADC的位数,减小量化噪声的影响.在对磁共振信号进行变增益接收后,需要在可编程逻辑部分利用DSP单元将放大后的K空间数据恢复为实际大小.本设计中所用VGA为亚诺德半导体的AD8331,AD8331是集成了前置放大器和可编程输入阻抗的超低噪声VGA,其3 dB带宽为120 MHz,控制电压为0~1 V,可控增益动态范围为48 dB[8].AD8331的前置放大器固定增益19 dB,具有很好的噪声表现,其电压噪声仅为

高速ADC在模拟信号的数字化中起着关键性作用,其位数影响着接收机的动态范围、量化噪声影响着接收机的信噪比、采样速率决定着能否正确地将信号数字化,因此ADC的设计对于接收机至关重要.本设计选择德州仪器的ADC—ADS805实现中频信号的数字化.ADS805是一款12位最高采样率为20 MHz的ADC,其在输入信号9.8 MHz时无杂散动态范围为74 dB,信噪比为68 dB,且具有输入信号超出可量化范围的提醒[11],这在中频信号的可变增益时可以用来防止信号增益过大超出ADC量化范围的情况.且ADS80X系列是一系列引脚兼容而采样速率不同的ADC,这对于不同的接收系统设计可以大大缩短开发周期.本设计中在对磁共振信号采样过程中设置ADC采样速率为20 MHz.

对于磁共振接收机硬件设计来说,电源部分的设计也十分重要.若电源设计不合理,电源噪声会对磁共振信号产生串扰、调制等影响,所以在电源设计时要尽量降低电源噪声,并且注意数字电源与模拟电源的隔离.本文选择多片TPS7A3001(TI)和TPS7A4901(TI)这两款超低噪声线性稳压器实现多路正负电源的设计.TPS7A4901和TPS7A3001是专为对噪声敏感的模拟系统设计的线性稳压器,其输出噪声有效值均可低至微伏量级,电源抑制比达72 dB,其中TPS7A4901为正电源,最大输出电流为150 mA[12];TPS7A3001为负电源,最大输出电流为200 mA[13].多路正负电源的设计既保证了各部分电流充足,避免了线性稳压器输出过流造成电源纹波增大的风险;同时也使各电路电源相互隔离,减少了各级之间的影响.

1.2 全可编程SoC部分设计Xilinx公司的ZYNQ系列全可编程SoC芯片最大的特点就是在一块芯片中集成了擅长于并行处理的现场可编程门阵列(Field Programmable Gate Array,FPGA)部分和擅长于控制的ARM(Advanced RISC Machines)Cortex-A9内核,两部分通过高级可扩展接口(Advanced eXtensible Interface,AXI)进行高速通信.这样做的优势是十分明显的,内部AXI-4总线相对于传统FPGA加ARM的结构可以有效地减少通信延时,提高系统的工作速率;而且SoC芯片可以减小电路板面积,降低电路复杂度,以更少的原件成本获得更好的系统稳定性.本设计选用德致伦(Digilent)基于Xilinx ZYNQ AP SoC推出的ZYBO开发平台,板载512 MBx32BIT DDR3存储芯片,并且有6个Pmod接口可以向外扩展.本部分将分别对可编程逻辑部分和处理器部分的设计做详细描述.

1.2.1 可编程逻辑部分设计在本设计中,可编程逻辑主要完成的工作是对模数转换器数字化后的磁共振信号进行数字下变频(Digital Down Converter,DDC)、实现与上位机进行USB通信的接口时序以及与处理器部分通信以交换数据,其中DDC是该部分的设计核心内容.

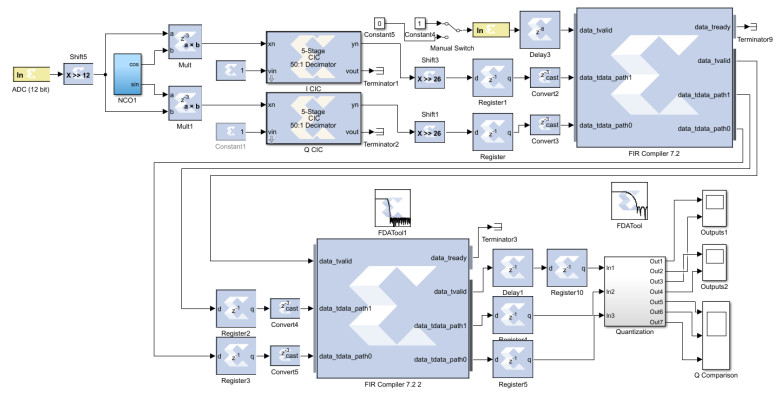

本设计采用了Xilinx公司提供的System Generator设计DDC IP核.System Generator是由Xilinx公司开发的Matlab/Simulink环境下一个工具箱,用来在以FPGA为核心器件设计信号处理系统时建立抽象算法,并且可以将抽象算法转化为可靠的硬件实现[14].工具箱中包含了大量的常用的数字信号处理模块,可以通过可视化编程的方式来设计我们需要的数字信号处理算法,这降低了算法开发难度,而且大大缩短了信号处理算法的开发周期.在本设计中利用System Generator搭建的DDC算法如图 2所示.

|

图 2 数字下变频算法模型 Figure 2 Algorithmic model of DDC |

左侧输入端口输入使用MATLAB/Simulink产生的仿真信号,经过移位操作将信号缩小4 096倍;然后将信号分为2路,分别通过乘法器同数控振荡器(Numerically Controlled Oscillator,NCO)产生的正交信号做数字混频,混频后得到基波信号.此处NCO的作用是通过查表法输出两路正交的数字本振信号.由于基波信号是一个低频信号,而当前信号采样率还是ADC的采样率,基波信号不需要这么高的采样速率,所以接下来要进行数据抽取滤波以降低信号的采样速率.

本设计中抽取滤波采用级联积分-梳状(Cascade Integration-Comb,CIC)滤波器、半带(Half Band,HB)滤波器和有限长单位冲击响应(Finite Impulse Response,FIR)滤波器实现.由于CIC滤波器运算中不需要乘法操作,所以其可以工作在采样速率较高的情况下[15],我们先用5级CIC滤波器将基波信号作50倍抽取滤波.ADC采样速率为20 MHz,经过50倍抽取后信号采样速率降低为400 kHz.本设计抽取的第二级采用HB滤波器将CIC滤波器抽取后的数据做两倍抽取,HB滤波器使用Xilinx提供的FIR Compiler7.2以及Matlab中的FDATool实现,设计采样速率为400 kHz,通带为80 kHz.HB滤波器由于一半的系数为0,而且其系数对称,其实现所需要的逻辑资源远小于普通FIR滤波器,但其每一级仅能做两倍抽取滤波,如果需要高倍率的抽取需要将多级HB滤波器级联实现[16].最后一级抽取滤波器需要提供足够大的带外抑制和足够窄的过渡带,由于考虑到在FPGA上实现,还需要控制滤波器的阶数以减少逻辑资源的消耗.本设计选择等纹波FIR滤波器实现,FDATool中设计采样速率为200 kHz,通带为30 kHz,过渡带为10 kHz,带外抑制为80 dB,带内纹波为0.01 dB.经过以上三级抽取滤波后信号实现了200倍抽取,最终采样速率由ADC的20 MHz降低为100 kHz,抽取滤波后信号经过Quantization子系统截断量化后输出并存储在板上的DDR3.

可编程逻辑部分最终在ZYBO开发板上实现后逻辑资源使用情况如表 1所示,由表中资源使用情况可知,本设计中各种逻辑资源还有较多余量,这有利于后续的系统算法开发和升级.

| 表 1 可编程逻辑资源利用列表 Table 1 Utilization of programmable logic resource |

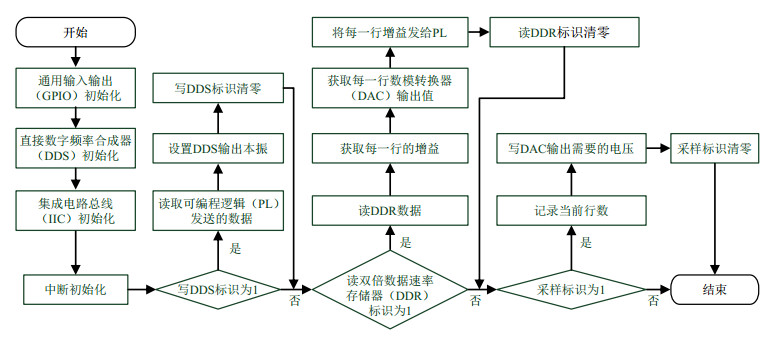

ZYBO开发平台采用的XC7Z010-1CLG400C全可编程SoC片内集成两个ARM Cortex-A9高速处理器硬核,运行时钟高达667 MHz,运算能力完全满足本设计的需求.在本设计中处理器部分主要负责对DDS和DAC的控制,用来产生混频器的本振信号和VGA的控制电压.单次采样的处理器部分软件流程图如图 3所示.

|

图 3 单次采样的处理器程序设计流程图 Figure 3 Software flow chart of single sampling |

处理器部分的工作过程如下:处理器先对通用输入输出(General Purpose Input/Output,GPIO)、DDS和DAC的集成电路总线(Inter-Integrated Circuit,IIC)接口进行初始化,完成初始化后就进入等待中断状态.可编程逻辑部分通过三个可编程逻辑-处理器(Programmable Logic-Processing System,PL-PS)中断中断处理器:1号中断用来通知处理器配置DDS产生本振信号,当用户在上位机端完成本振频率设置,上位机将数据通过USB传输到PL部分,PL部分产生1号中断并将数据发送到处理器,处理器响应中断并读取数据,设置DDS输出频率;2号中断用来通知处理器读取预采样数据,当PL部分完成磁共振信号的预采样后在处理器产生一个中断,处理器响应中断并读取PL存储在DDR3的每一行预采样数据,之后完成数据的处理,得到每一行需要的增益以及对应的增益控制电压(VG);3号中断用来通知处理器采样开始,处理器响应中断并通过IIC控制DAC输出当前采样序列需要的VG.

其中,处理器获取VG控制码表的过程如下:当接收机工作在预采样模式下,采样触发信号会触发PL部分读取ADC的并行输出数据,在得到数字化的磁共振数据后通过AXI总线将数据存储在DDR3存储器中.其中采样触发信号来自于实验用磁共振仪器工控机的脉冲序列控制板卡,其作用是控制接收机采样开始时间以保证每次采样的相位相同.在预采样结束后,PL部分通知处理器存储数据已完成,可以进行读取.处理器部分读取存储在DDR3中的磁共振信号,并根据ADC的可量化范围计算出每一行信号的VG,然后计算出DAC的控制字存储在数组中.

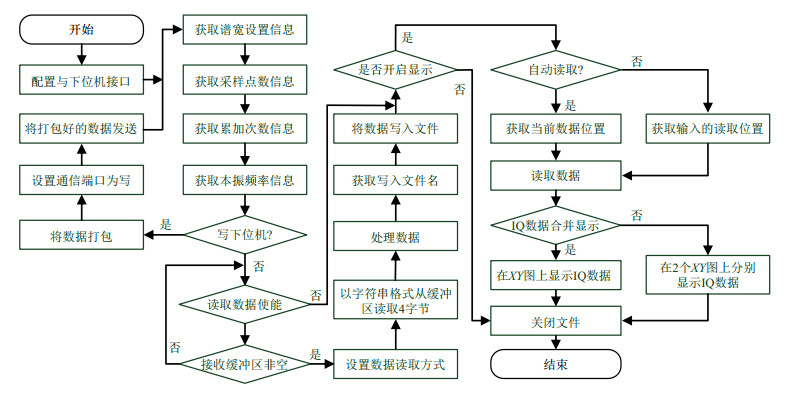

1.3 上位机部分设计在本设计中磁共振上位机软件利用LabVIEW软件完成,目前利用LabVIEW设计磁共振系统上位机软件的案例还较少,本设计验证了利用LabVIEW可以提高磁共振系统上位机软件的开发效率.本设计中上位机软件程序设计框图如图 4所示.

|

图 4 上位机软件程序设计流程图 Figure 4 Design flow chart of PC software program |

LabVIEW采用图像化编程G语言编程,程序运行方式为数据流驱动的方式运行.本设计上位机程序运行首先配置与下位机的通信接口,下位机USB通信接口芯片选用FT245RL,通信接口驱动程序采用英商飞特帝亚(Future Technology Devices International Ltd.,FTDI)提供的虚拟串口驱动程序.该驱动程序可以将FT245RL发送的USB数据流封装成串口的形式,这样在上位机的编程中直接操作串口就实现了对USB数据的读写,利用虚拟串口驱动可以实现300 kb/s的数据读写[17].

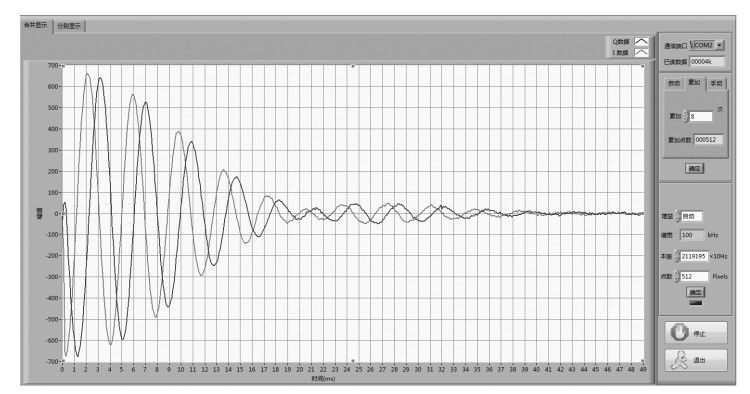

上位机通过数据输入控件输入设置参数,设置的参数包括接收谱宽、采样点数、累加次数和本振频率等,通过布尔按键触发写下位机操作将参数传输到ZYBO平台.当上位机接收到ZYBO平台发送的磁共振数据,上位机先判断读取数据按键是否使能,若读使能,将接收到的十六进制数据转为I和Q两路十进制有符号数,然后根据设置的读取点数将数据写入文件存储,上位机会为每一个采样序列生成一个存储数据的文本文档.若数据显示按键按下,上位机会在读取数据后将数据显示出来,数据可以选择实时显示读取到的数据或浏览历史数据.数据显示利用XY图控件实现,X轴为数据的时间信息,Y轴为数据幅度信息.在显示数据时,可以选择将I和Q两组数据在同一个XY图显示或者分别用一个XY图显示.利用LabVIEW设计的磁共振接收系统上位机软件界面如图 5所示.

|

图 5 上位机软件界面 Figure 5 PC software interface |

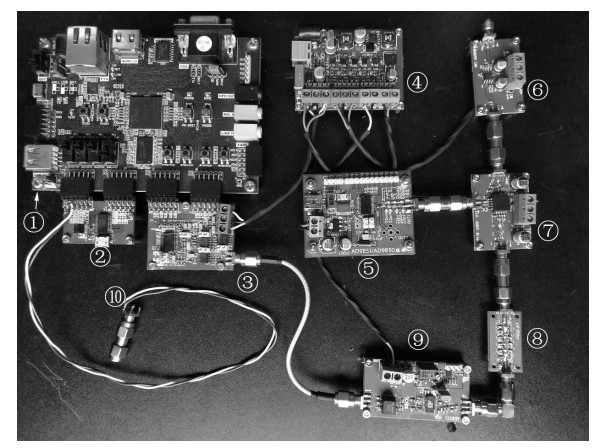

为了验证本文设计的接收机采集效果,用本接收机替换实验室0.5 T MRI仪器原接收机,并用本文设计的上位机软件显示接收的自由感应衰减(Free Induction Decay,FID)信号波形信息.本接收机替换原接收机的具体方式为:将MRI仪器射频机箱的信号输出利用同轴线连接到本文接收机低噪声放大器的输入接口,将MRI仪器工控机机箱中接收机采样触发信号通过同轴线连接到本文接收机采样触发的输入端口,将本文接收机通过USB连接到运行上位机程序的PC.由于本文仅设计了接收机部分,所以在本实验中发射机依然由原上位机控制,利用MRI仪器的采样触发信号来触发本文接收机进行采样从而保证每次采样的相位相同.本文选用实验室标准样品油作为被测对象,分别用单脉冲序列和硬脉冲CPMG(Carr-Purcell-Meiboom-Gill)序列进行试验,实验测得共振频率为21.194 950 MHz.本文设计的接收机硬件实物图如图 6所示,1号板为ZYNQ系统板,2号板为USB接口电路,3号板为ADC,4号板为低噪声电源板,5号板为DDS,6号板为低噪声放大器,7号板为混频器,8号板为滤波器,9号板为VGA,10号为连接外部采样触发信号的接口.

|

图 6 接收机硬件. ①ZYNQ系统板;②USB接口;③模数转换器;④低噪声线性稳压器;⑤直接数字频率合成器;⑥低噪声放大器;⑦混频器;⑧滤波器;⑨可变增益放大器;⑩触发接口 Figure 6 The hardware of receiver. ①ZYNQ Board; ②USB Interface; ③Analog-Digital Converter; ④Ultralow-Noise Linear Regulator; ⑤Direct Digital Synthesizer; ⑥Low Noise Amplifier; ⑦Mixer; ⑧Filter; ⑨Variable Gain Amplifier; ⑩Trigger Interface |

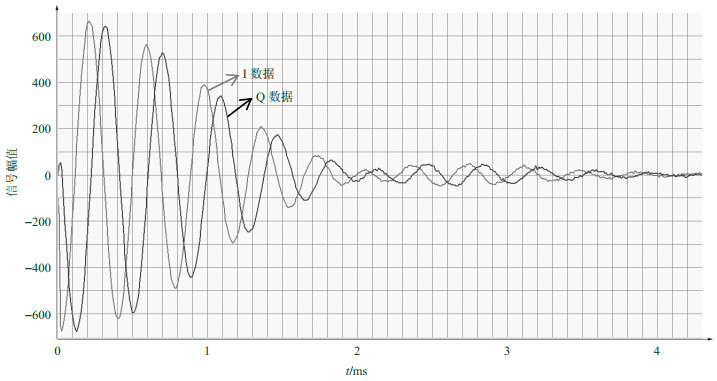

在选用硬脉冲单脉冲序列进行实验时,设置接收机检波频率为21.191 950 MHz,即偏共振3 kHz;设置采样点数为512,采样频率为100 kHz,即采样时间为5.12 ms;90˚射频脉冲施加时间P1为17 μs,脉冲施加强度为100%;重复时间D0为1 000 ms,累加次数NS设置为8.上位机接收信号进行8次累加后结果如图 7所示,其中横坐标为采样时间,每一格代表 100 μs,纵坐标为量化后的信号幅值.

|

图 7 单脉冲序列实验所得信号 Figure 7 The waveform of FID using single pulse sequence |

由上位机显示的硬脉冲单脉冲序列下的所得信号可以看出,接收机接收的信号为FID信号,其中浅色曲线为实部信号,深色曲线为虚部信号,实部信号较虚部信号领先90˚.接收机没有出现饱和的情况,且接收机信噪比较原接收机有所提高,这主要得益于本文接收机采用的低噪声放大器和低失真混频器为信号预处理链路,降低了噪声的引入,以及电源部分采用超低噪声线性稳压器极大地减少了电源部分对磁共振信号的串扰.另外,集成化的设计也有助于抑制噪声.

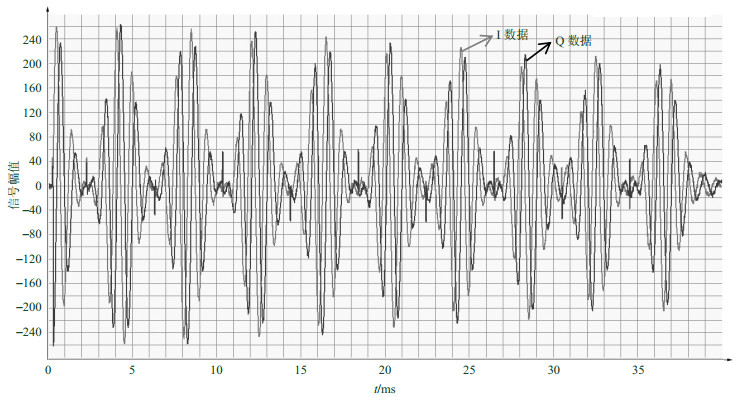

硬脉冲CPMG序列是在自旋回波序列基础上,多次施加180˚脉冲,从而可以得到多个回波信号的回波脉冲序列.本文在进行硬脉冲CPMG序列时设置参数情况如下:接收机检波频率21.193 450 MHz,即偏共振1.5 kHz;采样点数设置为4 000,采样频率设置为100 kHz,即采样时间为40 ms;90˚脉冲施加时间P1设置为17 μs,180˚脉冲施加时间设置为30 μs,脉冲施加强度均为100%;脉冲序列重复时间D0设置为1 000 ms,90˚脉冲与180˚脉冲之间的时间间隔D1设置为1 ms,180˚脉冲之间的时间间隔D2设置为2 ms;回波信号个数C1设置为9,累加次数NS设置为4,上位机接收信号进行4次累加后结果如图 8所示,其中横坐标为时间,每一格代表 1 ms,纵坐标为量化后的信号幅值.

|

图 8 CPMG序列实验所得信号 Figure 8 The waveform of CPMG sequence experiment |

由上位机显示的硬脉冲CPMG序列下的磁共振回波信号可以看出,在施加一个90˚脉冲后,连续对样品施加9次180˚脉冲,得到9个回波信号,回波信号的幅度逐渐减小.

3 结论本文提出了一种基于全可编程SoC和LabVIEW的磁共振信号接收系统的设计.本设计选用最新的全可编程SoC作为接收机主芯片,使用Matlab平台Simulink工具对DDC算法进行设计、仿真和优化.并利用Xilinx提供的System Generator工具设计DDC算法IP核.本设计选用高速ADC、低噪声放大器、低失真混频器、VGA、DDS以及超低噪声线性稳压器等设计了一套完整的磁共振接收机硬件系统.基于图形化编程平台LabVIEW编写磁共振上位机软件,完成了磁共振信号从接收机到PC端的传输、PC端对接收机参数的设置、磁共振信号的显示以及存储功能,使用LabVIEW开发磁共振上位机降低了上位机的开发难度,缩短了上位机设计时间,且设计的界面美观实用.通过实验表明本文设计的磁共振接收系统能正确获得磁共振信号,且具有较高的信噪比.

| [1] |

REN J J, XU Q, LI G Y. A digital receiver for nuclear magnetic resonance spectrometer[J].

Chinese J Magn Reson, 2007, 24(1): 27-33.

任洁静, 徐勤, 李鲠颖. 一体化核磁共振数字接收机设计[J]. 波谱学杂志, 2007, 24(1): 27-33. DOI: 10.3969/j.issn.1000-4556.2007.01.004. |

| [2] | 周鹏, 许钢. 精通LabVIEW信号处理[M]. 北京: 清华大学出版社, 2013. |

| [3] | 高瑜翔主编.高频电子线路[M].北京: 科学出版社, 2008. |

| [4] | AD8099 datasheet[EB]. Analog Devices, 2016. |

| [5] | AD831 datasheet[EB]. Analog Devices, 2003. |

| [6] |

HU Z Q, JIN T, ZHANG X M. Receiving MRI echo with software-defined radio approach[J].

Chinese J Magn Reson, 2013, 30(1): 29-39.

胡曾千, 金涛, 章新明. 用软件无线电方法实现MRI回波信号接收[J]. 波谱学杂志, 2013, 30(1): 29-39. DOI: 10.3969/j.issn.1000-4556.2013.01.004. |

| [7] |

LIU Y, ZHANG Y W, LIANG Z, et al. A heterogeneous dual-core receiver system for magnetic resonance applications[J].

Chinese J Magn Reson, 2017, 34(1): 100-107.

刘颖, 张育文, 梁浈, 等. 基于异构双核的磁共振接收机设计[J]. 波谱学杂志, 2017, 34(1): 100-107. |

| [8] | AD8331 datasheet[EB]. Analog Devices, 2010. |

| [9] | DAC101C08XX datasheet[EB]. TEXAS INSTRUMENTS, 2016. |

| [10] | LM4121 datasheet[EB]. TEXAS INSTRUMENTS, 2013. |

| [11] | ADS805 datasheet[EB]. TEXAS INSTRUMENTS, 2002. |

| [12] | TPS7A4901 datasheet[EB]. TEXAS INSTRUMENTS, 2015. |

| [13] | TPS7A3001 datasheet[EB]. TEXAS INSTRUMENTS, 2015. |

| [14] | 纪志成, 高春能. FPGA数字信号处理设计教程-System Generator入门与提高[M]. 西安: 西安电子科技大学出版社, 2008. |

| [15] |

HU J J, YAO J J, XU J C, et al. A magnetic resonance imaging receiver design based on NI PXIe-7966R[J].

Chinese J Magn Reson, 2017, 34(4): 489-497.

胡晋杰, 姚俊江, 徐俊成, 等. 基于NI PXIe-7966R的磁共振成像接收机设计[J]. 波谱学杂志, 2017, 34(4): 489-497. |

| [16] |

WANG H, SUN H Y, TANG W N, et al. An FPGA-based multi-chanel receiver module for magnetic resonance imaging[J].

Chinese J Magn Reson, 2012, 29(2): 239-247.

王洪, 孙宏宇, 汤伟男, 等. 基于单片FPGA的多通道磁共振成像接收模块[J]. 波谱学杂志, 2012, 29(2): 239-247. DOI: 10.3969/j.issn.1000-4556.2012.02.010. |

| [17] | FT245R datasheet[EB]. Future Technology Devices International Limited, 2010. |

2018, Vol. 35

2018, Vol. 35