2. 美国国家仪器有限公司(中国), 上海 201203

2. National Instruments Corporation(China), Shanghai 201203, China

在磁共振成像(MRI)系统中,信号接收链路需要将MRI模拟信号数字化,其数字化部分的设计方案和性能,直接影响磁共振图像质量.最初的接收机设计思路是首先进行模拟正交检波,然后再使用模数转换器(ADC)使模拟信号数字化,实部和虚部信号的任何不平衡都会引起误差,使磁共振图像产生伪影.为了解决这样的问题,通常采用数字接收机设计思想[1, 2],即磁共振信号首先进行模数转换,然后在数字域中实现正交检波和滤波抽取,以避免因正交接收通道的不平衡导致的鬼影和镜像信号.随着MRI系统的发展,数字接收机的设计方案正得到越来越广泛的应用[3-6].

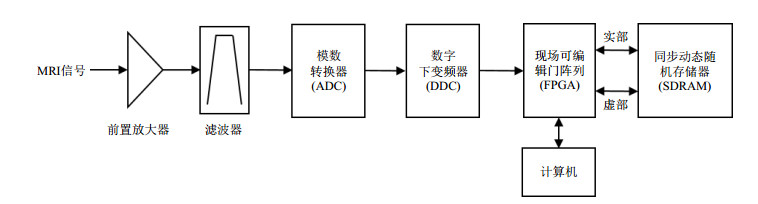

如图 1所示,现有的大部分数字接收机由前置放大器、抗混叠滤波器、ADC、数字下变频器(DDC)、现场可编程门阵列(FPGA)和内存等部分组成,输出实部和虚部信号.作为接收机的核心部分,DDC集成了数字正交检波和数字滤波抽取功能,通常由稳定性较高的商用下变频芯片实现.常用的商用数字下变频芯片有美国Analog Devices公司生产的AD6620、AD6636[7]等.但这样的专用数字处理芯片功能结构是固定的.例如AD6636的级联积分梳状(CIC)滤波器为固定5级级联,两级半带滤波器的系数都是固定的;有限脉冲响应(FIR)滤波器的最大阶数不能超过127阶,且抽头系数的位数也是不能改变的.但实际上,针对不同的MRI实验条件,应该灵活制定数字信号处理(DSP)方案.例如在CIC滤波器[8, 9]抽取倍数较小时,可以不对通带进行补偿,但抽取倍数较大时,需要在后一级设计补偿滤波器,而非固定某一种特定功能结构.

|

图 1 数字接收机整体结构框图 Figure 1 Block diagram of the digital receiver |

现在广泛使用的数字接收机中用到的FPGA也仅提供商用下变频芯片逻辑接口,然后将处理后的数据存到板上内存,主机通过外围器件互联(PCI)桥芯片从板上内存读取数据.而面向DSP功能的Virtex-5(Xilinx, Inc.,美国)[10]及更高系列的FPGA平台,可以提供的逻辑门高达数百万门,兼有串、并行工作方式,具有高集成度、高速和高可靠性等特点;而且可以灵活调用如直接数字频率合成器(DDS)和FIR滤波器等信号处理知识产权核(IP核),直接在FPGA内实现DDC功能,而不采用商用DDC芯片.这样既可以简化电路设计,也可以灵活配置下变频功能的各个参数,从而为不同的MRI实验定制DSP方案[11-16].

本文提出了一种基于NI PXIe-7966R(National Instruments Corporation,美国)的MRI接收机设计方法.以NI PXIe-7966R板载Virtex-5系列的SX95T FPGA为核心,控制磁共振信号高速采样,并完成DDC处理.下变频逻辑设计过程具有很好的灵活性和可编程性,可从单通道扩展至多通道.所采用的NI LabVIEW FPGA(National Instruments Corporation,美国)开发平台是一种图形化的高层次综合(HLS)设计工具,消除了开发FPGA逻辑时存在的开发难度大,仿真等待时间长等障碍,可以清晰的显示并行机制和数据流、仿真和验证FPGA功能,以及实现信号自动化编译.

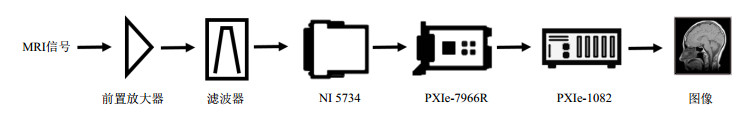

1 仪器设计 1.1 基于NI PXIe-7966R的MRI接收机的总体设计本文设计的接收机主要由信号采样模块、正交检波模块、下变频滤波器模块和数据上传模块等部分组成.硬件平台主要由NI 5734采样卡(National Instruments Corporation,美国)、PXIe-7966R和PXIe-1082机箱(National Instruments Corporation,美国)组成.

NI 5734采样卡可以提供4路同步采样,具有16位分辨率,并支持外部时钟、触发信号的输入,最高采样速度可达到120 MHz,完全满足磁共振信号模拟采样的要求.NI PXIe-7966R是NI 5734的FlexRIO模块,通过设计逻辑和算法,实现DSP(如DDC)功能.实验中,将50 MHz采样时钟通过NI 5734采样卡接入,将NI 5734插入NI PXIe-7966R的扩展输入输出(I/O)接口上,同步采样触发信号通过辅助I/O连接器(AUX I/O Connector)输入,在采样时钟和触发信号的控制下对磁共振信号进行采样,采样信号由板载FPGA中构建的DDC模块处理,所得到的基带数据通过面向仪器系统的PCI扩展总线(PXI)上传到PXIe-1082,进行快速傅里叶变换(FFT)和图像恢复等处理.具体流程如图 2所示.

|

图 2 数字接收机整体设计框图 Figure 2 Block diagram of the designed digital receiver |

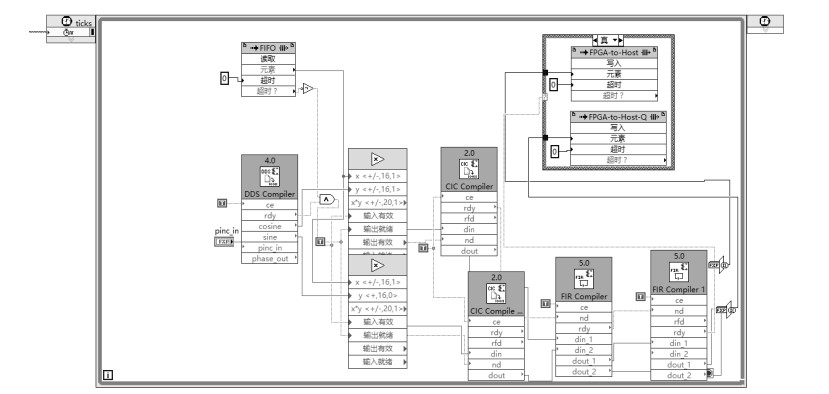

PXIe-7966R板载FPGA负责实现接收机的主要功能,即采样控制、信号的直接DDC处理,以及I路和Q路数据上传.首先使用DDS模块和高吞吐率乘法模块实现信号正交解调.解调后的信号由下变频滤波器进行滤波和抽取,在降低数据速率同时,滤除高频分量和带外信号.经抽取和滤波后,I路和Q路信号已降到较低速率(100 Hz~1 MHz),通过直接存储器存储(DMA)方式向主机传输基带数据.设计FPGA时,采用NI LabVIEW FPGA开发平台,对各模块进行了设计和仿真,并生成硬件描述语言(VHDL).图 3为利用NI LabVIEW FPGA设计的单通道接收机.

|

图 3 FPGA内部单通道功能框图 Figure 3 Functional block diagram of one receive channel inside the FPGA |

由NI 5734采样得到高速率数字信号后,数据流分别与DDS模块输出的I通道和Q通道数据做相乘运算,此过程为正交检波.检波处理后,磁共振信号由中频搬移至基带和高频处,随后高频分量被下变频滤波器滤除.为了发射机和接收机保持相位相干,首先必须保证接收机DDS模块输出的频率与发射机的频率完全相同,而且要保证发射机和接收机的时钟有相干性.被测谱仪系统中发射机的激发频率由DDS器件AD9854提供,其频率控制精度为48位、时钟频率为200 MHz,本文设计的接收机的DDS模块频率精度为32位、时钟频率为50 MHz,因此接收机DDS模块频率控制字A与发射机的频率控制字B应当满足以下关系式:

| $ A\times f_s/{{2}^{32}}=B\times f_c/{{2}^{48}} $ | (1) |

其中,接收机时钟频率(fs)为50 MHz,发射机时钟频率(fc)为200 MHz.接收机DDS模块使用的时钟与发射机时钟信号来自同一时钟源,并使用了根据以上关系式计算出的频率控制字,这样保证了发射机和接收机的相位相干.此外还通过加入相位抖动提高了无杂散动态范围(SFDR).

1.2.2 下变频滤波器模块设计经过正交检波后,信号被搬移到基带的同时产生了高频镜像分量,信号数据流速率与采样速率相同,需要进行降速处理.通过配置一系列滤波器,在滤除高频镜像分量的同时降低了信号的数据流速率.下变频滤波器模块由5级级联CIC滤波器和一系列FIR滤波器多级级联组成.在下变频滤波器的第1级采用了CIC滤波器,是因为CIC滤波器结构简单,没有乘法器,只有累加器、积分器和寄存器,非常适合在高采样率的条件下工作.设计中采用了5级级联的CIC滤波器,具有很好的阻带衰减作用.由于使用CIC滤波器对正交检波后的信号进行了抽取,数据流速率大大降低,因此后续的滤波器设计采用了滤波效果比较好、但是资源开销比较大的FIR滤波器进行级联设计.在分析CIC滤波器的幅频响应后,如果信号通带高频处的衰减较大,FIR滤波器组应首先设计CIC补偿滤波器使通带尽量平坦.最末1级的FIR滤波器为低通滤波器,对信号进行最后的滤波和抽取.此级滤波器对图像质量影响很大,需要满足过渡带陡峭、阻带衰减大的要求.采用最佳一致逼近法[17]设计的低通滤波器可以在最小的资源开销下满足滤波要求.由于不受到商用下变频芯片功能结构固定的限制,设计下变频滤波器模块时比较灵活,例如通过增加滤波器阶数的方式优化滤波效果、灵活决定是否旁路CIC补偿滤波器.设计下变频滤波器模块时通过NI LabVIEW FPGA设计平台调用CIC和FIR滤波器等IP核实现滤波器设计、仿真,开发难度大大降低.

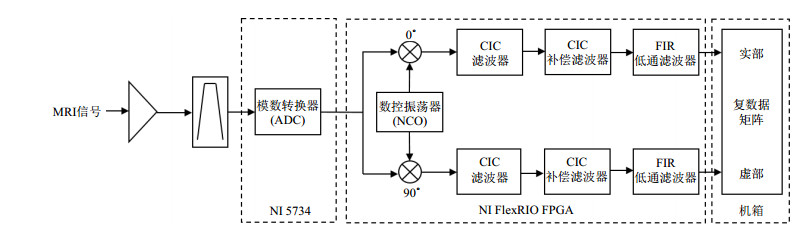

1.2.3 接收机设计针对不同的接收带宽,我们设计了不同组合的下变频滤波器模块.以采样间隔为50 μs、带宽为20 kHz的下变频滤波器设计为例,其接收机功能结构如图 4所示.

|

图 4 20 kHz带宽接收机的FPGA数字下变频功能结构 Figure 4 Functional block diagram of DDC inside the FPGA with the receiver bandwidth of 20 kHz |

接收机采样速率为50 MHz,ADC位数为16位,I路和Q路数据流上传带宽均为20 kHz.根据信噪比(单位为dB)计算公式:

| $ SNR=6.02n+1.76+10\text{lg}(f_s/2B) $ | (2) |

(2) 式中,n为ADC位数,fs为采样频率,B为模拟信号带宽,第3项为处理增益.经过计算,信号经过高速采样和正交检波处理后已具有139 dB的信噪比,有效转换位数为22位.为了适合不同带宽的分辨率要求和方便数据上传,将上传数据量化到24位,这就要求滤波器的阻带增益(单位为dB)小于20lg[(1/(224-1)],即-144.49.为了使数据流速率下降至20 kHz,需要2 500(50 MHz/20 kHz)倍抽取.采用了625×2×2的抽取策略,其中5级级联CIC滤波器抽取625倍.分析CIC滤波器的幅频响应,如图 5(a)中CIC滤波器在通带内的衰减曲线,10 kHz的通带之内,5级级联CIC滤波器已衰减约1 dB,因此在后级的FIR滤波器设计中对此衰减加以补偿.

|

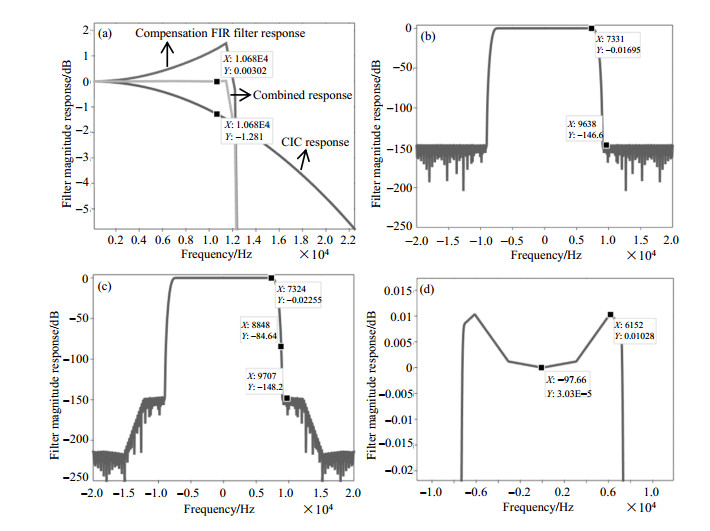

图 5 下变频滤波器组幅频响应曲线. (a) CIC和补偿滤波器幅频响应;(b)低通滤波器幅频响应曲线;(c)带宽为20 kHz的接收带宽内幅频响应曲线;(d)图(c)的通带放大 Figure 5 (a) Amplitude frequency response of the CIC and CIC compensation filter; (b)Amplitude frequency response of the low-pass filter; (c) Amplitude frequency response curve of decimating filter chain with bandwidth of 20 kHz; (d) The enlarged view of the passband in(c) |

为了提高通带内的平坦度,针对CIC滤波器在通带内的衰减曲线,设计了CIC补偿滤波器,使其频响特性与CIC滤波器在通带内的衰减特性相反.为了折中后续滤波器的通带设计需求,补偿滤波器补偿通带至12.5 kHz,滤波器阶数为189阶,设计的补偿滤波器补偿效果如图 5(a)所示.图 5(a)分别为针对CIC滤波器衰减曲线设计的补偿滤波器幅频响应曲线,以及CIC滤波器和补偿滤波器的综合幅频响应曲线,可以看出在通带内平坦度较好.

末级的低通滤波器需要在尽量少的阶数下提供尽量大的带外抑制,利用最佳一致逼近法设计的低通FIR滤波器,阶数为149阶,幅频响应曲线如图 5(b)所示.

针对20 kHz上传带宽设计的下变频滤波器具体由5级级联CIC滤波器、189阶的CIC补偿滤波器、149阶的低通滤波器组成,从综合幅频响应曲线[15][如图 5(c)]可以看出,阻带截止特性达到了145 dB,通带纹波为0.01 dB [如图 5(d)].由于补偿滤波器对通带的补偿,在-7.3~7.3 kHz的通带范围内,具有较好的通带平坦度,这样的下变频滤波器可以满足要求.理论上20 kHz的上传带宽可提供-10~10 kHz的通带范围,本设计中牺牲了一部分通带范围保证了充分的带外抑制.

2 结果与讨论为了检验所设计接收机的功能,将实验分为两个部分:首先,使用设计好的接收机对中心频率附近10 kHz谱宽范围的不同单频信号进行测量,用以检验触发信号控制采样功能和下变频滤波器的滤波性能;然后再进行MRI实验,恢复磁共振图像.

2.1 滤波器性能测试单频信号测量时,使用了两个函数发生器(Agilent 33250A).将函数发生器a的时钟输出端口与b的时钟输入端口连接,这样能保证两个函数发生器的时钟相干.函数发生器a采用突发模式,每秒进行一次信号输出,每次连续输出107个单频正弦信号作为被采样信号,且每次发出信号的初相位均为0、强度约为13 dBm.在单频信号开始输出的同时同步输出一个晶体管-晶体管逻辑(TTL)电平作为采样触发信号.函数发生器b固定输出50 MHz时钟信号作为采样时钟.触发信号通过NI 5734采样卡的辅助I/O连接器输入,采样时钟连接到采样卡的外部时钟输入端口.接收机每秒钟收到一个触发信号开始采样,在采样到达预设数量后停止采样并等待下一个触发信号.由于两个函数发生器的时钟是同步的,这样每次采样到的信号都具有相同的初相位,方便后续谱图的恢复.

函数发生器a分别生成22.001 MHz、22.002 MHz、22.007 3 MHz和22.008 8 MHz的单频正弦信号,这些信号位于以22 MHz为中心,距中心频率偏移分别为+1 kHz、+2 kHz、+7.3 kHz、+8.8 kHz的位置.使用本接收机分别采样并处理这些单频信号,并设正交检波模块的参考频率为22 MHz,对上传主机的信号进行频谱恢复.

从频谱图 6中可以看出,通带以内中心频率附近1 kHz、2 kHz、7.3 kHz的单频信号谱线被恢复出来.位于中心频率附近8.8 kHz的信号,由于其位于所设计下变频滤波器的通带以外,受到了明显的抑制.这样的结果与所设计的下变频滤波器的滤波性能是吻合的.通过对频谱结果的分析,可见本接收机的下变频滤波器,对通带内信号几乎没有衰减,而对通带外信号可以实现有效的抑制.

|

图 6 带宽为20 kHz下的单频测试频谱. (a) 22.001 MHz输入;(b) 22.002 MHz输入;(c) 22.007 3 MHz输入;(d) 22.008 8 MHz输入 Figure 6 Filter performance with bandwidth of 20 kHz. (a) 22.001 MHz input; (b) 22.002 MHz input; (c) 22.007 3 MHz input; (d) 22.008 8 MHz input |

另外,谱图中的轴峰(中心峰)是由于采样卡采用了直流耦合方式,采样到了信号发生器发出的微小直流分量造成的.若采用交流耦合方式,就可以避免轴峰产生.

以上实验验证了所设计接收机的信号采样、滤波抽取、数据上传等功能.

2.2 MRI实验接着进行了常规MRI实验.以上海市磁共振重点实验室研制的Dispect谱仪为平台,用本文设计的接收机取代其中一路接收机进行实验.

实验中,Dispect谱仪产生50 MHz采样时钟,接入NI 5734采样卡的外部时钟输入通道.同步采样触发信号,由谱仪的序列控制器产生,并接入采样卡的辅助I/O端口.每一次相位编码,Dispect谱仪的序列控制器就会发出一个同步触发信号.本文设计的接收机,每次接收到触发信号后开始采样、处理并上传磁共振信号,采样到达预设的数量后停止采样并等待下一个触发信号.每次上传的数据填充k空间的一列,序列运行完毕时k空间也填充完毕.然后处理采样到的信号并恢复图像.

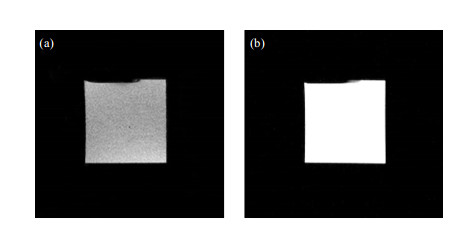

实验使用单片SE-2D序列对一个正方形水模成像(图 7).实验条件如下:磁场强度为0.3 T,谱宽为20 kHz,视野(FOV)为26 cm×26 cm,频率编码数为224,相位编码数为160,激发层厚为8 mm,层数为1,累加次数为1,利用本接收机采样多通道线圈的一个通道信号,同时使用Dispect谱仪接收机采样其它通道信号.图 7(a)为Dispect谱仪接收机恢复的水模图像,图 7(b)为本接收机所恢复水模图像.

|

图 7 (a) 使用Dispect谱仪自带接收机恢复的SE-2D水模图像;(b)使用本文接收机恢复的SE-2D水模图像 Figure 7 SE-2D image derived using the receiver included in Dispect spectrometer (a) and the design proposal (b) |

分析两幅图像的信噪比(SNR = Cr×S/SD,其中S为中心区域信号均值,SD为边缘各区域信号方差的均值,Cr ≈ 0.655)[20, 21],发现使用本接收机得到的磁共振图像信噪比为56.14,显著高于Dispect谱仪自带的接收机(SNR = 37.99).两幅图像在同一次扫描序列下获得,图像轮廓相同,但它们来自不同的线圈通道,因此其图像信噪比不能直接进行比较.

3 结论本文提出了一种基于NI PXIe-7966R的MRI接收机设计方法.以板载FPGA为核心,控制磁共振信号高速采集,并直接进行下变频处理,产生I路和Q路数据并上传.下变频功能针对不同接收带宽,灵活地设计滤波器结构、分配抽取因子、配置抽头系数,具有较好的滤波特性.下变频设计过程具有很好的灵活性和可编程性,采用图形化的HLS设计工具NI LabVIEW FPGA,清晰地显示数据流、快速完成FPGA功能的仿真和验证、并自动化编译,很大程度上降低了开发难度,加快了开发速度.实验证明该接收机实用性和灵活性较好、效率较高.

| [1] | VILLA M, TIAN F, COFRANCESCO P, et al. High-resolution digital quadrature detection[J]. Rev Sci Instrum, 1996, 67(6): 2123-2129. DOI: 10.1063/1.1147025. |

| [2] | LI G Y, XIE H B. Digital quadrature detection in nuclear magnetic resonance spectroscopy[J]. Rev Sci Instrum, 1999, 70(2): 1511-1513. DOI: 10.1063/1.1149615. |

| [3] |

XU Q, SHEN J, JIANG Y, et al. A digital receiver for nuclear magnetic resonance spectrometer[J].

Chinese J Magn Reson, 2005, 22(4): 357-365.

徐勤, 沈杰, 蒋瑜, 等. 一体化核磁共振数字接收机的设计[J]. 波谱学杂志, 2005, 22(4): 357-365. |

| [4] |

GU X F, JIANG Z D, ZU D L, et al. PCI-based digital frequency source for MRI[J].

Chinese J Med Imaging Technol, 2005, 21(6): 959-962.

谷晓芳, 姜忠德, 俎栋林, 等. 基于PCI总线的MRI数字频率源设计[J]. 中国医学影像技术, 2005, 21(6): 959-962. |

| [5] | LIU Y, LI G. F_TDM receiver for parallel acquisition of MRI[J]. Electron Lett, 2008, 44(7): 454-456. DOI: 10.1049/el:20080013. |

| [6] |

YAN Z, ZHAO W Y, WANG H X, et al. Design of a parallel high-speed receiving system[J].

Chinese J Magn Reson, 2011, 28(2): 198-206.

严政, 赵武贻, 王慧贤, 等. 磁共振信号并行高速接收系统设计[J]. 波谱学杂志, 2011, 28(2): 198-206. |

| [7] |

ZHU L, FEI Y C. Application of AD6636 in a wideband digital intermediate frequency receiver[J].

Modern Electronic Technique, 2005, 28(23): 39-41.

朱良, 费元春. AD6636在宽带数字中频接收机中的应用[J]. 现代电子技术, 2005, 28(23): 39-41. DOI: 10.3969/j.issn.1004-373X.2005.23.017. |

| [8] | LYONS R G. Understanding cascaded integrator-comb filters[J]. Embedded Systems Programming, 2005(4):14-16, 18, 20, 23-27. http://www.eetindia.co.in/ART_8800503098_1800005_TA_969aa80d.HTM |

| [9] | DOLECEK G J, MITRA S K. Simple method for compensation of CIC decimation filter[J]. Electron Lett, 2008, 44(19): 1162-1163. DOI: 10.1049/el:20081603. |

| [10] | XILINX. Virtex-5 FPGA data sheet:DC and switching characteristics[OL]. 2010.05, http://www.xilinx.com/support. |

| [11] | 俎栋林. 核磁共振成像学[M]. 北京: 高等教育出版社, 2004. |

| [12] | 李睿. 磁共振成像谱仪的软件设计及成像序列研究[M]. 北京: 北京大学信息科学技术学院, 2009. |

| [13] |

LI R, XIAO L, WANG W M. The design of a digital receiver system for mri scanners[J].

Chinese J Magn Reson, 2009, 26(3): 359-368.

李睿, 肖亮, 王为民. 磁共振成像信号的数字化接收系统设计[J]. 波谱学杂志, 2009, 26(3): 359-368. |

| [14] | AELTERMAN J, LUONG H Q, GOOSSENS B, et al. Augmented Lagrangian based reconstruction of non-uniformly sub-Nyquist sampled MRI data[J]. Signal Process, 2011, 91(12): 2731-2742. DOI: 10.1016/j.sigpro.2011.04.033. |

| [15] |

WANG H, SUN H Y, TANG W N, et al. An FPGA-based multi-channel receiver module for magnetic resonance imaging[J].

Chinese J Magn Reson, 2012, 29(2): 239-247.

王洪, 孙宏宇, 汤伟男, 等. 基于单片FPGA的多通道磁共振成像接收模块[J]. 波谱学杂志, 2012, 29(2): 239-247. |

| [16] |

ZHENG C B, XIE J Y, LI J Q, et al. Digital down-conversion technology based on DSP Builder[J].

Information Technology, 2015, 5: 44-47.

郑呈斌, 谢君尧, 李建奇, 等. 基于DSP Builder的数字下变频技术[J]. 信息技术, 2015, 5: 44-47. DOI: 10.3969/j.issn.1674-7461.2015.01.009. |

| [17] |

QIN Y, MAO Y F, QIN S R. FIR digital filter design based on proximate best uniform approximation theory[J].

Journal of Chongqing University (nature science edition), 2006, 29(5): 12-15.

秦毅, 毛永芳, 秦树人. 基于近似最佳一致逼近原理的FIR数字滤波器[J]. 重庆大学学报(自然科学版), 2006, 29(5): 12-15. |

| [18] | MICHAL C A, BROUGHTON K, HANSEN E. A high performance digital receiver for home-built nuclear magnetic resonance spectrometers[J]. Rev Sci Instrum, 2002, 73(2): 453-458. DOI: 10.1063/1.1433950. |

| [19] | SHEN J, XU Q, LIU Y, et al. Home-built magnetic resonance imaging system (0.3 T) with a complete digital spectrometer[J]. Rev Sci Instrum, 2005, 76(10): 105101. DOI: 10.1063/1.2069707. |

| [20] |

SUN H Y, TANG W N, WANG W M. Improving signal-to-noise ratio in magnetic resonance imaging using dynamic receiver gain[J].

Chinese J Magn Reson, 2014, 31(4): 515-522.

孙宏宇, 汤伟男, 王为民. 利用动态接收增益提高磁共振成像信噪比的方法[J]. 波谱学杂志, 2014, 31(4): 515-522. DOI: 10.11938/cjmr20140406. |

| [21] | MCCANN A J, WORKMAN A, MCGRATH C. A quick and robust method for measurement of signal-to-noise ratio in MRI[J]. Phys Med Biol, 2013, 58(11): 3775-3790. DOI: 10.1088/0031-9155/58/11/3775. |

2017, Vol. 34

2017, Vol. 34