2. 中国科学院大学, 北京 100049

2. University of Chinese Academy of Sciences, Beijing 100049, China

铷原子频标(RAFS)具有体积小、重量轻、功耗低的特点,是目前使用最广泛的原子频标[1].铷原子频标可以简单地分为物理系统和电路系统两部分.电路系统一般由射频倍频器、频率综合器、调制器和同步检波器组成.已有文献报道实现10 MHz信号经过频率综合器产生5.312 5 MHz信号方案,通常的做法是通过现场可编程门阵列(FPGA)+直接数字频率合成器(DDS)实现,在该方案中,5.312 5 MHz信号是由参考信号经过高次倍频后经DDS器件直接合成产生.

DDS器件可以精确预置输出频率和相位,应用灵活、易于集成,但受常用DDS器件(AD9852)自身的技术要求所限,存在功耗高、发热量大(5 V/1 A,器件外部必须装有散热片)、杂散大等缺点.最重要的是,根据Nyquist采样定理,DDS的最高输出频率应小于输入时钟的一半(fc/2),实际应用中一般只能达到40% fc.也就是说,上述方案中为直接获得5.312 5 MHz信号,通常情况下10 MHz参考信号必须经过多次倍频后才能作为AD9852器件的输入时钟.从理论上讲,倍频器将信号频率提高N倍,会让相噪抬高20lgN(单位为dB),类似的N分频会让相噪降低20lgN(单位为dB).那么经过计算,由5次倍频电路所引入的附加相噪为14 dB,不容忽视.

经过分析发现,5.312 5 MHz信号既可以由较高频率信号经DDS器件直接生成,又可以通过5 MHz和0.312 5 MHz信号混频后获取.其中0.312 5 MHz信号属于低频信号,10 MHz信号为0.312 5 MHz信号的32倍频,按照Nyquist采样定理,10 MHz信号完全可以直接作为DDS器件的输入时钟,经过直接数字频率合成后得到0.312 5 MHz信号.

按照上述设计思想,只需利用DDS器件产生0.312 5 MHz信号即可.由于设计需求简化,选用AD9852/AD9854之类功能复杂的DDS器件并不适合.而另一款DDS器件AD9956,既能够以10 MHz直接作为输入时钟,又具有功耗低(无需散热片)、调试简便等优点,通过编程可精确预置输出频率和输出相位,完全能够满足上述设计需求.以下将具体介绍采用AD9956器件设计并实现的铷原子频标5.312 5 MHz频率综合器新方案.

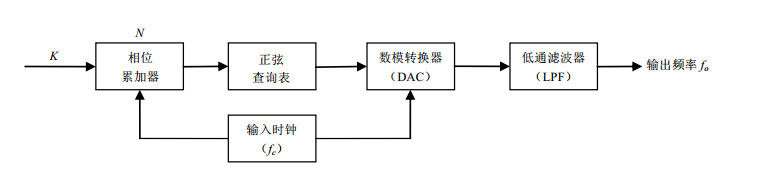

1 频率综合器的工作原理及设计 1.1 工作原理DDS的工作原理如图 1所示.它利用采样定理,通过查表法产生波形.其内部结构由相位累加器与累加寄存器级联构成.每来一个输入时钟,相位累加器将控制字K与累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使加法器在下一个输入时钟的作用下继续与频率控制字相加.这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加.由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加1次,相位累加器输出的数据就是合成信号的相位,相位累加器的输出频率就是DDS输出的信号频率.用相位累加器输出的数据作为波形存储器(ROM)的相位取样地址.这样就可把存储在波形存储器内的波形抽样值(二进制编码)经查找表查出,完成相位到幅值转换.波形存储器的输出送到数模转换器(DAC),DAC将数字量形式的波形幅值转换成所要求合成频率的模拟量形式信号[2].低通滤波器用于滤除生成的阶梯形正弦波中的高频成分,以便输出光滑、频谱纯净的正弦波信号.

|

图 1 DDS工作原理图 Figure 1 Diagram of DDS working principle |

本设计方案选用的器件为AD9956,它是一款功能先进、性价比很高、应用广泛的DDS芯片,该芯片由美国Analog Devices公司生产,内部集成一个采用相位累加器的数字控制振荡器、一个正弦查找表和一个14位数模转换器,它最高支持400 MHz输入时钟,48位分辨能力使频率控制精度可达40亿分之一[3].AD9956具有80 dB无杂散动态范围(SFDR),能实现快速的跳频.调频和控制字通过串行I/O接口加载进入AD9956,器件的写入速度为25 MbPs.器件的DDS模块还支持用户定义的线性扫描模式.

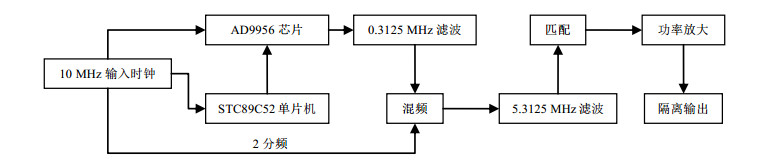

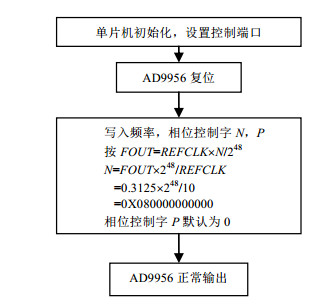

AD9956中DDS的3种工作模式通过控制单元写入数据和地址,来配置DDS的工作模式,通过控制寄存器(CFR)的模式比特位,选择相应的工作模式.AD9956的工作温度范围为-40~125 ℃.其输出频率FOUT=REFCLK×N/248.本文中REFCLK为10 MHz参考时钟,N为FOUT输出0.312 5 MHz时,由单片机STC89C52控制器写入AD9956频率控制寄存器中的48位控制字.将10 MHz信号经过2分频后与AD9956芯片输出的0.312 5 MHz信号混频相加后即得到5.312 5 MHz信号.为了能够满足谐波、相位噪声、稳定度等技术要求,还需增加滤波、匹配、功率放大、隔离输出等电路.本文频率综合器设计方案工作原理如图 2所示.

|

图 2 频率综合器设计方案原理图 Figure 2 Frequency synthesizer design scheme schematic diagram |

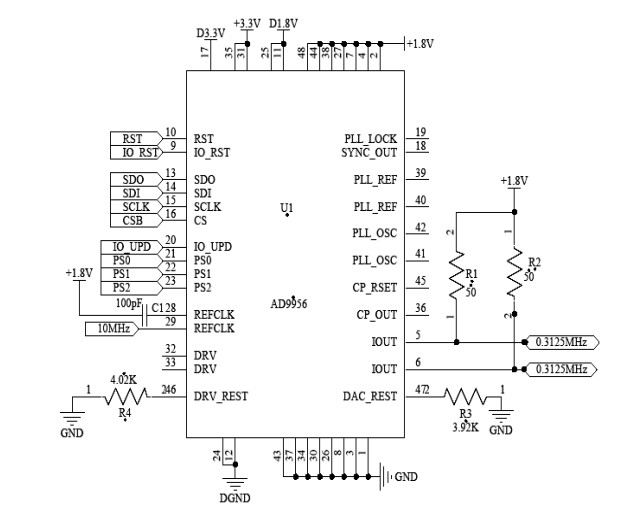

按图 2的设计原理,频率综合器包含有单片机STC89C52主控单元电路、AD9956单元电路、混频电路、两级滤波电路、匹配、放大以及隔离输出电路.限于篇幅,本文仅给出AD9956单元电路、3阶椭圆低通0.312 5 MHz滤波电路以及混频电路的设计,其余部分从略.图 3所示为AD9956单元电路.REFCLK即为输入时钟管脚,接10 MHz参考源信号.

|

图 3 AD9956单元电路 Figure 3 AD9956 unit circuit |

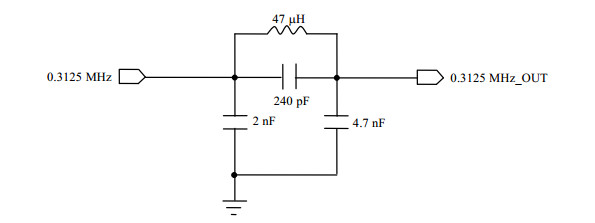

AD9956输出的0.312 5 MHz由于含有丰富谐波成分,正弦信号呈阶梯波状,必须经过低通滤波器“提纯”、滤除带外杂散后方可使用.椭圆函数滤波器由于其过渡带很窄、下降迅速,相比其他函数滤波器性能更好[4].结合设计需求,本设计方案选择3阶椭圆低通滤波器,截止频率为0.34 MHz,配合软件仿真计算,该电路设计图如图 4所示.

|

图 4 椭圆低通滤波电路设计原理图 Figure 4 Design of elliptical low-pass filter circuit |

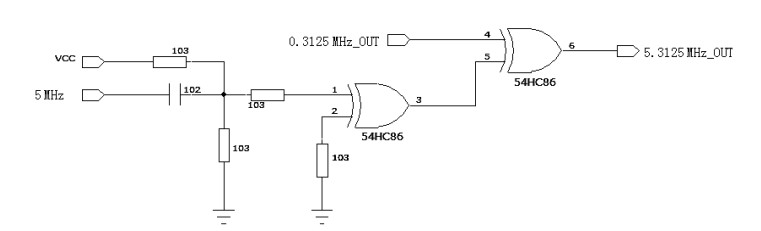

经滤波后0.312 5 MHz信号与5 MHz信号(由10 MHz经过2分频电路产生)的混频是通过54HC86异或门(等同于作加法)得到,该电路的设计原理图如图 5所示.其输出为方波,再经过高Q值、窄带通晶体滤波电路和选频放大后最终可获得5.312 5 MHz正弦波信号.

|

图 5 混频电路设计原理图 Figure 5 Design of mixing circuit |

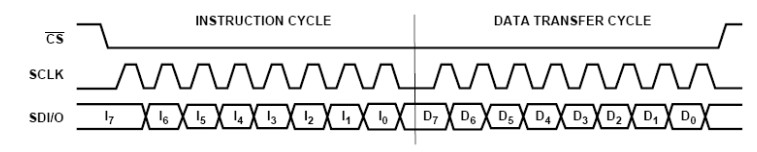

单片机通过串行口实现对AD9956内部寄存器的读写,读写操作受到引脚SCLK上时钟信号的控制,在每个SCLK上升沿写1位数据,如图 6所示.在AD9956中串行操作是在寄存器级执行的,而不是在字节级执行.AD9956与单片机的通信周期分两个阶段:第1个阶段是指令周期,在这个阶段把指令字节写入AD9956,指令字节除了指出读写操作和寄存器地址外,还同时给出了第2个阶段所要传送数据的字节数;第2个阶段为数据传送周期,传送信号参数的控制字[5].

|

图 6 AD9956控制时序图 Figure 6 AD9956 controls the timing diagram |

对AD9956软件控制流程图如图 7所示.

|

图 7 AD9956软件控制流程图 Figure 7 AD9956 software controls flow chart |

为了对本设计方案实现的频率综合器电路性能进行评估,我们对新、旧两种数字化方案频率综合器输出信号的谐波、相噪等主要性能指标进行了测试和分析.

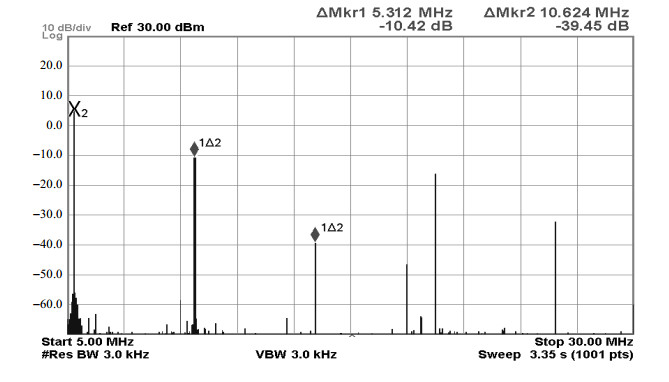

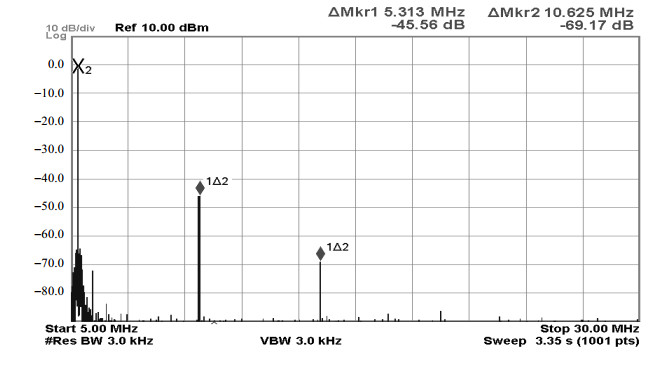

图 8为使用频谱仪对采用旧综合器方案(10 MHz经5次倍频+AD9852)所测量输出5.312 5 MHz频率信号的2次和3次谐波频谱图.

|

图 8 旧频率综合器方案谐波频谱图 Figure 8 Old frequency synthesizer scheme harmonic spectrum |

图 9为使用频谱仪对采用新频率综合器方案(10 MHz无需倍频+AD9956)所测量输出5.312 5 MHz信号的2次和3次谐波频谱图.

|

图 9 新频率综合器方案谐波频谱图 Figure 9 New frequency synthesizer scheme harmonic spectrum |

从图 8和图 9可以看出,采用新方案频率综合器输出的5.312 5 MHz频率信号的谐、杂波指标明显优于旧方案频率综合器.

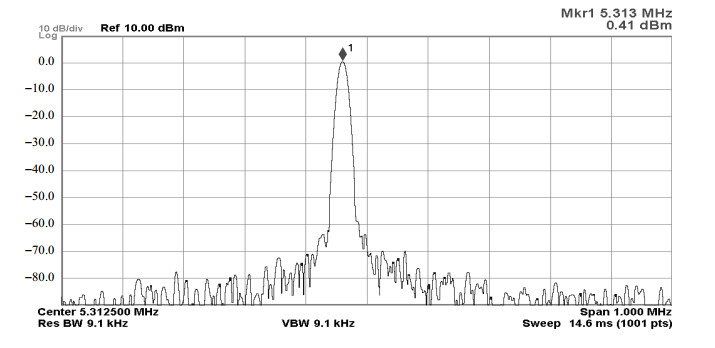

另外,我们使用频谱仪在SPAN为1 MHz范围内对新方案综合器的5.312 5 MHz信号进行了更细致的测试,获得的频谱如图 10所示.测试结果表明,该综合器输出的5.312 5 MHz信号频谱纯度较高、杂散噪声得到了充分抑制.

|

图 10 5.312 5 MHz信号频谱图 Figure 10 5.312 5 MHz signal spectrum |

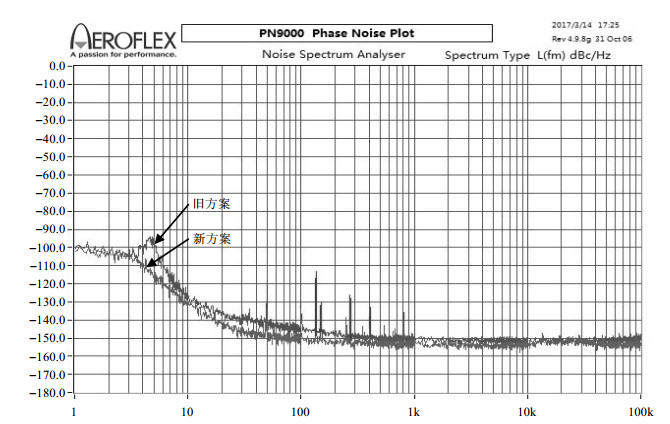

我们用PN9000相噪分析仪对新、旧两种方案频率综合器输出信号的相位噪声进行了测试,相噪测试结果如图 11所示.

|

图 11 新旧频率综合器方案输出信号的相位噪声 Figure 11 Phase noise of the output signal using old and new frequency synthesizer |

从图 11可以看出,采用无倍频设计的新频率综合器方案相位噪声优于采用倍频电路的旧频率综合器方案.

将采用新、旧两种频率综合器方案在同样的测试环境下产生的5.312 5 MHz信号的技术指标进行分析对比,如表 1所示.

| 表 1 新、旧两种频率综合器性能指标对比 Table 1 Comparison of performance characteristics using new and old frequency synthesizer |

分析对比结果表明,采用0.312 5 MHz信号与5 MHz信号混频的无倍频设计新方案,不仅可以产生精确的5.312 5 MHz信号,并且谐波、相噪指标均优于采用倍频电路的旧方案.新频率综合器方案产生的5.312 5 MHz信号经过滤波、功率放大后,与6 840 MHz信号混频即可得到满足铷原子频标工作需求的683 4.687 5 MHz微波探寻信号.

3 结论本文针对铷原子频标5.312 5 MHz频率综合器展开研究和优化设计,在不使用内部或外部倍频电路的情况下,直接利用铷原子频标10 MHz基准信号作为DDS器件的输入时钟,实现了5.312 5 MHz信号的频率合成及产生.该频率综合器设计方案具有结构简单、频谱纯度较高、相位噪声低等优点,采用该综合器设计方案有利于提高铷原子频标整机的性能指标并降低成本.

| [1] | 王义遒, 王庆吉, 傅济时, 等. 量子频标原理[M]. 北京: 科学出版社, 1986. |

| [2] | 自居宪. 低噪声频率合成器[M]. 西安: 西安交通大学出版社, 1994. |

| [3] |

WEN S J, QIAN C. PLL reference source design based on AD9956[J].

Modern Radar, 2007, 29(12): 1-3.

温慎洁, 钱澄. 基于AD9956的锁相参考源设计[J]. 现代雷达, 2007, 29(12): 1-3. DOI: 10.3969/j.issn.1004-7859.2007.12.001. |

| [4] |

JIA X B, LIU S X, JIA H L, et al. Design of low-pass elliptic filter based on DDS[J].

Electronic Design Engineering, 2010, 18(9): 171-173.

贾晓斌, 刘四新, 贾海亮, 等. 基于DDS的椭圆函数低通滤波器的设计[J]. 电子设计工程, 2010, 18(9): 171-173. |

| [5] |

JIANG Y H, LI Z. One realization method of DDS techonology based on chip AD9956[J].

J Astronautic Metrology and Measurement, 2005, 25(3): 6-9.

姜永华, 李峥. 一种基于AD9956芯片的DDS技术实现方法[J]. 宇航计测技术, 2005, 25(3): 6-9. |

2017, Vol. 34

2017, Vol. 34