磁共振成像(Magnetic Resonance Imaging,MRI)系统主要由磁体、谱仪和计算机等部分组成,其中脉冲序列发生器是MRI谱仪中的核心部件之一,用于实时控制谱仪中其他部件之间的协同工作[1-3].由于成像系统的各硬件部件对触发信号的响应时间不同,在MRI实验中各部件之间会存在相对延时.以梯度系统延时为例,它会使成像脉冲序列中选层梯度、相位编码梯度以及频率编码梯度相对于射频脉冲信号的时序发生紊乱,导致磁共振图像的退化与失真,进而无法获得准确的医学诊断信息[4].因此对MRI系统中各部件之间的相对延时进行补偿具有重要的意义和作用.

在MRI实验中,脉冲序列数据以“事件-时间”(“E-D”)列表的格式从计算机下载到脉冲序列发生器中,用于更新脉冲序列发生器的输出状态[5-7].目前常用于消除相对延时对磁共振图像质量影响的方法有两种.第一种是在脉冲序列执行之前,首先利用软件对“E-D”表进行“时间移位”处理[4],之后再下载到脉冲序列发生器的存储单元中进行解码输出,以实现脉冲序列发生器对各个部件的异步触发,即提前触发相对延时较大的部件,从而对各部件之间的相对延时进行补偿.由于在“时间移位”处理过程中原列表中的“时间”将被分割成多个部分,分割精度有赖于脉冲序列发生器的最小脉冲宽度.这将导致脉冲序列发生器所发出的脉冲序列的时间分辨率降低,使脉冲序列发生器无法精确控制各个部件之间的工作时序,对实验过程和图像质量产生影响.第二种方法是通过优化脉冲序列设计[8],实现在梯度、射频和接收等部件上可控的延时.但是对于某些脉冲序列,例如任意断层的MRI序列,由于选层梯度、相位编码梯度以及频率编码梯度在仪器梯度系统中的x、y、z三个空间方向上存在投影分量,因此这种方法难以完全消除三路空间编码梯度的相对延时效应,对提高磁共振图像质量的作用有限.

针对上述问题,本文设计了一种具有独立通道延时功能的脉冲序列发生器,通过在脉冲序列输出通道上添加延时电路,实现脉冲序列发生器对谱仪中各个部件进行异步触发的功能,从硬件上消除相对延时.在参考文献[4]中,利用软件方法进行延时补偿的精度为400 ns,本文设计的脉冲序列发生器每一路通道的最大延时值可以达到819 μs,补偿精度则提高到50 ns.对于梯度系统延时的补偿[8],在本文的设计方案中可以首先通过实验测得x、y、z三个方向上的延时值,再根据延时值的大小调整三路梯度通道所对应的脉冲序列发生器输出通道上的延时参数,以达到精确补偿的目的.下面给出了该脉冲序列发生器的详细设计方案,以及性能测试的结果.

1 设计方案 1.1 脉冲序列数据的表示方式本文设计的脉冲序列发生器具有16个独立的输出通道,每一个输出通道的状态由一位二进制数来确定,16个输出通道的状态组合被称为“事件”[7].每当任意一个通道状态发生改变,则将其定义为一个新的事件,每一个事件的持续时间由该事件所对应的“时间”值决定,因此整个脉冲序列可以由一组离散的“E-D”表来表示[2].

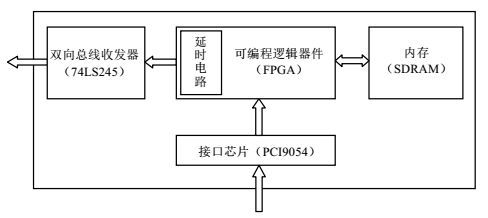

1.2 脉冲序列发生器的结构图 1为脉冲序列发生器的硬件结构框图.本文中设计的脉冲序列发生器是基于外围部件互连总线(Peripheral Component Interconnect, PCI)与主机进行数据交互.为了简化设计,采用了PCI桥芯片(PCI9054, PLX Inc, USA)实现PCI总线与脉冲序列发生器本地总线之间的通信;现场可编程门阵列(Field Programmer Gate Array, FPGA)是脉冲序列发生器的核心,设计中采用Xilinx公司的XC3S500E-PQ208负责整块板卡的逻辑控制;同步动态随机存储器(Synchronous Dynamic Random Access Memory, SDRAM)用于存储板卡上的脉冲序列数据,设计中采用了Micron公司的MT48LC32M16A2,其存储容量为64 MB可以满足现有MRI实验的要求;8路同相三态双向总线收发器(74LS245, Semiconductor Components Inc, USA)用于提高FPGA输出信号的驱动能力.

在执行脉冲序列之前,先将脉冲序列数据以“E-D”表的形式依次通过PCI9054和FPGA写入到SDRAM中.在执行脉冲序列的过程中,脉冲序列数据从SDRAM中读出,经FPGA处理后得到的脉冲序列信号,再由74LS245提高其驱动能力后,用于对谱仪中各个部件进行实时控制.本文中脉冲序列发生器的FPGA和PCI桥芯片使用40 MHz工作时钟.在读取SDRAM数据的过程中,为了提高访问速度,减小最小脉宽,利用FPGA将40 MHz时钟倍频到80 MHz,以提供给SDRAM作为数据读写的工作时钟.

|

图 1 脉冲序列发生器结构框图 Figure 1 Block diagram of pulse generator |

本文利用硬件描述语言(Very-High-Speed Integrated Circuit Hardware Description Language, VHDL)对FPGA芯片进行开发,在其内部构建与SDRAM进行数据传输的接口模块、用于存储FPGA内部信号的寄存器模块、产生脉冲序列的波形发生单元以及用于数据缓存处理的先进先出(First In First Out, FIFO)模块.在MRI实验中,对样品的选层激发需要发射多次射频软脉冲,因此需要脉冲序列发生器不断地触发频率源对射频波形进行调制,相当于进行一次选层激发就需要多组相同的“E-D”表数据.为了节约板上存储空间,以执行更加复杂的脉冲序列,对脉冲序列数据采用了(LLi,LNi,E1,D1,E2,D2……ELLi,DLLi)的形式进行编码,并将编码后的数据存储到SDRAM中.其中,LLi表示循环体中脉冲序列数据的个数,LNi表示脉冲序列数据的循环次数,(E1,D1,E2,D2……ELLi,DLLi)是当前循环体中的脉冲序列数据,当LLi或LNi为0时,表示脉冲序列数据的结束.

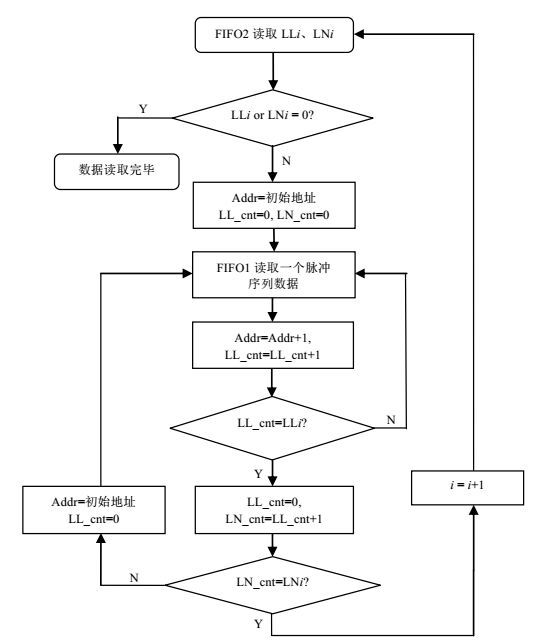

在MRI谱仪中,对脉冲序列数据的解码方式直接影响着最小脉冲宽度的大小,而最小脉冲宽度是衡量脉冲序列发生器性能的重要指标,其决定了两个连续事件之间的最快更新速率.本设计采用的数据解码方式示意图如图 2所示.

|

图 2 数据解码流程图 Figure 2 Flow chart of data decoding |

在FPGA内部的波形发生单元模块与SDRAM读写接口模块之间,建立两块内部FIFO,分别为FIFO1和FIFO2.在解码脉冲序列数据的过程中,利用变量LL_cnt和LN_cnt对已读入到FIFO1中的数据进行计数.首先FPGA中的SDRAM读写接口模块从SDRAM中读取LLi、LNi的值经FIFO2缓存后写入到寄存器中并将LL_cnt和LN_cnt分别置为0.之后SDRAM读写接口模块控制SDRAM往FIFO1中写入脉冲序列数据,每写入一个数据LL_cnt和用于读取SDRAM中脉冲序列数据的地址变量(Addr)分别加1.之后比较LL_cnt与LLi的值是否相等,若不相等,重复上一步的操作;若相等则将LL_cnt置为0,并将LN_cnt加1后,再比较LN_cnt与LNi的值是否相等.若不相等,则Addr赋值为本循环体中数据的初始地址,并重复上述操作,开始重新读取本循环体中的数据;若相等,表示本循环体中的数据读取完毕,将读取下一个循环体中的数据.本设计中,在SDRAM往FIFO1写入数据的过程中进行解码计数的操作,因此FIFO1中存储的是经过解码的脉冲序列数据,当波形发生单元从FIFO1读取数据时不再需要进行计数以判断是否达到LLi、LNi这两个设定值.因此本设计中采用的数据解码方式,可以有效减小脉冲序列发生器的最小脉冲宽度,提高了脉冲序列发生器的性能,同时也使利用软件方法进行相对延时补偿的时间精度得到了提高.

1.4 独立通道延时功能的实现本文通过在脉冲序列发生器的输出通道上添加延时电路,实现对谱仪中各个部件进行异步触发的功能,从硬件上来消除相对延时对于磁共振图像的影响.可以采用深度可编程的FIFO芯片构建延时电路,也可采用脉冲序列发生器上FPGA芯片的内部FIFO构建延时电路.前一种方法不会消耗FPGA内部存储资源,但会增加脉冲序列发生器硬件结构的复杂性.后一种方法要求FPGA内部存储资源必须满足设计需要,但是FPGA对其内部FIFO的控制会更加灵活高效.本设计所使用的FPGA芯片(XC3S500E-PQ208)内部具有容量为360 kB的块随机存储器(Block Random Access Memory, BRAM)资源,因此本文采用了通过在FPGA内构建FIFO组成延时电路的设计方案.本文中的脉冲序列发生器具有16路输出通道,需要利用FPGA内部的块RAM资源建立16个FIFO,每一个FIFO与一个输出通道相对应.当波形发生单元解码得到“E-D”表数据后,将事件值(Event)的每一位数据都发送到对应的FIFO中,每一个FIFO的存储深度都可以独立设定.对于需要进行延时的第i(i = 1, 2……16)路通道的数据,通过设定该通道上的计数器上限值Mi的大小来实现延时缓存的处理.

图 3为脉冲序列发生器单个输出通道上实现延时功能的流程图,对于多通道而言,相同步骤是并行执行的.具体的工作流程如下:

|

图 3 延时功能的流程图 Figure 3 Flow chart of delay function |

(1)首先设定每一路通道对应的FIFOi的存储深度以及计数器上限值Mi的大小.

(2)当脉冲序列发生器接收到上位机发出的“start”命令后,FPGA内部的波形发生单元从SDRAM中解码得到多组“E-D”表数据,并且将事件值(Event)的每一位数据传送到对应的FIFOi上等待写入,之后向延时电路模块发送“output”高电平信号.

(3)当延时电路模块接收到波形发生单元发送的“output”高电平信号后,往FIFOi发送一个写指令,FIFOi则开始写入数据,每写入一个数据计数器counti加1.

(4)判断计数器的值是否达到所设定的Mi的大小,若是则往FIFOi发送一个读指令,使其开始往外发送数据,更新该FIFO所对应的输出通道的状态,若不是则继续写入数据并进行计数.

(5)当脉冲序列发生器的延时电路模块接收到来自上位机或者波形发生单元的“stop”高电平信号,以及FIFOi的空信号时,FIFOi停止发送数据并复位.

独立通道延时功能是通过在ISE(Xilinx公司的FPGA设计工具)软件编译环境下,编写VHDL代码并下载到FPGA中实现的.通过上述方法,可以实现对脉冲序列发生器中每一路输出通道进行独立延时的功能.对于谱仪中相对延时较大的部件,可以减小该部件所对应的脉冲序列输出通道上计数器上限值Mi的大小,实现对该部件的提前触发,以达到补偿矫正相对延时的目的.

2 实验结果图 4为本文所设计脉冲序列发生器的实物图.

|

图 4 脉冲序列发生器实物图 Figure 4 Photograph of the pulse generator |

脉冲序列发生器具体性能指标如表 1所示.

| 表 1 脉冲序列发生器性能指标 Table 1 Characteristics of the pulse generator |

为了测量真实的最小脉冲宽度和步进值,通过上位机向板卡上的SDRAM中写入“E-D”表(0, 1;1, 1;0, 2;1, 2;0, 3;1, 3),并发送到波形发生单元进行解码输出.图 5为利用示波器(Tektronix MSO 2024)采集到的脉冲波形,经过光标测量,其中最左端高电平脉冲持续时间为125 ns,其后的高电平持续时间往右依次为150 ns、175 ns.根据测量结果可以得到最小脉冲宽度大小为125 ns,脉冲宽度的步进值为25 ns,图中横轴每一小格的代表的时间为20 ns.

|

图 5 最小脉冲宽度的测量 Figure 5 Measurement of the minimal pulse width |

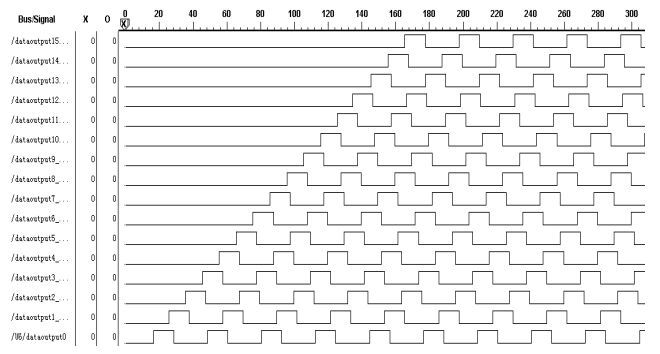

利用在线逻辑分析仪(ChipScope)软件对脉冲序列发生器的16路输出通道延时功能进行了验证测试.为了便于展示每一路通道的独立延时功能,通过上位机控制波形发生单元每隔500 ns发出一个持续时间为300 ns、值为“1111111111111111”的16位二进制数用以更新16个输出通道的状态.同时将通道1~16的延时值即计数器的上限值Mi分别设定为5、10、15、20、25……80.图 6为利用Chipscope采集到的每一路输出通道所对应的计数器值、FIFO读指令、输出脉冲信号的波形数据.如图所示当每一路通道计数器值达到所设定的值Mi后,对应的FIFOi都会接收到一个读指令,继而开始往外发送数据. 图 7为利用Chipscope采集到的经过延时处理的16路输出通道的脉冲波形.

|

图 6 延时功能的测试结果 Figure 6 The test result of delay function |

|

图 7 脉冲序列发生器的输出波形 Figure 7 The output waveform of pulse generator |

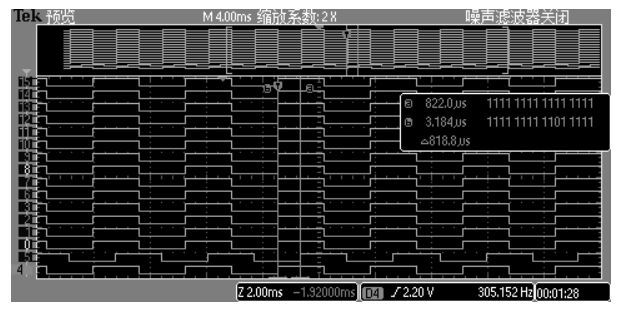

图 8是利用示波器(Tektronix MSO 2024)采集到的经74LS245进行驱动放大后,输出到板卡外的16路输出通道的脉冲波形.根据示波器的测量结果,每一路输出波形的延时值与代码中设定的延时值一致,其中横轴每一小格代表的时间为200 ns.

|

图 8 脉冲序列发生器的输出波形 Figure 8 The output waveform of pulse generator |

在本设计中我们使用FPGA(XC3S500E-PQ208)内部的块RAM(Block RAM)资源来建立每一路输出通道所对应的FIFO,每个FIFO可以存储宽度为一位,深度为16 384的数据,因此理论上可以达到的最大延时值为(16 384×50)ns,即819 μs.为了测量每一路输出通道最大延时的实际值,通过上位机控制波形发生单元每隔1.6 ms发送一个持续时间为1.6 ms、值为“1111111111111111”的16位二进制数,并将其中一路通道上的计数器上限值设置为16 384,而其他各路通道不做延时处理.利用示波器(Tektronix MSO 2024)采集到的波形如图 9所示,通过光标测量可以读出最大延时值为818.8 ms,与理论值一致.其中横轴每一小格代表的时间为400 μs.

|

图 9 延时最大值测量 Figure 9 Maximum value measurement of time-delay |

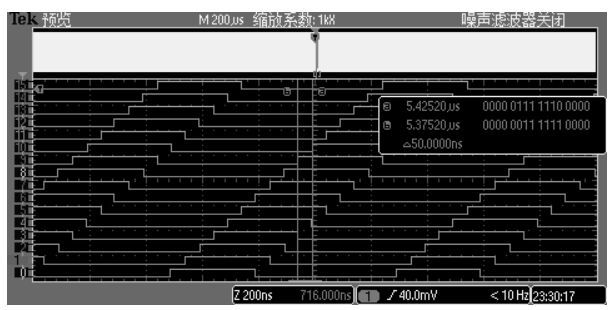

最后我们将代码中每一路通道间的相对延时值修改为1,使通道间发送数据的时间间隔为延时的最小步进值,并通过示波器(Tektronix MSO 2024)对最小步进值进行测量.从图 10中可以读出延时的步进值为50 ns,其中横坐标每一小格代表的时间为40 ns.

|

图 10 延时最小步进值测量 Figure 10 Minimum step value measurement of time-delay |

对于多回波成像实验,梯度系统的延时会导致MRI图像出现严重的带状伪影.在参考文献[4]中提出了一种解决方案,即通过对梯度系统进行延时补偿的方法来消除图像伪影.而且文献[4]多回波成像实验的结果表明该方案可以有效消除图像中由于梯度系统延时所造成的失真,提高了磁共振成像的质量.利用该方法进行延时补偿的精度为400 ns,而本文中设计的脉冲序列发生器同样具有对成像系统中各硬件部件进行延时补偿的功能,并且具有更高的补偿精度,延时步进值可以达到50 ns,因此理论上能够更加精确地补偿相对延时.

3 讨论与总结在MRI实验中,各部件之间的相对延时会导致图像的退化与失真.本文设计的脉冲序列发生器具有独立通道延时功能,每一路通道的最大延时值为819 μs,延时步进值为50 ns,可以精确地补偿相对延时,消除其对磁共振图像质量的影响.当需要进行更大时间跨度的延时补偿时,可以通过选用逻辑资源更加丰富的FPGA芯片来提高脉冲序列发生器的最大延时值,但是这将会增加设计的成本.因此可以利用软件与硬件相结合的方法.以补偿梯度系统延时为例,通过使用编译软件对脉冲序列数据进行重构计算或在实验前进行预扫描操作来优化脉冲序列设计的方法粗略补偿梯度系统中x、y、z三个空间方向上较大时间范围内的相对延时值,再利用脉冲序列发生器可以进行独立延时的功能,实现对每一路输出通道相对延时值进行精确补偿的目的.利用这种方法可以有效消除相对延时的影响,实现脉冲序列发生器性能与成本的最优化,提高磁共振图像的质量.由于16路延时通道是搭建在一块FPGA芯片内部,因此本设计中的通道延时参数是可编程的,针对不同的MRI系统可以设置不同的参数,具有较好的灵活性和通用性.

| [1] | HASHIMOTO S, KOSE K, HAISHI T. Development of a pulse programmer for magnetic resonance imaging using a personal computer and a high-speed digital input-output board[J]. Rev Sci Instrum, 2012, 83(5): 053702. DOI: 10.1063/1.4711132. |

| [2] | HANDA S, DOMALAIN T, KOSE K. Single-chip pulse programmer for magnetic resonance imaging using a 32-bit microcontroller[J]. Rev Sci Instrum, 2007, 78(8): 084705. DOI: 10.1063/1.2773636. |

| [3] | MAO W P, BAO Q J, YANG L, et al. A modularized pulse programmer for NMR spectroscopy[J]. Meas Sci Technol, 2011, 22(2): 025901. DOI: 10.1088/0957-0233/22/2/025901. |

| [4] | NING R P, YANG G, Li G Y. A versatile pulse programmer for magnetic resonance imaging[J]. Rev Sci Instrum, 2011, 82(5): 054301. DOI: 10.1063/1.3587068. |

| [5] | SHEN J, XU Q, LIU Y, et al. Home-built magnetic resonance imaging system (0.3 T) with a complete digital spectrometer[J]. Rev Sci Instrum, 2005, 76(10): 105101. DOI: 10.1063/1.2069707. |

| [6] |

ZHANG Z, MAO W P, LIU C Y. Progress in the development of pulse programmer for nuclear magnetic resonance[J].

Chinese J Magn Reson, 2012, 29(3): 339-345.

张志, 毛文平, 刘朝阳. 核磁共振脉冲序列发生器研究进展[J]. 波谱学杂志, 2012, 29(3): 339-345. |

| [7] |

JI W B, QIAO Y, LEI D, et al. Hardware design for general-purpose pulse generator used in NMR spectrometers[J].

Chinese J Magn Reson, 2007, 24(3): 321-327.

季文彬, 乔勇, 雷都, 等. 通用硬件脉冲序列发生器的研制[J]. 波谱学杂志, 2007, 24(3): 321-327. |

| [8] | 宁瑞鹏. 用于引导HIFU治疗的永磁开放式MRI系统研究[D]. 上海: 华东师范大学, 2011. http://cdmd.cnki.com.cn/Article/CDMD-10269-1011130812.htm |

2017, Vol. 34

2017, Vol. 34