2. 中国地震局地壳应力研究所武汉科技创新基地,武汉市洪山侧路40号,430071

TDC(time to digital converter)即时间数字转换技术,通常用于激光测距[1]、激光三维扫描[2]、绝对重力仪[3]等仪器中的高精度时间间隔测量。TDC有常规计数型、游标卡尺型、时间扩展型、时幅变换型等类型。常规型TDC的时间分辨率极低,游标卡尺型和时间扩展型TDC的测量时间较长,而时幅变换型TDC因采用模拟电路,对环境温度与噪声十分敏感,其稳定性较差[4-8]。本文基于常规计数型TDC设计思想,应用FPGA内部PLL延迟相位技术,设计多个同频率、同间隔相位的参考时钟来对同一待测时间间隔信号进行测量。该方法测量精度达220 ps,较常规计数型TDC的分辨率有很大改善。

1 计数型TDC原理计数型TDC是通过一个精确的高频时钟信号驱动的计数器来测量外部输入信号的时间间隔信息,测量的时间为:

|

(1) |

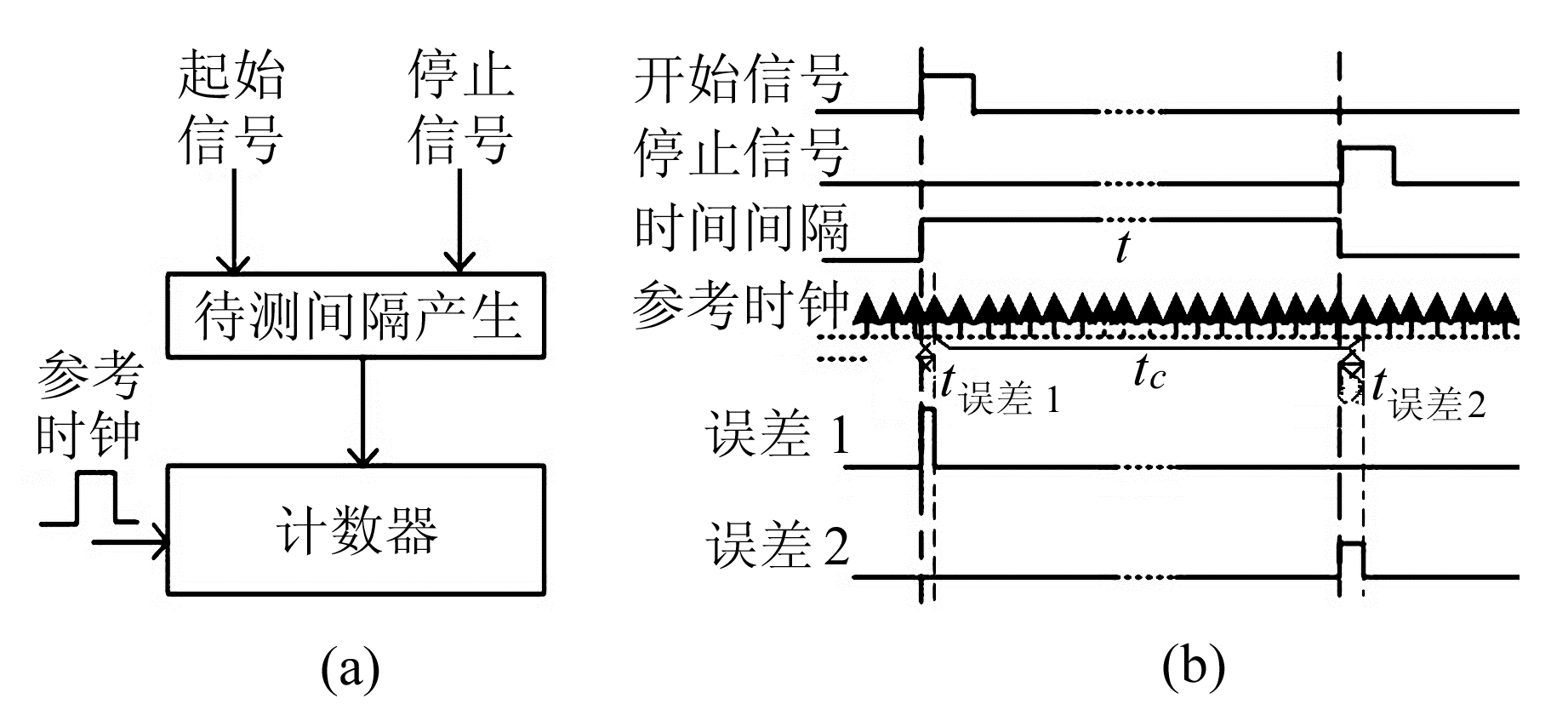

式中,N为计数器的值,tr为高频参考时钟的周期,tc为测量时间。如图 1(a)所示,起始信号和停止信号由待测时间间隔的输出作为使能信号,参考时钟作为时钟CP信号。

|

图 1 计数型TDC Fig. 1 Counting-type TDC |

计数型TDC的测量误差如图 1(b)所示。计数型TDC的测量结果为tc,实际的待测时间间隔为t,t误差1、t误差2分别是待测脉冲上升沿和下降沿与下一个参考时钟上升沿之间的时间间隔。它们之间的关系为:

|

(2) |

|

(3) |

测量误差为:

|

(4) |

式中,t误差1、t误差2在0到Tr之间,-tr≤t误差≤tr。

由上述公式可知,计数型TDC的测量分辨率和精度由参考时钟信号的频率及其稳定度决定。FPGA芯片电路中的参考时钟频率可达上百MHz,其测量分辨率为ns量级。若将参考时钟信号的频率再提高一些,会引入很大的时钟抖动,从而造成计数型TDC的时间测量误差增大。

2 改进的计数型TDC原理计数型TDC的测量精度受FPGA输入参考时钟的限制[9-10],很难获得ps量级的分辨率。本文基于常规计数型TDC的基本电路,应用FPGA内部资源PLL技术和基本逻辑单元延迟链,实现对参考时钟信号的移相,从而改善常规计数型TDC的时间间隔测量精度。

2.1 改进的计数型TDC结构设计改进的常规计数型TDC结构如图 2所示。利用PLL将输入参考时钟倍频成4个同频,即顺序延迟90°的C0、C1、C2、C3。将这4个时钟信号分别通过4个由FPGA内部资源构成的延迟链,将参考时钟顺序延迟N-1次,产生相邻时钟信号间相位差相同的N个参考时钟信号的延迟信号,分别作为N个计数器的计数时钟信号,将待测间隔产生的输出作为计数器的使能信号。N个计数器得到N个计数值,记为ni(1≤i≤N)。将计数值进行数据存储和处理,即可得到开始和停止信号的两时间间隔值。

|

图 2 改进的计数型TDC结构 Fig. 2 The structure of improved counting-type TDC |

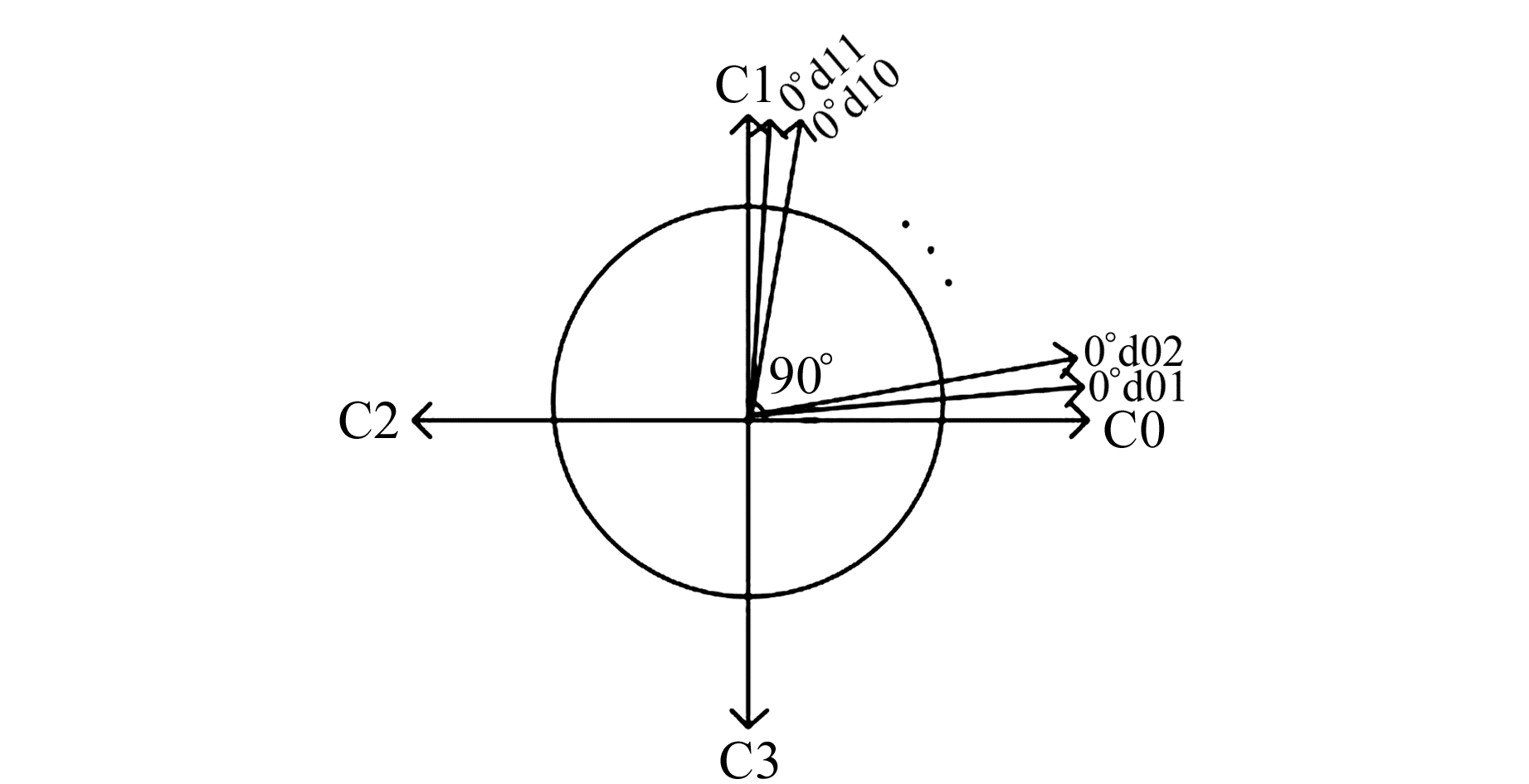

利用PLL的倍频和移相技术,将输入参考时钟倍频到100 MHz,相位依次延迟90°,使用Altera公司的PLL的IP核来实现4个频率为100 MHz的等相位延迟时钟作为相位延迟的4个校准时钟,如图 3所示,C0为相位延迟0°,C1为相位延迟90°,C2为相位延迟180°,C3为相位延迟270°。

|

图 3 参考时钟信号经PLL相移与延迟链的相位分布 Fig. 3 The reference clock signal's phase distribution through the PLL phase shift and delay chain |

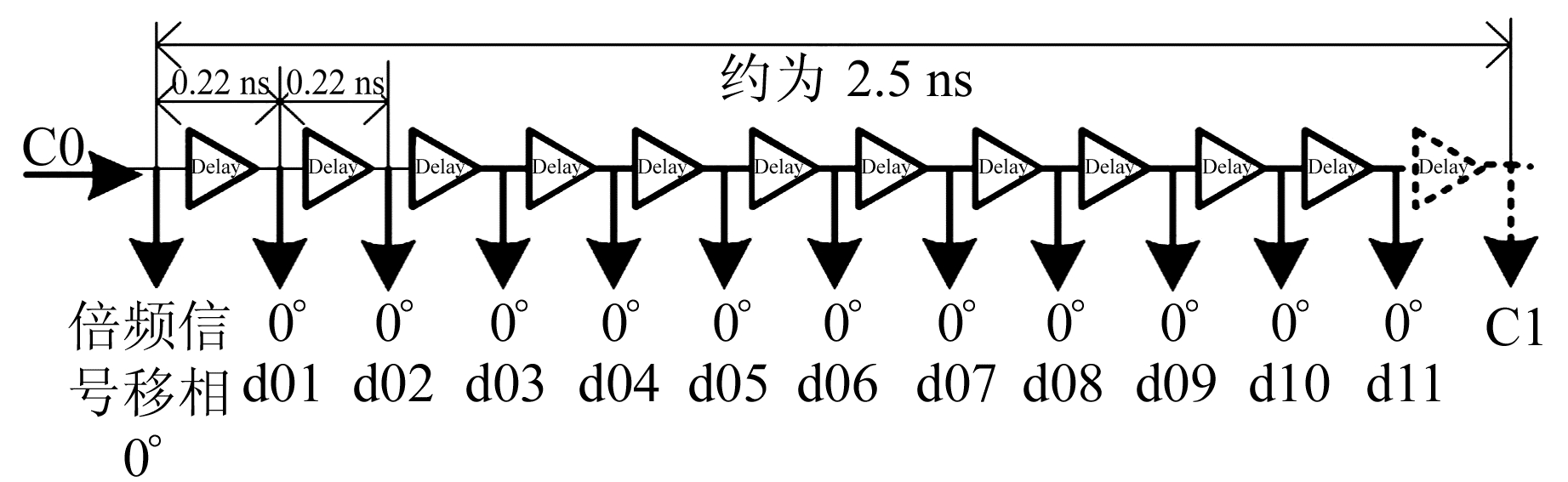

相位延迟设计中,使用PLL生成4个延迟相位(分别为0°、90°、180°、270°)作为校准时钟,将一周期分为4部分,再使用4个延迟链来延迟每个部分的相位。如图 4所示,以C0作为校准时钟的延迟链为例,用11个基本延迟单元级联,即可得总时延约2.5 ns,用4个延时链即可对周期为10 ns的参考时钟相位顺序延迟成48个两相邻相位延迟相等的参考时钟。将4个短的延迟链与一个长的延迟链比较,每一个基本延迟单元的延迟精度较均等,但较长的延迟链易受温度和内部电路走线较长影响,延迟均等性较差。使用PLL的4个相位延迟输出信号作为4个延迟链的时钟,可使48个参考时钟的相位延迟相对均等。

|

图 4 延迟链时序延时模型 Fig. 4 Delay chain timing delay model |

由N个参考时钟相位分布可知,输入参考时钟通过PLL倍频和移相后,再经过N次延迟,可得到最后一个参考时钟的频率大约刚好延迟一个周期T。由于N-1次延迟单元的延迟形成N-1个参考时钟和0°相移的参考时钟,所以,形成的N-1个参考时钟信号在一个周期内的移相信号均匀。每个单元的延迟时间为:

|

(5) |

每个计数器值为Ni,其算数平均值作为计数器的计数值,即待测时间值。可知,改进后的常规计数型TDC测量的时间间隔值为:

|

(6) |

由式(4)和(6)比较可知,改进后的计数型TDC测量误差为:

|

(7) |

根据N个参考时钟之间的相位差得其延迟时间td,在理论上可以把N个参考时钟间的时延定义为公差td的等差数列。将等差数列求和并代入式(8),可得改进后的计数型TDC设计测量误差:

|

(8) |

比较式(4)和(8),改进后的常规计数型TDC相比常规计数型TDC,测量分辨率提高N倍,即测量误差减小N倍。理论上,改进后的常规计数型TDC得到的测量结果是在其他条件不变的情况下将参考频率值提高N倍的测量结果。

3 基于Cyclone Ⅳ改进的计数型TDC的实现改进的常规计数型TDC是在Altera公司FPGA器件上实现的。根据改进的常规计数型TDC原理,再进行电路结构优化,将其分成5个子模块:PLL子模块、时间间隔产生子模块、延迟链模块、计数器子模块、数据存储子模块。采用自顶向下的设计原则实现[11-14]。

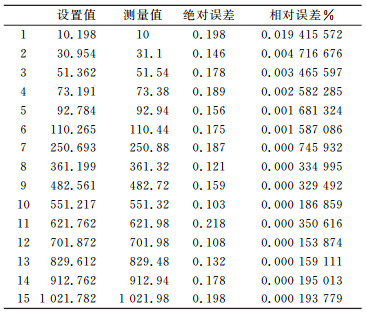

对改进的TDC进行实验验证。输入参考时钟信号频率50 MHz,通过PLL进行2倍频,计数参考时钟频率为100 MHz。从理论可知,系统的测量分辨率大约为200 ps,最大测量误差约为200 ps。通过编写测试开始start与停止stop激励信号对该改进的计数型TDC进行验证。表 1给出了改进的计数型TDC测量值的对比结果(单位:ns),测量误差基本在200 ps之内。

|

|

表 1 改进的TDC时间间隔测量结果 Tab. 1 The design of TDC time interval measurement results |

本文设计并实现了一种在常规计数型TDC基础上的改进型TDC,其具有测量误差小、实现方法简单、集成度高、稳定性好以及移植性较强的优点。后续将对设计电路进一步优化,可将延迟链用在FPGA中延迟更小的内部逻辑资源(如进位链、移位寄存器等),以构建和使用高端FPGA芯片提高输入参考时钟频率,进一步提高改进型常规TDC的分辨率和精度。

| [1] |

朱威, 王培源, 李欣, 等. TDC-GPX在卫星激光测距中的应用[J]. 大地测量与地球动力学, 2011(1): 174-177 (Zhu Wei, Wang Peiyuan, Li Xin, et al. Application of TDC-GPX in Satellite Laser Ranging[J]. Journal of Geodesy and Geodynamics, 2011(S1): 174-177)

(  0) 0) |

| [2] |

李世鹏, 郭唐永, 杨厚丽. 三维激光扫描仪嵌入式控制系统设计[J]. 大地测量与地球动力学, 2016(2): 124-127 (Li Shipeng, Guo Tangyong, Yang Houli. Design of Embedded Control System for 3D Laser Scanner[J]. Journal of Geodesy and Geodynamics, 2016(S2): 124-127)

(  0) 0) |

| [3] |

张为民, 王晓兵, 叶文蔚, 等. 事件计时器在小型快速绝对重力仪中的应用[J]. 大地测量与地球动力学, 2012, 32(1): 149-151 (Zhang Weimin, Wang Xiaobing, Ye Wenwei, et al. Application of Event Timer in Small Fast Absolute Gravimeter[J]. Journal of Geodesy and Geodynamics, 2012, 32(1): 149-151)

(  0) 0) |

| [4] |

Kalisz J. Review of Methods for Time Interval Measurements with Picosecond Resolution[J]. Metrologis, 2004, 41: 17-32 DOI:10.1088/0026-1394/41/1/004

(  0) 0) |

| [5] |

潘维斌, 龚光华, 李荐民. 基于进位链的多通道时间数字转换器[J]. 清华大学学报:自然科学版, 2013, 53(10): 1391-1396 (Pan Weibin, Gong Guanghua, Li Jianmin. Carry Chain Based Multi-Channel Time-to-Digital Converter[J]. J Tsinghua Univ: Sci & Technol, 2013, 53(10): 1391-1396)

(  0) 0) |

| [6] |

安琪. 粒子物理实验中的精密时间间隔测量[J]. 核技术, 2006, 29(6): 453-462 (An Qi. Review of Methods and Techniques of Precise Time Interval Measurements for Particle Physics Experiments[J]. Nuclear Techniques, 2006, 29(6): 453-462 DOI:10.3321/j.issn:0253-3219.2006.06.011)

(  0) 0) |

| [7] |

冯国旭, 常保成. 高精度激光测距技术研究[J]. 激光与红外, 2007, 37(11): 1137-1140 (Feng Guoxu, Chang Baocheng. Study of High Precision Laser Ranging Technology[J]. Laser & Infrared, 2007, 37(11): 1137-1140 DOI:10.3969/j.issn.1001-5078.2007.11.003)

(  0) 0) |

| [8] |

陈弈, 郭颖, 杨俊, 等. 脉冲式高精度激光测距技术研究[J]. 红外, 2010, 31(06): 1-4 (Chen Yi, Guo Ying, Yang Jun, et al. Study of High-Precision Pulsed Laser Range Finding Techniques[J]. Infrared, 2010, 31(6): 1-4 DOI:10.3969/j.issn.1672-8785.2010.06.001)

(  0) 0) |

| [9] |

楮振勇, 翁木云. FPGA设计及应用[M]. 西安: 西安电子科技大学出版社, 2002 (Chu Zhenyong, Weng Muyun. FPGA's Design and Application[M]. Xi'an: Xidian University Press, 2002)

(  0) 0) |

| [10] |

吴继华, 蔡海宁, 王诚. Altera FPGA/CPLD设计(高级篇)[M]. 北京: 人民邮电出版社, 2011 (Wu Jihua, Cai Haining, Wang Cheng. Altera FPGA/CPLD Design (Advanced)[M]. Beijing: The People's Posts and Telecommunications Press, 2011)

(  0) 0) |

| [11] |

夏宇闻. Verilog数字系统设计教程[M]. 北京: 北京航空航天大学出版社, 2008 (Xia Yuwen. Verilog Digital System Design[M]. Beijing: Beihang University Press, 2008)

(  0) 0) |

| [12] |

徐志军, 徐光辉. CPLD/FPGA的开发与应用[M]. 北京: 电子工业出版社, 2002 (Xu Zhijun, Xu Guanghui. CPLD/FPGA's Development and Application[M]. Beijing: Publishing House of Electronics Industry, 2002)

(  0) 0) |

| [13] |

王金明, 杨吉斌. 数字系统设计与Verilog HDL[M]. 北京: 电子工业出版社, 2002 (Wang Jinming, Yang Jibin. Digital System Design and Verilog HDL[M]. Beijing: Publishing House of Electronics Industry, 2002)

(  0) 0) |

| [14] |

张亮. 数字电路设计与Verilog HDL[M]. 北京: 人民邮电出版社, 2000 (Zhang Liang. Digital Circuit Design and Verilog HDL[M]. Beijing: The People's Posts and Telecommunications Press, 2000)

(  0) 0) |

2. Wuhan Base of Institute of Crustal Dynamics, CEA, 40 Hongshance Road, Wuhan 430071, China

2017, Vol. 37

2017, Vol. 37