2. 中国科学院大学, 北京 100049;

3. 上海复旦微电子集团股份有限公司, 上海 200433

2. University of Chinese Academy of Sciences, Beijing 100049, China;

3. Shanghai Fudan Microelectronics Group Company Limited, Shanghai 200433, China

为了实现电路工作频率和功耗的性能优化,集成电路设计人员往往利用对晶体管阈值电压调节的技术[1-3]。

在电路应用中,一种常用的阈值电压调节技术是体偏技术。体硅CMOS(Complementary Metal Oxide Semiconductor)工艺的电路的P/N结阱偏置或衬底偏置和SOI(Silicon-On-Insulator)工艺的电路中的体接触都属于此类技术的范畴。这种技术的核心思想就是对单个晶体管的沟道电压产生直接的影响。另一种阈值电压调节技术则是超薄体超薄埋氧(Ultra Thin Body and Buried oxide,UTBB) FDSOI(Fully Depletion SOI)的背偏调节技术[4-6]。根据埋氧层(Buried Oxide,BOX)层下掺杂的类型不同,背偏调节可以分为2种:正向背偏(Forward Back Bias,FBB)调节和反向背偏(Reverse Back Bias,RBB)调节。晶体管级的测试显示UTBB FDSOI对阈值电压Vth和跨导Gm的调节能力比体硅FinFET(Fin Field-Effect Transistor)的调节能力要高2个数量级[7]。借助于背偏技术,可以设计并优化低功耗、高性能的FDSOI CMOS集成电路,达到低功耗和高性能的需求[8-12]。

本文为了比较UTBB FDSOI CMOS背偏及体硅CMOS体偏的偏置调节能力,基于相同的电路结构,比较和分析了2种典型的工艺制程(28 nm体硅CMOS和22 nm FDSOI)的功耗和电路特性的后仿真结果。

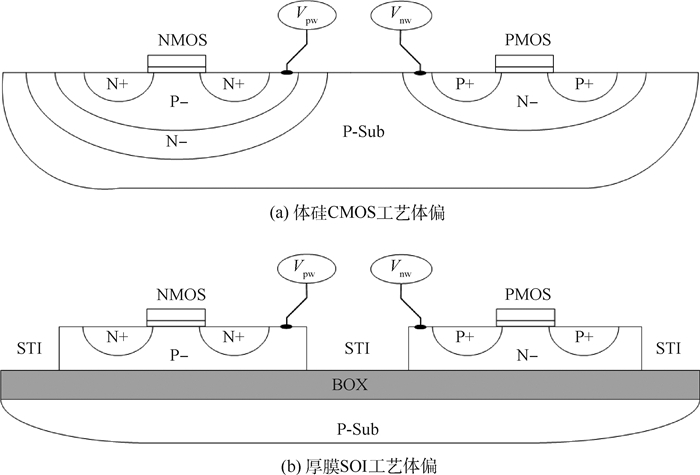

1 电路结构 1.1 工艺简介体硅CMOS工艺如图 1(a)所示,厚膜SOI工艺如图 1(b)所示, Vpw为对P阱施加的电压,Vnw为对N阱施加的电压。

|

| 图 1 体硅CMOS和厚膜SOI工艺的体偏 Fig. 1 Body bias in bulk CMOS and thick SOI |

图 2(a)展示的是FBB调节,图 2(b)展示的是RBB调节,Vpbb为对P阱施加的背偏电压,Vnbb为对N阱施加的背偏电压。

|

| 图 2 UTBB FDSOI的FBB和RBB背偏 Fig. 2 Back bias in UTBB FDSOI FBB and RBB |

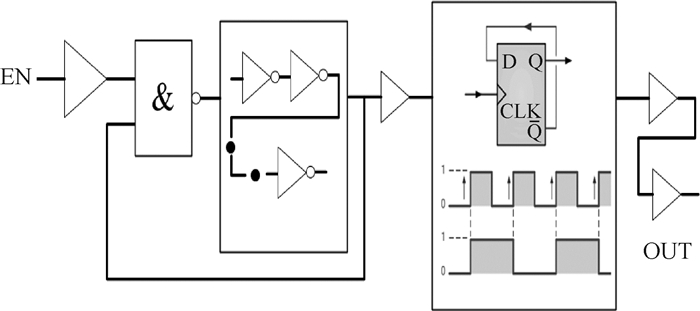

如图 3所示,基于28 nm体硅CMOS工艺和22 nm FDSOI工艺分别设计了带有使能端和4级分频器的65级环阵(RO),其中EN为使能端,OUT为环阵的输出。为了尽可能公平地比较上述2种工艺制程,所有晶体管的沟长均设为30 nm。环阵的基本延时单元是最小尺寸的反相器,PMOS管和NMOS管的沟宽分别为220 nm和160 nm。分频器为4级,在每一级上具有一个自反馈D触发器(D type Flip-Flop,DFF)。因此最终的输出频率为环阵内核频率的1/16。

|

| 图 3 环阵电路结构 Fig. 3 RO circuit structure |

环阵电路规模适中,包含N管和P管,同时涵盖了组合逻辑和时序逻辑,因此选取环阵电路作为验证电路。环阵电路是频率综合器、锁相环(Phase Locked Loop,PLL)等时钟电路的核心组成部分之一,分频器中的寄存器是时序逻辑的基础模块,因此以分频和环阵组成的实例极具代表性。

注意到电路中的所有晶体管均为体偏或者背偏,包括使能的与非门、环阵内核、分频器和输出缓冲器。因此意味着偏压将同时影响所有的模块。

1.3 环阵分析环阵是N(奇数)个反相器首尾相连构成的环状链。设一级反相器的延时为τd,则高电平信号经过Nτd的延时变成低电平,再经过Nτd的延时变回高电平。因此环阵的频率可表示为

|

(1) |

反相器的延时τd定义为输入输出波形的50%翻转点之间的时间。可将MOS管在充放电过程中看做一个非时变的线性电阻REQ,而后通过一阶RC(Resistor-Capacitance)网络计算延时τd[13]。MOS管的等效电阻可表示为

|

(2) |

式中:L为沟道长度(Lp=Ln=L);W为沟道宽度(Wp=kWn=kW);K为工艺参数(Kn, Kp);Vsat为速度饱和电压(Vsatn, Vsatp);λ为沟长调制系数(λn, λp); VDD为电源电压。

负载电容CL可表示为

|

(3) |

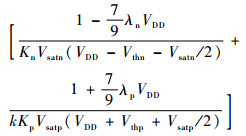

式中:cox为栅氧的单位面积电容。则传播延时τd=0.69CL(Reqn+Reqp)/2(Reqn和Reqp分别为NMOS管和PMOS管的等效电阻)可表示为[14]

|

(4) |

因此,反相器延时τd与器件沟道宽度W无关,与电源电压VDD和器件的其他工艺参数相关[15]。

由式(4)可知,1/τd与阈值电压Vth成近似线性关系;而阈值电压又受到背偏和体偏的影响。因此可以通过仿真得到背偏-环阵频率的变化图和体偏-环阵频率的变化图。

1.4 仿真设置电路设计、版图参数提取和后仿真都在标准的工作环境中进行。使用Cadence ICADV12.20.700进行原理图和版图设计,使用Calibre2016.4_15.11进行DRC/LVS/LPE等流程,使用Hspice 2016.03_1进行后仿真。

工艺角模型为典型的N和典型的P。为了避免核电压的不同,内核电压设为0.8 V。温度为室温25℃,偏压从-2 V扫到+2 V,步进为0.4 V。在仿真过程的全过程中记录或计算输出频率(Freq)、静态电流(Iddsb)、背偏和体偏电流(Inbb, Ipbb)。22 nm FDSOI工艺环阵的仿真时间是28 nm体硅CMOS工艺环阵仿真时间的4倍。

2 后仿真结果与分析为了得到不同工艺的偏置效果,本节对仿真结果进行比较。

2.1 偏压的调节范围在28 nm体硅CMOS工艺中,体偏应用于阱区。如图 1所示,在阱区和源/漏之间存在PN结,因此Vpw应该小于0 V,Vnw应该大于0 V。后仿真也遵守上述限制。如图 4所示,如果Vpw>0 V或者Vnw < 0 V,该工艺环阵没有功能。静态电流Iddsb和工作电流Iddop也比正常的范围大。实际上,仿真表明Vpw可以比0 V略大。因此,对于该工艺环阵,为了确保功能,Vnw设置为0~2V,Vpw设置为-2~0.4 V,步长为0.4 V。

|

| 图 4 28 nm体硅CMOS工艺环阵体偏电压对输出频率的影响 Fig. 4 Output frequency response to body bias voltage of 28 nm bulk CMOS RO |

在22 nm FDSOI工艺中,背偏电压可以从-2 V扫到+2 V。环阵工作状态良好,输出频率随着偏压改变,并且电流在正常范围内变化。Vnbb和Vpbb均在-2~+2 V变化,步长为0.4 V。

2.2 输出频率在28 nm体硅CMOS工艺环阵中,非体偏电路的工作条件是Vpw=0 V且Vnw=+0.8 V,输出频率为120 MHz。体偏的情况下,Vpw=-2 V且Vnw=+2 V时频率是92.8 MHz,为后仿真范围内的最小频率,频率降低了23%;在Vpw=+0.4 V且Vnw=+0.4 V时最大频率是127 MHz,为后仿真范围内的最大频率,频率提升了5.8%。图 4展示出了输出频率的整体变化情况,注意到在偏压超出功能范围时没有输出频率。

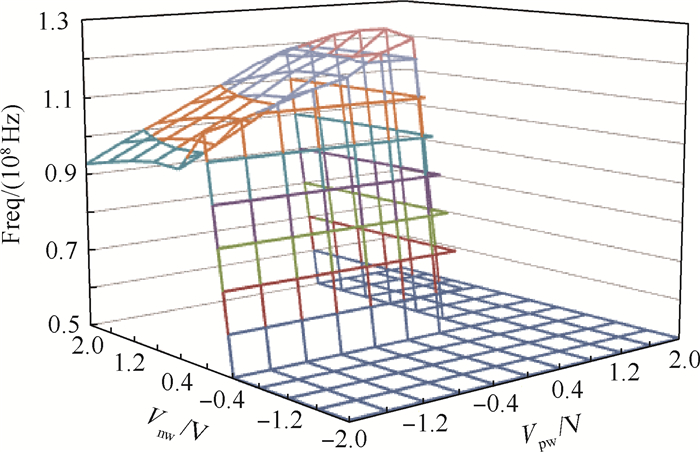

在22 nm FDSOI环阵中,非背偏的工作条件是Vpbb=0 V且Vnbb=0 V,输出频率Ferq为158 MHz。背偏的情况下,Vnbb=-0.4 V且Vpbb=+1.2 V时频率为57.8 MHz,是后仿真范围内的最小频率,频率降低了63%;在Vnbb=+0.4 V且Vpbb=+0.4 V时频率为206 MHz,是后仿真范围内的最大频率,频率提升了30%。图 5展示出了输出频率的整体变化情况,注意到Vnbb对性能有更大的影响。具体对比结果如表 1所示。

|

| 图 5 22 nm FDSOI工艺环阵背偏电压对输出频率的影响 Fig. 5 Output frequency response to back bias voltage of 22 nm FDSOI RO |

| MHz | |||

| 工艺环阵 | 最小值 | 正常值 | 最大值 |

| 28nm体硅CMOS | 92.8 | 120 | 127 |

| 22nm FDSOI | 57.8 | 158 | 206 |

2.3 静态电流

设置EN信号为0 V,环阵将功能关断。这时可以得到静态电流。

对于28 nm体硅CMOS工艺环阵,非体偏的静态电流Iddsb=2.34×10-7 A。在体偏的情况下,Vpw=-2 V且Vnw=+2 V时Iddsb=1.70×10-8 A,是后仿真范围内的最小电流,电流降低了93%;在Vpw=+0.4 V且Vnw=0 V时静态电流为1.26×10-6 A,是后仿真范围内的最大电流,增加了5.4倍。

对于22 nm FDSOI工艺环阵,非背偏的静态电流Iddsb为2.99×10-9 A。在背偏的情况下,最小静态电流为1.33×10-9 A,电流降低了56%;最大静态电流为5.34×10-9 A,增加了2倍。具体对比结果如表 2所示。

| A | |||

| 工艺环阵 | 最小值 | 正常值 | 最大值 |

| 28 nm体硅CMOS | 1.70×10-8 | 2.34×10-7 | 1.26×10-6 |

| 22 nm FDSOI | 1.33×10-9 | 2.99×10-9 | 5.34×10-9 |

2.4 工作电流

对于28 nm体硅CMOS工艺的环阵,非体偏的工作电流Iddop为1.01×10-4 A。在体偏的情况下,最小工作频率下的工作电流Iddop为6.78×10-5 A,电流降低了33%;最大工作频率下的工作电流Iddop为1.29×10-4 A,增加了28%。图 6展示出了工作电流Iddop整体变化情况,注意到这个统计没有计算超出工作范围的工作电流。

|

| 图 6 28 nm体硅CMOS工艺环阵体偏电压对工作电流的影响 Fig. 6 Operating current response to body bias voltage of 28 nm bulk CMOS RO |

对于22 nm FDSOI工艺的环阵,非背偏的工作电流Iddop为7.03×10-5 A。在背偏的情况下,最小工作频率下的工作电流Iddop为2.44×10-5 A,电流降低了65%;最大工作频率下的工作电流Iddop为9.04×10-5 A,增加了29%。图 7展示出了在不同背偏情况下工作电流Iddop整体变化情况。具体对比结果如表 3所示。

|

| 图 7 22 nm FDSOI工艺环阵背偏电压对工作电流的影响 Fig. 7 Operating current response to back bias voltage of 22 nm FDSOI RO |

| A | |||

| 工艺环阵 | 最小值 | 正常值 | 最大值 |

| 28nm体硅CMOS | 6.78×10-5 | 1.01×10-4 | 1.29×10-4 |

| 22nm FDSOI | 2.44×10-5 | 7.03×10-5 | 9.04×10-5 |

3 测试芯片实验结果与分析

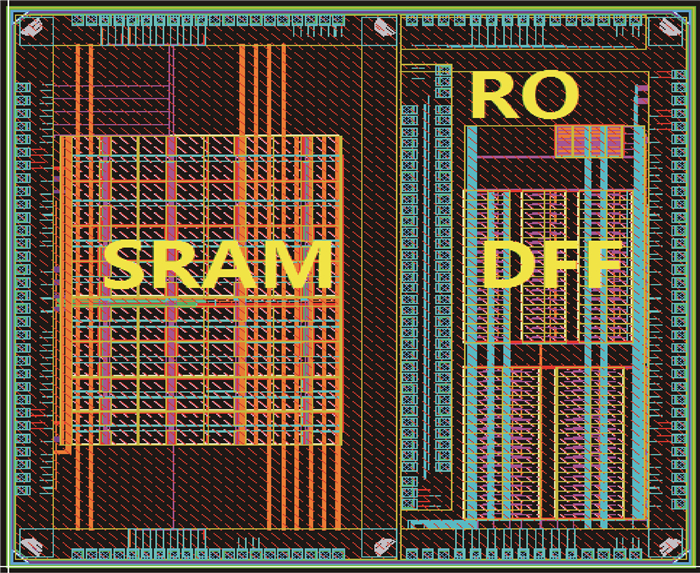

针对22 nm FDSOI工艺进行了流片验证。如图 8所示,测试芯片包括1 Mbit的SRAM,8个8 Kbit的DFF链和4个环阵,整体面积为3 mm× 3 mm。GPIO库和标准单元库由Invecas提供。

|

| 图 8 22 nm FDSOI测试芯片版图 Fig. 8 22 nm FDSOI test chip layout |

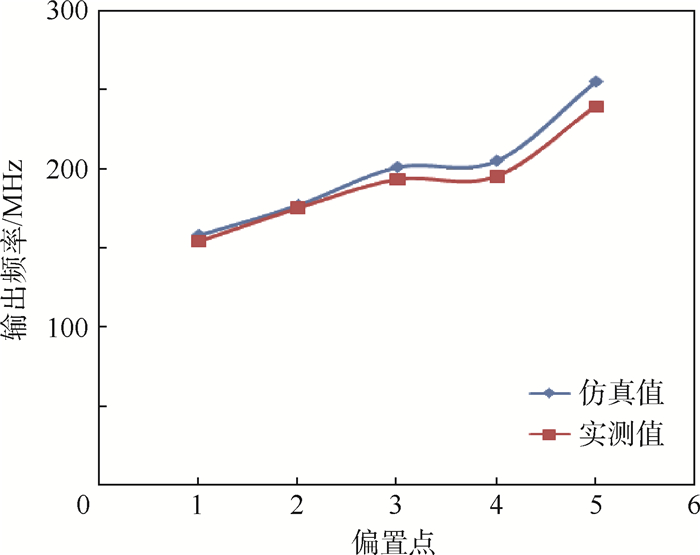

对流片后22 nm FDSOI工艺环阵进行了ATE测试,ATE设备为J750EX-1测试台。测试了三片环阵,环阵的平均输出频率如表 4所示,并针对仿真值和实测值进行了对比。图 9给出了输出频率仿真和测试的对比图。

| 背偏电压/V | 输出频率/MHz | |

| 仿真值 | 实测值 | |

| (0, 0) | 158 | 154 |

| (+1, 0) | 177 | 175 |

| (+1, -1) | 201 | 193 |

| (+2, 0) | 205 | 195 |

| (+2, -2) | 255 | 239 |

|

| 图 9 22 nm FDSOI工艺环阵输出频率仿真和实测对比 Fig. 9 Comparison of output frequency of 22 nm FDSOI RO between simulation and test |

实测结果表明,环阵的输出频率实测比仿真频率慢,变化的范围为1.1%~6.5%;背偏越大,差异也越大。背偏的影响效果,仿真和实测呈现相近的变化规律。综上,背偏对频率的影响,仿真能比较好地反映实测结果,具有较好的参考价值,但模型的准确性仍需改进。

4 结论本文对体硅CMOS工艺的体偏和FDSOI工艺的背偏进行了分析和比较。由于不同阱区掺杂的存在,在体硅CMOS工艺中存在体偏电压的安全范围。2种工艺测试电路的偏置效应在2个方面进行比较:功耗和电路性能。以带有4级分频器的65级环阵为例,后仿真结果表明:对于FDSOI工艺的环阵,与非背偏的工作状态进行对比,背偏可以使输出频率从-63%调整到30%,同时对应的工作电流可以从-65%变化到29%;但是对于体硅工艺的环阵,输出频率仅可从-23%调整到5.8%,同时对应的工作电流仅可以从-33%变化到28%。对于FDSOI工艺的环阵,实测结果和仿真结果呈现相近的变化规律,仿真结果和实测结果的差异在可接受的范围,仿真结果具有较好的参考价值。因此,在功耗和性能2个方面,FDSOI工艺电路背偏的动态调节范围比体硅CMOS工艺电路体偏的动态调节范围要大的多。

在需要速度快的部分电路,可以加正偏置,在需要功耗低的部分电路,可以加负偏置,这样可以使整体电路得到优化。基于上述结论,可以借助于背偏技术,设计并优化低功耗、高性能的FDSOI CMOS集成电路,以满足未来对低功耗和高性能的需求。

致谢 感谢中国科学院微电子研究所的副研究员李彬鸿和赵星博士对于本文框架的支持。感谢上海复旦微电子集团股份有限公司的雷蕾,Invecas公司的Vivek和GlobalFoundries公司的Louisa、Wesley在测试芯片制造过程中的帮助。

| [1] |

SUN P P, WANG G A, WOODS W, et al.An adaptive body-bias low voltage low power LC VCO[C]//Proceedings of 2010 IEEE International Symposium on Circuits and Systems (ISCAS).Piscataway, IEEE Press, 2010: 1121-1124. An adaptive body-bias low voltage low power LC VCO

|

| [2] |

HART M J, YOUNG S P, GITLIN D, et al.Structures and methods for selectively applying a well bias to portions of a programmable device: US2003/0053335A1[P].2003-03-27.

|

| [3] |

NABAA G, NAJM F, AZIZI N.FPGA architecture with threshold voltage compensation and reduced leakage: US2008/0180129A1[P].2008-07-31.

|

| [4] |

NEDELCU S, HAUER J, KLEIN L, et al.Dynamic body bias for 22 nm FD-SOI Technology[C]//Proceedings of Analog 2016 IET/GMM-Symposium.Berlin: VDE-Verlag, 2016: 44-48. https://www.vde-verlag.de/proceedings-en/454265007.html

|

| [5] |

DE STREEL G, BOL D.Impact of back gate biasing schemes on energy and robustness of ULV logic in 28 nm UTBB FDSOI technology[C]//IEEE International Symposium on Low Power Electronics and Design (ISLPED).Piscataway, NJ: IEEE Press, 2013: 255-260. https://www.researchgate.net/publication/261283584_Impact_of_back_gate_biasing_schemes_on_energy_and_robustness_of_ULV_logic_in_28nm_UTBB_FDSOI_technology

|

| [6] |

BERNARD S, BELLEVILLE M, VALENTIAN A, et al.Experimental analysis of flip-flops minimum operating voltage in 28 nm FDSOI and the impact of back bias and temperature[C]//2014 24th International Workshop on Power and Timing Modeling, Optimization and Simulation (PATMOS).Piscataway, NJ: IEEE Press, 2014, 5596: 1-7. https://www.researchgate.net/publication/286738046_Experimental_analysis_of_flip-flops_minimum_operating_voltage_in_28nm_FDSOI_and_the_impact_of_back_bias_and_temperature

|

| [7] |

CHANG W T, LIN S W, SHIH C T, et al.Back bias modulation of UTBB FDSOI, bulk FinFET, and SOI FinFET[C]//2016 IEEE International Nanoelectronics Conference (INEC).Piscataway, NJ: IEEE Press, 2016: 1-2. https://ieeexplore.ieee.org/document/7589260

|

| [8] |

SKOTNICHI T.Competitive SOC with UTBB SOI[C]//2011 IEEE International SOI Conference.Piscataway, NJ: IEEE Press, 2011: 1-61. https://www.infona.pl/resource/bwmeta1.element.ieee-art-000006081792

|

| [9] |

CHRIRAT S, BEIGNE E, BERTHIER F, et al.Ultra low energy FDSOI asynchronous reconfiguration network for an IoT wireless sensor network node[C]//IEEE S3S Microelectronics Technology Unified Conference.Piscataway, NJ: IEEE Press, 2016: 1-3. https://www.mdpi.com/2079-9268/7/2/11

|

| [10] |

RASHED M.22FDX FDSOI application towards IOT for smart devices[C]//2017 30th International Conference on VLSI Design and 2017 16th International Conference on Embedded Systems (VLSID).Piscataway, NJ: IEEE Press, 2017.

|

| [11] |

CHEN L, LOMBARDI F, HAN J.FDSOI SRAM cell for low power design at 22 nm technology node[C]//IEEE International Midwest Symposium on Circuits & Systems, College Station. Piscataway, NJ: IEEE Press, 2014: 527-530. http://www.ece.ualberta.ca/~jhan8/publications/FDSOISRAM_MWCAS2014.pdf

|

| [12] |

SAKURAI T, MATTSUZAWA A, DOUSEKI T. Fully-depleted SOI CMOS circuits and technology for ultra-low power applications[M]. Berlin: Springer, 2006: 108-113.

|

| [13] |

RABARY J M, ANANTHA C, BORIVOJE N. 数字集成电路——电路、系统与设计[M]. 北京: 电子工业出版社, 2012: 140-146. RABARY J M, ANANTHA C, BORIVOJE N. Digital integrated circuit-Circuits, systems and designs[M]. Beijing: Publishing House of Electronics Industry, 2012: 140-146. (in Chinese) |

| [14] |

黄如, 张国艳, 李映雪, 等. SOI CMOS技术及其应用[M]. 北京: 科学出版社, 2005: 168-172. HUANG R, ZHANG G Y, LI Y X, et al. SOI CMOS technology and its application[M]. Beijing: Science Press, 2005: 168-172. (in Chinese) |

| [15] |

GAO C, ZHAO X, ZHAO K, et al. DSOI-A novel structure enabling adjust circuit dynamically[J]. Journal of Semiconductor, 2016, 37(6): 065003. DOI:10.1088/1674-4926/37/6/065003 |